Изобретение относится к измерительной технике и может быть использовано при измерении незлектрических величин с применением тензорезис торов. Известен цифровой измерительный неуравновешенный мост, содержащий; мостовую схему, одно плечо которого образовано измерительным резистором, например тензорезистором, усилитель разбаланса, включенный в измерительную диагональ, соединенные последовательно интегратор и усилитель-огра ничитель, задатчик временных интервалов, соединенный с выходом усилителя-ограничителя, с измерителем временных интервалов и с управляющим входами двух ключей l. Недостатком этого устройства явля ется нелинейность зависимости выходного кода от рабочего приргидения сопротивления тензорезистора. Известен также цифровой измерительный неуравновешенный мост, содер жащий мостовую схему, одно плечо которой образовано измерительным резис тором, усилитель разбаланса, подключенный к измерительной диагонали,источник тока, изменяющий свою полярность , один выход которого соединен одной вершиной диагонали питания, интегратор, вход которого соединен с выходом усилителя разбаланса,усилитель-ограничитель, вход которого сое-динен с выходом интегратора, а выход подключен к управляющему входу источника тока, датчик временных интервалов , соединенный с выходом усилителяограничителя , с измерителем времеиных интервалов и с управляю1цими входами двух ключей 21. Устройство имеет следующие недостатки:для жесткой функциональной связи кода с измеряемым приращением сопротивления необходимо либо использовать образцовый резистор,либо производить предварительное измерение его сопротивлeнияJне обеспечивает непосредственное измерение относительного изменения сопротивления измерительного резистора; в составе измерителя временных инtepBanoB необходимо иметь высокоточный генератор опорной частоты, импульсами которой заполняется измеряемый временный интервал, т.к. точность установки опорной частоты опрееляет точность измерения устройстом;

необхолимость использования исочника тока в качестве источника итания мостовой схемы приводит к сложнению последнего.

Цель изобретения - повышение точ- 5 ости измерения относительного прираения сопротивления измерительного, езистора.

Указанная цель достигается тем, что цифровой измерительный неуравно- |в вешенный мост, содержащий мостовую схему, одно плечо которой образовано измерительным резистором, например тензорезистором, источник питания , один выход которого подключен е к одной вершине диагонгили питания, усилитель разбаланса, один вход ко- торого подключен к первой вершине измерительной диагонали, соединенной с общей точкой постоянных резисторов мостовой схемы, последовательно сое- диненные интегратор и усилитель-ограничитель , выход которого соединен с управляющим входом источника питания, два ключа, датчик временных интервалов, соединенный с выходом уси- 25 лителя-ограничителя и управляющими входами ключей, измеритель временных интервалов, содержащий генератор импульсов и последовательно соединенные схему И и счетчик, управляющие JQ входы которых соединены с датчиком временных интервалов, снабжен делителем напряжения, образованным тремя последовательно соединенными резисторами, подключенными к вершинам диаго- 35 нал и питания и имекяцими два выхода в точках соединения двух смежных резисторов, цифро-ансшоговым преобразователем, вход которого соединен с выходом усилителя разбаланса, а выход подключен к входу интегратора, реги- стром, выходы которого подключены к управляющим входам цифро-аналогового преобразователя, третьим ключом, блоком цифровой памяти, входы которого подключены к выходс1м счетчика, а вы- 45 ходы соединены с входами регистра и счетчика, при этом второй вход усилителя разбаланса через ключи соединен, соответственно, со второй вершиной измерительной диагонали и выхо- 50 дами делителя напряжения, источник питания выполнен в виде источника напряжения, другой выход которого подключен к другой вершине диагонали питания и к датчику временных интер- jj валов, выход схемы И соединен с. входом счетчика через делитель частоты, управляющие.входы которого соединены с датчиком временных интервалов,уп- : равляющие входы регистра и блока цифровой памяти подключены к датчику временных интервалов.

Датчик временных интервгшов содержит формирователь строба, второй и третий счетчики, входа которых соединены между собой и связаны че- 65

рез схему И-ИЛИ с генератором импульсов, четвертый счетчик, два выхода которого подключены к управляющим входам второго и третьего счетчиков, а вход через схему ИЛИ соединен с выходами второго и третьего счетчиков и выходом формирователя стооба.тоиггер, D-вход которого соединен с одни из входов схемы исключающее ИЛИ и чрез схему согласования с входной шиной датчика временных интервалов, подключенной к выходу усилителяограничителя, а выход соединен с другим входом схемы исключающее ИЛИ, а С-вход подключен к входу четвертого счетчика, логический блок,входы которого подключены к выходам четвертого счетчика, к выходу схемы исключающее ИЛИ, к выходу задатчика режимов работы и к входной шине датчика временных интервалов, соединенной с источником питания,при этом выходы логического блока соединены с выходными шинами датчика временных интервалов, один управляющий вход схемы И-ИЛИ соединен с выходом формирователя строба,а второй вход с выходом схемы исключающее ИЛИ.

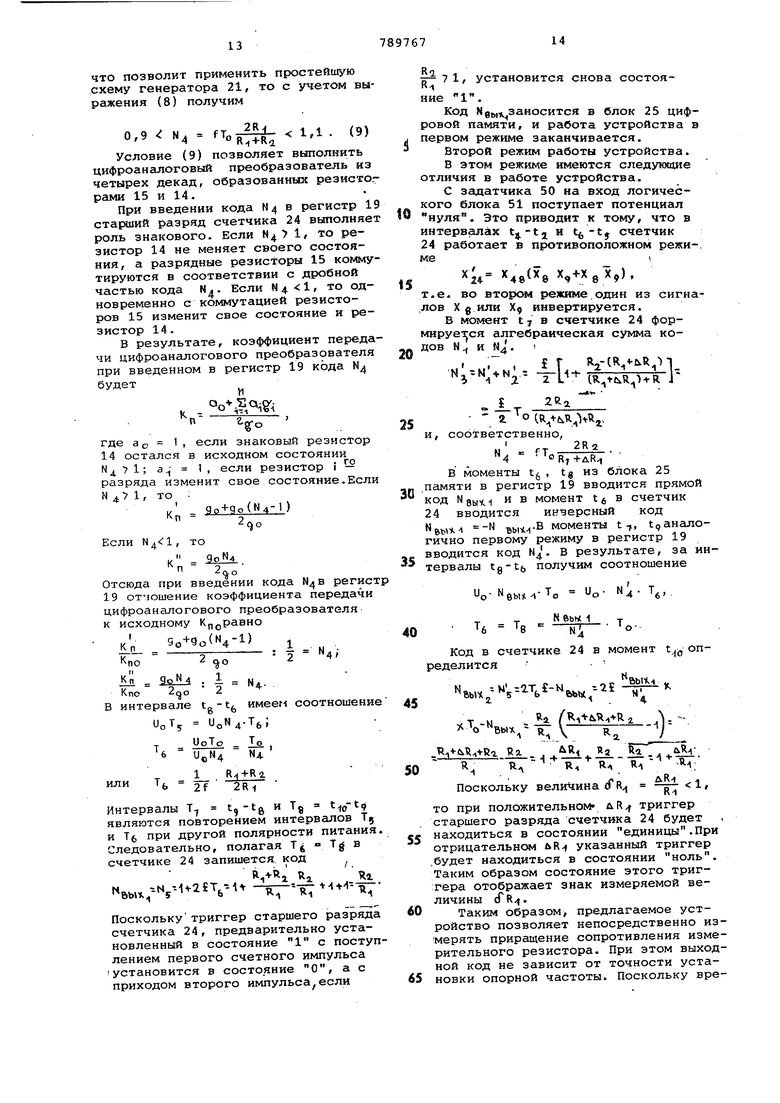

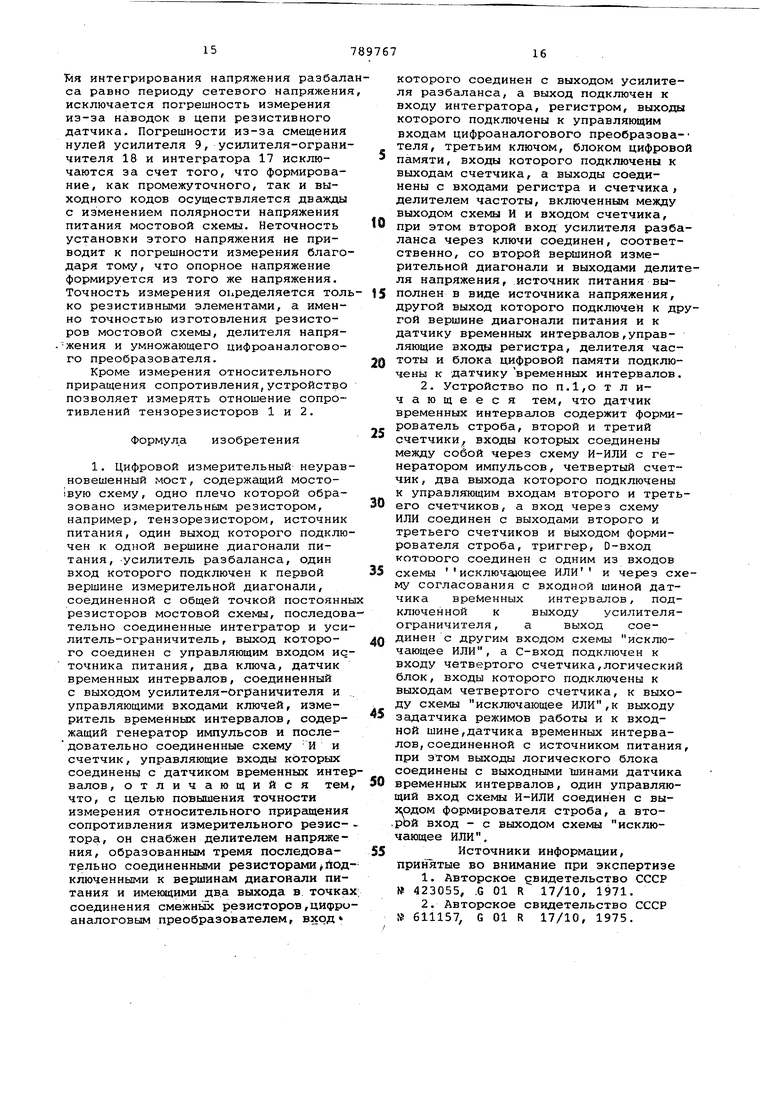

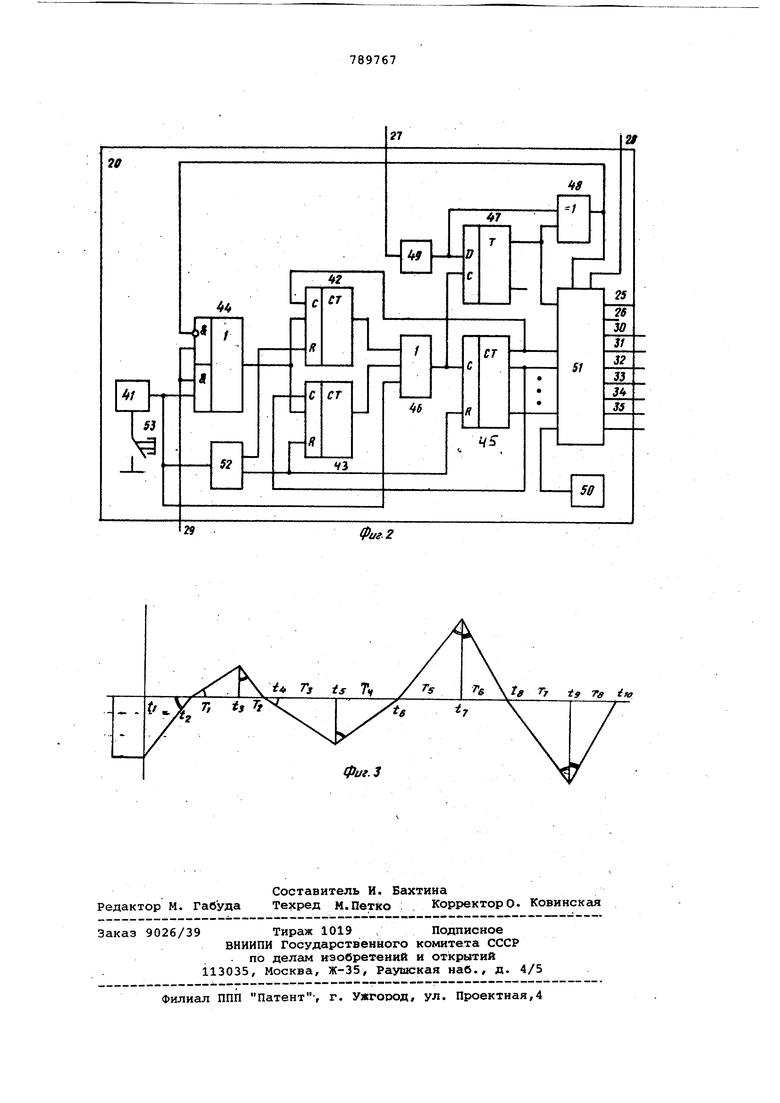

На фиг. 1 изображен цифровой измерительный неуравновешенный мост; на фиг. 2 - датчик временных интервалов; на фиг. 3 - временная диаграмма выходного напряжения интегратора. Цифровой измерительный неуравновешенный мост содержит мостовую схему, состоящую из активного тензорезистора 1, компенсационного тензорезистора 2, образцовых резисторов 3 и 4, делителя напряжения, образованного резисторами 5, 6 .и 7, источника 8 питания, включенного в одну диагональ мостовой схемы, усилителя 9 разбаланса, один вход которого соединен с общей точкой резисторов 3 и 4, а другой вход через ключи 10, 11 и 1 соединен,соответственно, с общей точкой тензорезисторов 1 и 2, с общей точкой резисторов 5 и б и с общей точкой резисторов 6 и 7. Последовательно соединенные цифро-аналоговый преобразователь 13, состоящий из разрядных резисторов 14, 15 и разрядных переключателей- 16, интегратор 17, усилитель-ограничитель 18, регистр 19, выходы которого соединены р управляющими входами переключате 1ей 16, измеритель 20 временных интервалов , состоящий из последовательного соединения генератора 21 импульсов, схемы 22 И, делителя 23 час;тоты и реверсивного двоично-десятичного счетчика 24, блок 25 цифровой ;памяти, входы которого подключены :к выходам десятичного счетчика 24, а выходы соединены с входами регистра 19 и счетчика 24, датчик 26 временных интервалов, входные шины 27, |28 и 29 которого соединены, соответственно, с .выходом усилителя-ограничителя 13, с одной вершиной диагонали питания мостовой схемы, и выходом генератора 21, а выходные шины 30-40 соединены с управляющими входами ключей 10, 11, 12, регистра 19 схемы 22 И, делителя 23 частоты, счетчика 24 и блока 25 цифровой пам Датчик 26 временных интервалов содержит формирователь 41 строба, связанный с сетью промьшшенного напряжения, реверсивные счетчики 4,2 и 43, входы которых соединены между собой и через схему 44 И-ИЛИ связаны с входной шиной 29, счетчик 45,счет ный вход которого через схему 46 ИЛИ соединен с выходами счетчиков 42, 43 и формирователя 41, триггер 47, D-вход которого соединен с одни входом схемы 48 исключающее ИЛИ и через схему 49 согласования - с входной шиной 27. Выход триггера 47 соединен с другим входом схемы 48, а счетный вход подключен к выходу схемы 46. Выходы счетчика 45, задат чика 50 режимов работы, схемы 48 подключены к входам логического бло ка 51. Два выхода счетчика 45 соеди нены с управляющими входами счетчиков 42 и 43, установочные входы сче чиков 42, 43 и 45 через формирователь 52 коротких импульсов связаны выходом формирователя 41.Управляющи входы схемы 44 соединены, соответственно, с выходом схемы 48 и форми рователя 41, к управляющему входу к торого подключена кнопка 53 пуска. Входная шина 28 соединена с одним и входов логического блока 51, выходы которого подключены к выходным шинам 30-40. Устройство имеет два режима рабо ты, устанавливаемые задатчиком 50. Первый режим осуществляется при ненагруженном тензорезисторе 1, т.е. при отсутствии деформации. В этом режиме алгоритм аналого-цифрового преобразования организуется так,что выходной код отображаетвеличину ВЫ R1 исходное сопротивление активного тензорезистора 1; 2 сопр тивление компенсационного тензорезистора 2. Во втором режиме тензорезистор имеет рабочее приращение сопротивле ний. В этом режиме выходной код ото ражает величину Ra. .U R 9. где лК - рабочее приращение сопротивления тензорезистора 1. В каждом ражиме работы устройство имеет два этапа аналого-цифрового преобразования.При этом на первом этапе формируются промежуточные код 2.Ял К -V i где Ь и Ь - коэффициенты; промежуточный код в первом режиме работы; . - промежуточный код во втором режиме работы. Счетчик 24 имеет старший разряд, отображающий целую часть формируемого кода, и состоящий из одного триггера, и несколько двоично-десятичных декад, отображсоощих дробную часть кода. Выбор числа таких декад зависит от Зсщанной точности измерения. Поскольку в тензометрии обычно , единицей дискретности является относительных единиц деформации, то в этом случае необходимо иметь пять декад. При этом сформированный код будет представлять собой десятичное число с пятью знаками после запятой. Устройство реализует аналого:цифровое преобразование по методу двухтактного интегрирования, заключающееся в том, что сначала на вход интегратора 17 подают напряжение разбаланса мостовой схемы, усиленное усилителем 9, которое интегрируется за интервал времени, равный периоду сетевого напряжения 1 t - t 5 (фиг.З). Затем на вход интегра,тора 17 подается опорное напряжение,также усиленное усилителем 9, противоположной полярности. Интервал времени от момента t-, до момента t, когда выходное напряжение интегратора 17 станет равным нулю, пропорционален отношению напряжения разбаланса и опорного напряжения. U Т K-UO-TJ , где их - напряжение разбаланса; Uo опорное напряжение, К - результирующий коэффициент передач усилителя 9, -цифро-аналогового преобразовате- . ля 13 и интегратора 17. Напряжение разбаланса выразим через элементы мостовой схемы. Uy ил где Ug - нгшряжение источника 8 питания/ Rj - сопротивление резистора 3; R4 - сопротивление резистора 4. При R , R4 получаем (-|) Rg - RI 8 2() Опорное напряжение Uo формируется вспомогательным мостом, образованным резисторами 3, 4 и резисторами 5, б и 7. При этом ключ 10 разомкнут, а один из ключей 11 и 12 замкнут. Выбор ключа 11 или ключа 12 определяет, только знак Uo, а абсолютная

величина его одинакова в обоих случаях. Это обеспечивается равенством

(1)

R,

г. п,

где R f - сопротивление резистора 5, R 1 - сопротивление резистора 7. При замкнутом ключе 11 имеем

о я ( 1ч

, 2 а при замкнутом ключе 12

-i.

и. (

8 Rj+Rfc+R ii . II R7- R5+Rfe

UQ - Ug

2()

II 11 « .b 8 2(Rj )

Учитывая условие (1), получаем

Rfe

и

8 2(Rg+R6 + R)

6

и ® 2(R +R +R,)

Таким образом, опорные напряжения и о и DO равны по абсолютной величине и противоположны по знаку.

Если ввести обозначение

1 т

R6

2(,)

то для.опорного напряжения рн ние будет

|и,

m

Делитель 23 частоты, в зависимости от потенциалов на выходных шинах 35 и 36 датчика 26 временных интервалов, имеет три коэффициента деления

V-l

Si Ь

К

Для упрощения делителя частоты величина m кратна есть

m . 2,

где Р - целое число.

Величину Р в свою очередь выбирают,

исходя из того, чтобы

- и,„,

и,

где максимальное напряжение разбаланса мостовой схемы. Для обеспечения высокой разрешающей способности устройства необходимо, чтобы и о и и были как можно ближе друг к другу.

Разрядные резисторы 15 цифро-аналогового преобразователя образуют собой разряды двоично-десятичных декгщ.

Проводимость каждого из резистора 15 соответствует весовому значению соответствующего двоично-десятичного разряда. Проводимость резистора 14 равна суммарной проводимости резисторов 15.

и

(2)

S д.

9 ° i-.-f 1

где д - проводимость резистора 15 -го разряда.

В исходном состоянии, когда регистр 19 установлен в нулевое состояние, резистор 14 подключен к входной шине цифро-аналогового преобразователя, соединенной с выходом усилителя 9, а резисторы 15 подключены к нулевой шине (корпусу). При этом коэффициент передачи цифро-аналогового преобразователя составляет

по 9

с учетом соотношения (2)

К

по

Устройство работает следующим образом.

Первый режим работы устройства.

5 С выхода задатчика 50 на вход логического блока 51 поступает потенциал логической единицы.Устройство запускается нажатием кнопки 53.Формирователь 41 вырабатывает единичный строб, фронты.которого совпадают с моментами двух ближайших переходов сетевого напряжения из одной полярности (положительной) в другую (отрицательную), т.е. длительность строба, равна периоду сетевого напряжения. Во время действия строба

схема 44 открыта, и импульсы генератора 21 поступают на входы счетчиков 42 и 43. По переднему фронту строба формирователь 52 вырабатывает

0 на первом выходе короткий импульс, устанавливающий счетчики 43 и 45 в улевое состояние. На выходной шине 30 появится потенциал единицы и ключ 10 замкнется. Выходы первого

J разряда счетчика 45 установят счетчик 43 в режим сложения, а счетчики 42 - в режим вычитания. По окончанию действия строба, в момент t (фиг.3),в счетчике 43 зафиксируется код

NO - TO,

где f - частота генератора 21; Т длительность периода сетевого напря 5 жения. Знак выходного напряжения интегра тора определяется знаком напряжения разбаланса. В момент ty : 1.Счетчик 42 устанавливается в ноль формирователем 52, на втором выходе которого выбрасывается импульс сброса по Зсщнему фронту строба. Одновременно задний фронт строба через схему 46 воздействует на счетные входы счетчика 45 и триг гера 47. 2.На выходе триггера 47 установится потенциал логически равный по тенциалу, поступающему с выхода схе мы 49, который определяется состоянием усилителя-ограничителя 18. 3.Поскольку на обоих входах схемы 48 будут одинаковые потенциалы (два нуля или две единицы), то на выходе ее появится логическая единица, поступающая на инвертирующий управляющий вход схемы 44, которая теперь будет закрыта по обоим управляющим входам. 4.Под действием логической единицы на выходе схемы 48 логический блок 51 вырабатывает на одной из выходных шин 31 и 32 потенциал единицы , открывающий один из ключей 11 или 12. Логика выбора ключа, с учетом обозначения прямого и инверсного входов усилителя 9, определяется уравнением 48 В Х 1, если замкнут ключ ll, 1, если замкнут ключ 12; 1, если на выходе схемы 48 присутствует сигнал единицы ; Xg 1, есл полюс источника 8 питания, подключен ный к датчику 26 временных интервалов , положителен; X q - 1, если выход ное напряжение усилителя 9 положительно. В результате, в момент t ,а также впредь в моменты t- , tg , t-, , t происходит формирование опорного напряжения DO, полярность которого противоположна полярности напряжения разбаланса Уц. В интервале выходное напряжение интегратора 17 будет уменьшаться по абсолютной величине до нуля. В момент t2 происходит: 1.Изменение полярности выходного напряжения усилителя-ограничителя 18 и схемы 49. 2.На выходе схемы 48 появится . потенциал нуля, так как на ее входах будут разные потенциалы. 3.На шине 39 формируется коротки импульс, устанавливающий счетчик 24 в ноль. Регистр 19 также устанавливается в ноль .По шине 37 уста навливается режим сложения счетчика 24. 4.Схема 44 по инверсному управляющему входу открывается для импульсов генератора 21. 5.По выходным шинам 35 и 36 устанавливается коэффициент деления делителя 23 частоты равным Kg. 2. 6.Замкнется ключ 10, логика работы которого описывается выражением« где ХОР 1, когда в счетчике 45 записано двоичное число 00. 7. Под воздействием перепада выходного напряжения усилителя-ограничителя 18 источник В изменит полярность напряжения, и, следовательно, в интервале времени Т tл напряжение разбаланса будет противоположно по знаку напряжению разбаланса в интервале tf-t. В интервале Т ъ 2 импульсы генератора 21 поступают на входы счетчиков 42, 43 и через делитель 23 на вход счетчика 24. Код счетчика 42, работающего на сложение,растет от нуля, код счетчика 43, работающего на вычитание, уменьшается от N (J и в момент t ,j станет равным нулю, следователгано т is -1 f В момент t происходит: 1.Перепад потенциала с выхода счетчика 43 через схему 46 воздействует на счетные входы счетчика 45 и триггера 47. В результате,в счётчике 45 запишется двойное число 01, а на выходе триггера 47 устанавливается потенциал, логически равный выходному потенциалу схемы 49. 2.На выходе схемы 48 установится потенциал 1, схема 44 закрывается, и в счетчике 42 зафиксируется код NO. 3.Счетчик 42 устанавливается в режим вычитания, а счетчик 43 - в режим сложения. 4.Замкнется один из ключей 11 или 12, в соответствии q выражением (3), и к входу усилителя 9 подключится опорное напряжение, полярность которого противоположна полярности напряжения разбаланса. 5.Счетчик 24 устанавливается в режим сложения или вычитания, что определяется логическим уравнением Х24 Х48(Х8- Х + Xg-X, , (5) где Х2.,,если счетчик 24 установлен в режим сложения . 6.Коэффициент деления делителя 23 устанавливается К о- т. В интервале Tj, - t - t выходно напряжение интегратора 17 уменьшает ся по абсолютной величине до нуля. В момент t усилитель-ограничитель 18 изменит свою полярность, под воздействием чего источник 8 изменит свою полярность напряжения питания. Далее, в интервалах Т t - t и Т4 tf, - tj, устройство работает так же, как и в интервалах Т t а 4 3 ° другой полярности напряжения источника 8, и в м мент tj- в счетчике 45 запишется дво ичное число 10. Для интервалов Т. и Т имеем со отношение Т - Ц т T,-UX о Uo или, с учетом выражений для U т - т и i- . Jk г о 821R + R,j) m -г -гRi R-1 TO- 2(R; + R,) х| -г в интервале времени Т. счетчик работает в режиме сложения, а дели тель 23 частоты имеет К( 2.Следо вательно, за указанный интервал в счетчике запишется код i Kq В интервале Т К т, и за это интервал в счетчике 24 поступит ко личество импульсов .- аСчетчиком 24 в момент t формирует ся алгебраическая разность кодов N и N2- Режим работы счетчика 24 в и тервале Та, выбранный согласно выражению (5), определяется в конечном счете знаком числителя в выраж нии (6) , так что при R, R 7 О счетчик 24 работает на вычитание,а при ,- - О счетчик 24 работает на сложение. Таким образом, в момент t в счетчике 24 сформируется код м -ы -N -1т -R-l)T7 мл-м а-5о тозТнТПГрТТ J.T /1 20 2о с учетом последующего цикла работы в интервале tg-t в счетчике 24 зафиксируется код 2N, fT, ,. В момент J: б начинается второй э аналого-цифрового преобразования. этот момент, а так же в последующем, в момент tg логическим блоком 51 вырабатывается блокировочный сигнал где 1, если в счетчике 45 записано двоичное число 10, Х 1, если в счетчике 45 записано двоичное число 11. При XjfA 1 отменяется действие логического уравнения (4),и вместо ключа 10 остается замкнутым один из ключей 11 или 12, тот,который был замкнут до момента t(, . Логика работы ключа 10 на основании выражений (4) и (7) примет вид -ю 48 -l-t 00В момент t,кроме того,происходит: 1.Код N4 заносится в блок 25 цифровой памяти, а счетчик 24 сбрасывается в ноль. 2.По шине 34 схема 22 закрывается для импульсов генератора 21. 3.Источник 8 сменит полярность напряжения. 4.Навыходе схемы 48 появится потенциал нуля и схема 44 откроется для импульсов генератора 21. Начинается формирование интервала времени Tg. TO, в течение которого к входам усилителя 9 подключено опорное напряжение DOВ момент t-f ; 1.Б счетчике 45 запишется двоичное число 11.. 2.В регистр 19 из блока 25 вводится код N. 3.Схема 22 открывается для импульсов генератора 21. 4.Коэффициент деления делителя 23 установится Кд 1. 5.Триггер старшего разряда счетчика 24 установится в единицу,а остальные разряды в ноль. 6.Счетчик 24 установится в режим сложения. В остальном происходит то же,что и в моменты t. Обычно в тензометрии практически легко обеспечить, чтобы 0,95 С1,05. Номинальное требование к установке частоты генератора 21 где fv, - номинальная частота генератора 21. Если допустить отклонение частоты f от номинальной в пределах fH + 5% f -) fH - 5%, что позволит применить простейшую схему генератора 21, то с учетом вы ражения (8) получим ORT Условие (9) позволяет выполнить цифроангшоговый преобразователь из четырех декад, образованных резисто рами 15 и 14, При введении кода N в регистр 1 разряд счетчика 24 выполняе роль знакового. Если У i, то резистор 14 не меняет своего состояния, а разрядные резисторы 15 комму тируются в соответствии с дробной частью кода N.. Если 1, то одновременно с коммутацией резисторов 15 изменит свое состояние и ре зистор 14. В результате, коэффициент переда чи цифроанеипогового преобразователя при введенном в регистр 19 кода Мд будет OQ-V.SQ.O. (, -г Л. П о где а о 1 , если знаковый резистор 14 остался в исходном состоянии Мд 1; 1 , если резистор i разряда изменит свое состояние.Есл N д 1, то go+go(N4-1) 2(jo Если , то Отсюда при введении кода регис 19 отчошение коэффициента передачи цифроаналогового преобразователя к исходному Kfj paBHO Кя (N4-l) 1 2 4/ имееп соотношени Интервалы Т и Tg являются повторением интервалов Tj и Tfe при другой полярности питания Следовательно, полагая Т Tg в счетчике 24 запишется, код , R -R, -И+ГПоскольку триггер старшего разряда счетчика 24, предварительно установленный в состояние 1 с поступ лением первого счетного импульса установится в состояние О, а с приходом второго импульса если д- 71, установится снова состояние 1. Код Мв,заносится в блок 25 цифровой памяти, и работа устройства в первом режиме заканчивается. Второй режим работы устройства. В этом режиме имеются следуккцие отличия в работе устройства. С эадатчика 50 на вход логического блока 51 поступает потенциал нуля. Это приводит к тому, что в интервалах и счетчик 24 работает в противоположном режиме Х,+Х g Х Т.е. во втором режтасе один из сигна;Лов X g или Хф инвертируется. В момент tj в счетчике 24 формируе ся алгебраическая сумма кодов Н и N4. I V, к, 5 г N,-N.N. -.. го (v R Vft-i соответственно, Rt+uf -l В моменты t, tg из блока 25 .памяти в регистр 19 вводится прямой код NBUK.- и в момент t в счетчик 24 вводится инверсный код выщ- моменты t-, t() аналогично первому режиму в регистр 19 вводится код N. В результате, за интервалы tg-t(, получим соотношение Код в счетчике 24 в момент tio определитея . Ra.. UR, Ua uRv R U, Поскольку величина cf R - TO при положительном uR триггер старшего разряда счетчика 24 будет находиться в состоянии единицы.При отрицательнс 1 bR указанный триггер будет находиться в состоянии ноль. Таким образом состояние этого триггера отображает знак измеряемой величины cTR. Таким образом предлагаемое устройство позволяет непосредственно измерять приращение сопротивления измерительного резистора. При этом выходной код не зависит от точности установки опорной частоты. Поскольку вреТля интегрирования напряжения разбала са равно периоду сетевого напряжения исключается погрешность измерения из-за наводок в цепи резистивного датчика. Погрешности из-за смещения нулей усилителя 9, усилителя-ограничителя 18 и интегратора 17 исключаются за счет того, что формирование, как промежуточного, так и выходного кодов осуществляется дважды с изменением полярности напряжения питания мостовой схемы. Неточность установки этого напряжения не приводит к погрешности измерения благо даря тому, что опорное напряжение формируется из того же напряжения. Точность измерения определяется толь ко резистивными элементами, а именно точностью изготовления резисторов мостовой схемы, делителя напряжения и умножающего цифроаналогового преобразователя. Кроме измерения относительного приращения сопротивления,устройство позволяет измерять отношение сопротивлений тензорезисторов 1 и 2. Формул.а изобретения 1. Цифровой измерительный неурав новешенный мост, содержащий мосто1вую схему, одно плечо которой образовано измерительным резистором, например, тензорезистором, источник питания, один выход которого подклю чен к одной вершине диагонали питания, усилитель разбаланса, один вход которого подключен к первой вершине измерительной диагонали, соединенной с общей точкой постоянн резисторов мостовой схемы, последов тельно соединенные интегратор и уси литель-ограничитель , выход которого соединен с управляющим входом ис точника питания, два ключа, датчик временных интервалов, соединенный с выходом усилителя-ограничителя и управляющими входами ключей, измеритель временных интервалов, содержащий генератор импульсов и последовательно соединенные схему И и счетчик, управляющие входы которых соединены с датчиком временных инте валов, отличающийся тем что, с целью повышения точности измерения относительного прирсшхения сопротивления измерительного резнетора, он снабжен делителем напряжения, образованным тремя последоватрльно соединенными резисторами йод ключенными к вершинам диагонали питания и имеющими дв.а выхода в точка соединения смежньйс резисторов,цифро аналоговым преобразователем, вход которого соединен с выходом усилителя разбаланса, а выход подключен к входу интегратора, регистром, выходы которого подключены к управляющим входам цифроаналогового преобразова- теля, третьим ключом, блоком цифровой памяти, входы которого подключены к выходам счетчика, а выходы соединены с входами регистра и счетчика , делителем частоты, включенным между выходом схемы И и входом счетчика, при этом второй вход усилителя разбаланса через ключи соединен, соответственно, со второй вершиной измерительной диагонали и выходами делителя напряжения, источник питания выполнен в виде источника напряжения, другой выход которого подключен к другой вершине диагонали питания и к датчику временных интервалов,управляющие входы регистра, делителя частоты и блока цифровой памяти подключены к датчику временных интервалов. 2. Устройство по п.1,0 т л ичающееся тем, что датчик временных интервалов содержит формирователь строба, второй и третий счетчики,, входы которых соединены между собой через схему И-ИЛИ с генератором импульсов, четвертый счетчик , два выхода которого подключены к управляющим входам второго и третьего счетчиков, а вход через схему ИЛИ соединен с выходами второго и третьего счетчиков и выходом формирователя строба, триггер, D-вход KOTODoro соединен с одним из входов схемы исключающее ИЛИ и через схему согласования с входной шиной датчика временных интервалов, подключенной к выходу усилителяограничителя, а выход соединен с другим входом схемы исключающее ИЛИ, а С-вход подключен к входу четвертого счетчика,логический блок, входы которого подключены к выходам четвертого счетчика, к выходу схемы исключающее ИЛИ,к выходу задатчика режимов работы и к входной шине,датчика временных интервалов, соединенной с источником питания, при этом выходы логического блока соединены с выходными гиинами датчика временных интервалов, один управляющий вход схемы И-ИЛИ соединен с выходом формирователя строба, а второй вход - с выходом схемы исключающее ИЛИ. Источники информации, при1штые во внимание при экспертизе 1.Авторское свидетельство СССР № 423055, .G 01 R 17/10, 1971. 2.Авторское свидетельство СССР 611157, G 01 R 17/10, 1975.

2f

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой многоточечный измерительный мост | 1980 |

|

SU938164A1 |

| Цифровой неуравновешенный измерительный мост | 1979 |

|

SU983551A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ДАВЛЕНИЯ С ЧАСТОТНЫМ ВЫХОДОМ НА ОСНОВЕ НАНО- И МИКРОЭЛЕКТРОМЕХАНИЧЕСКОЙ СИСТЕМЫ | 2009 |

|

RU2406985C1 |

| Цифровой многоточечный тензометрический мост | 1980 |

|

SU917101A2 |

| Аналого-цифровой преобразователь неэлектрических величин | 1985 |

|

SU1403374A1 |

| Цифровой многоточечный измерительный мост | 1978 |

|

SU746300A1 |

| ЧАСТОТНЫЙ ПРЕОБРАЗОВАТЕЛЬ СИГНАЛА РАЗБАЛАНСА ТЕНЗОМОСТА | 2009 |

|

RU2396705C1 |

| ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ РАЗБАЛАНСА МОСТОВОЙ СХЕМЫ В ЧАСТОТУ ИЛИ СКВАЖНОСТЬ | 2018 |

|

RU2699303C1 |

| Многоканальный преобразователь приращения сопротивления в интервал времени | 1979 |

|

SU892707A1 |

| ДАТЧИК ДАВЛЕНИЯ НА ОСНОВЕ НАНО- И МИКРОЭЛЕКТРОМЕХАНИЧЕСКОЙ СИСТЕМЫ С ЧАСТОТНЫМ ВЫХОДНЫМ СИГНАЛОМ | 2009 |

|

RU2408857C1 |

Авторы

Даты

1980-12-23—Публикация

1978-12-25—Подача