уменьшает КПД и увеличивает массу ,и объем импульсного регулятора.

Целью изобретения является повышение входного напряжения, уменьшение «го массы и Объема, а также упрощение схемы импульсного регулятора.

Для этого в вмпульсном регуляторе, который содержит сглаживаюШИЙ дроссель, цепочку из последовательно соединенных ключевых транзисторов, один конец которой Подсоединен к первому входному выводу регулятора для подключения основного источника питания, а другой ее конец связаи с выходным выводом регулятора, и группу вспомогательных источников питания, образующих последовательную цепь, первый крайний вывод -кюторой соедин ен через диод с общей точкой входного и выходного выводов регулятора, второй крайний вывод - с общей точкой транзистора, подключенного к первому входному выводу регулятора, .и следующего транзистора цепочии, а промежуточные выводы депи подключены через диоды к соответствующим общим точкам транзисторов цепочки, каждый из указанных вспомогательных источников питания содержит два однояолупериодных выпрямителя, выходные выводы которых включены последовательно и согласно, а входные выводы подключены к разным дополнительным обмоткам сглаживающего дросселя, причем первый входной вывод одного из указанных выпрямителей подключен к началу соответствующей дополлительной обмотки дросселя, а соответствующий первый входной вывод другого вылрям-ителя - к коицу дополнительной обмотки дросселя.

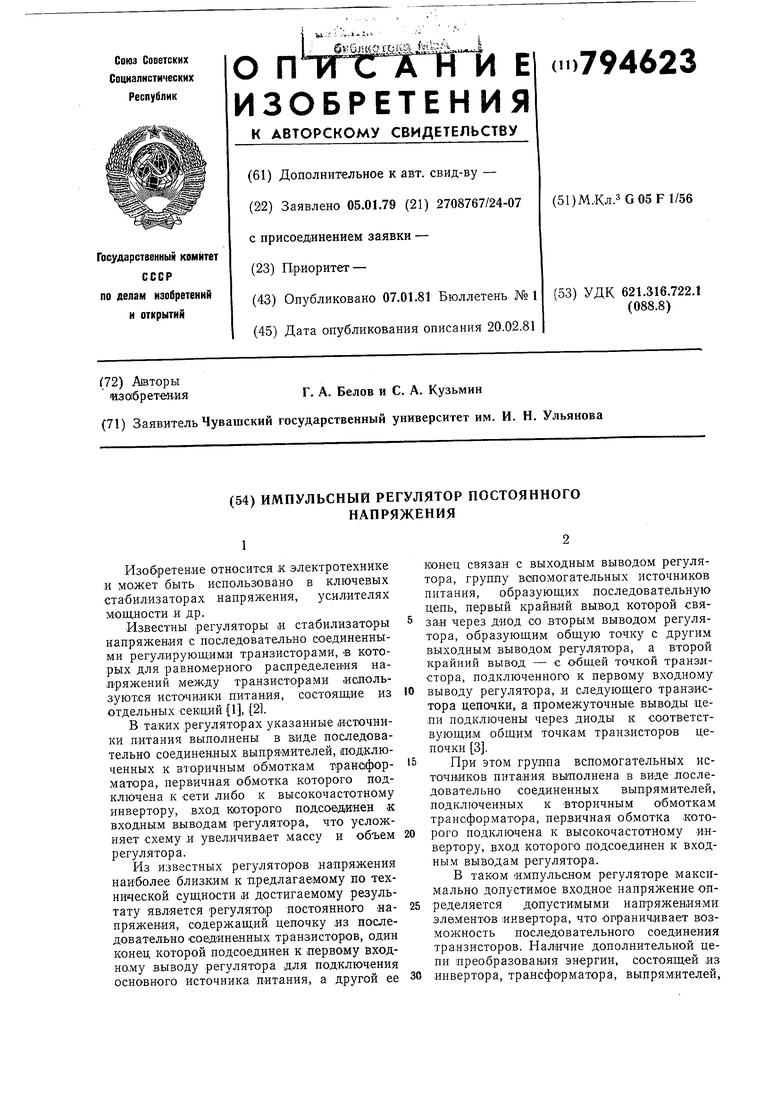

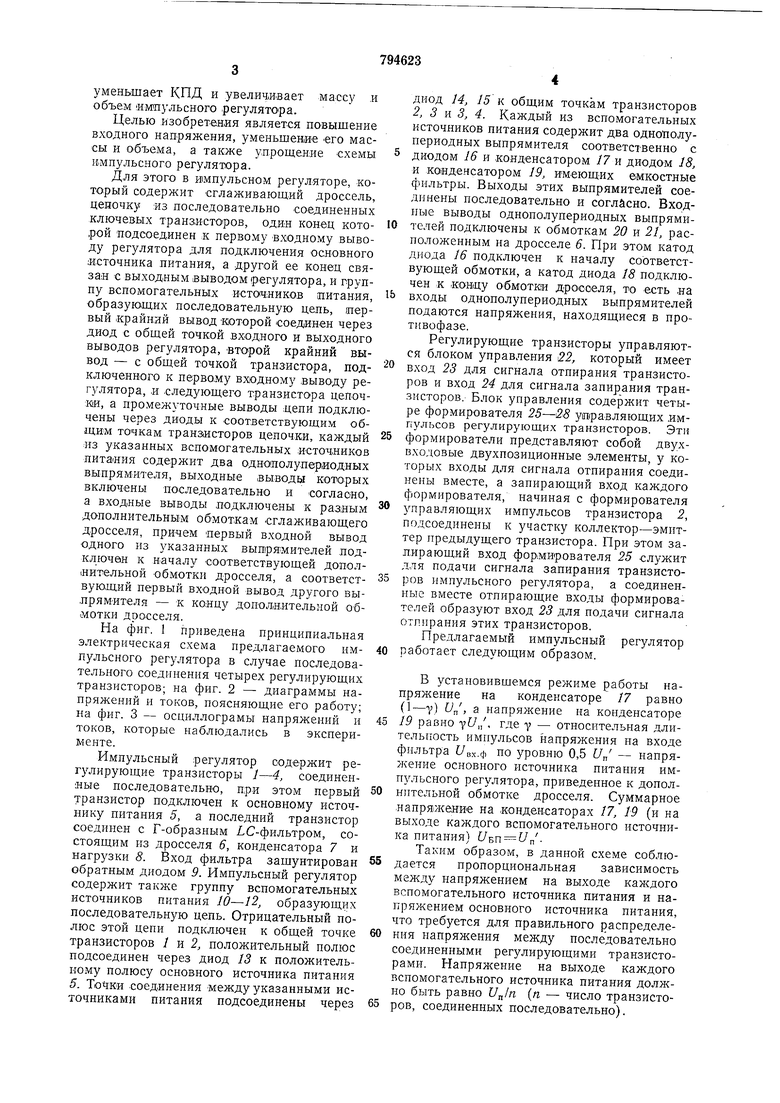

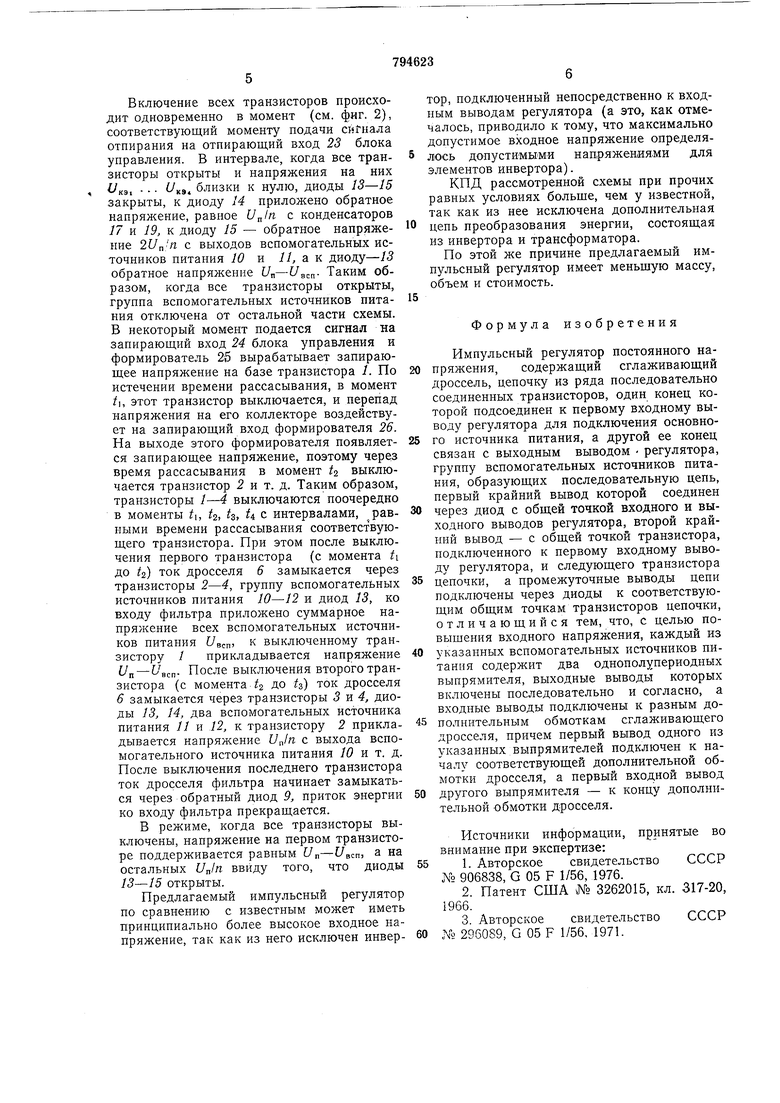

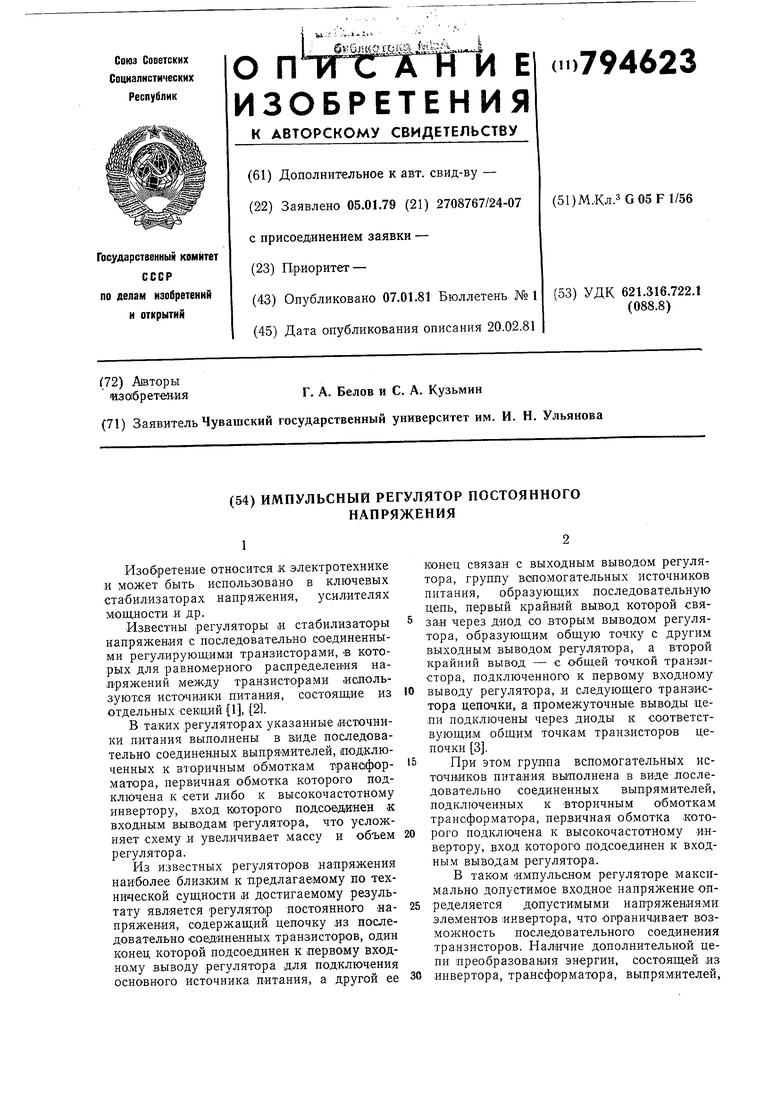

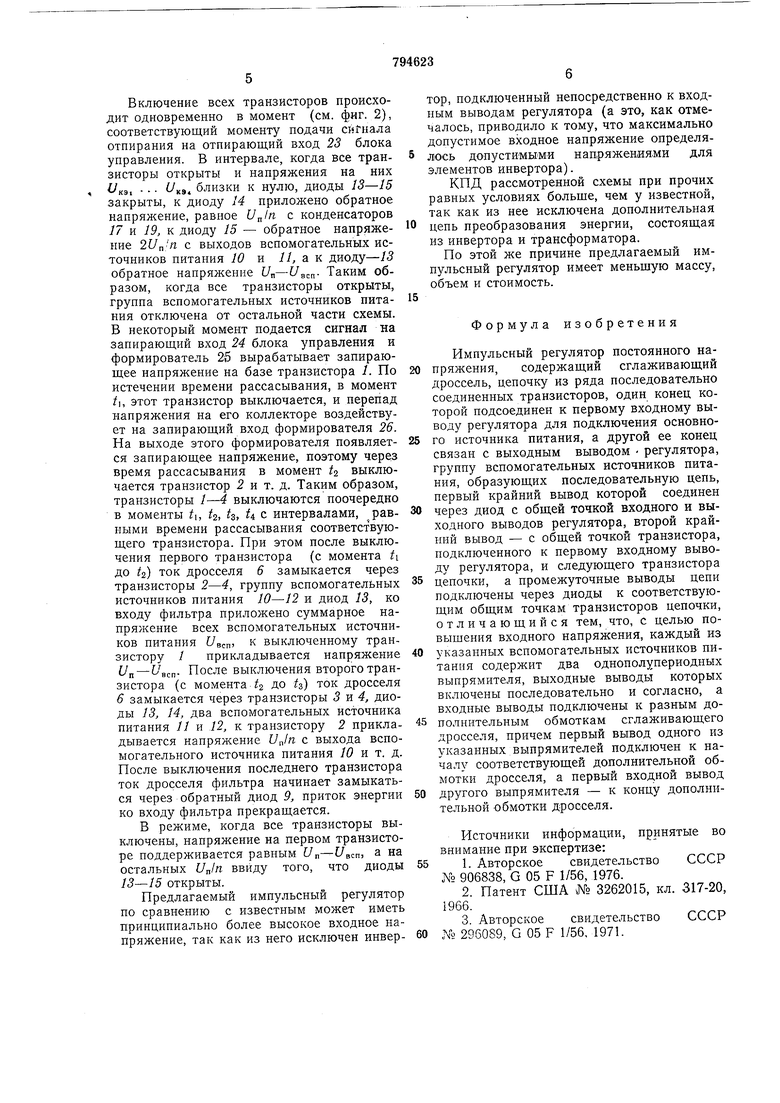

На фиг. 1 приведена принципиальная электрическая схема предлагаемого импульсного регулятора в случае последовательного соединения четырех регулирующих транзисторов; на фиг. 2 - диаграммы напряжений и токов, поясняющие его работу; на фиг. 3 - осциллограмы напряжений и токов, которые наблюдались в эксперименте.

Импульсный регулятор содержит регулирующие транзисторы /-4, соединенные последовательно, при этом первый транзистор подключен к основному источнику питания 5, а последний транзистор соединен с Г-образным LC-фильтром, состоящим из дросселя 6, конденсатора 7 и нагрузки 8. Вход фильтра защунтирован обратным диодом 9. Импульсный регулятор содержит также группу вспомогательных источников питания 10-12, образующих последовательную цепь. Отрицательный полюс этой цепи подключен к общей точке транзисторов 1 я 2, положительный полюс подсоединен через диод 13 к положительному полюсу основного источника питания 5. Точки соединения между указанными источниками питания подсоединены через

диод 14, 15 к общим точкам транзисторов 2, 3 и 3, 4. Каждый из вспомогательных источников питания содержит два однонолупериодных выпрямителя соответственно с диодом 16 и конденсатором 17 и диодом 18, и конденсатором 19, имеющих емкостные фильтры. Выходы этих выпрямителей соединены последовательно и согласно. Входные выводы однополупериодных выпрямителей подключены к обмоткам 20 и 21, расположенным на дросселе 6. При этом катод диода 16 подключен к началу соответствующей обмотки, а катод диода 18 подключен :К КОнщу обмотк1и дросселя, то есть на

входы однополупериодных выпрямителей подаются напряжения, находящиеся в противофазе.

Регулирующие транзисторы управляются блоком управления 22, который имеет

вход 23 для сигнала отпирания транзисторов и вход 24 для сигнала запирания транзисторов. Блок управления содержит четыре формирователя 2S-SS управляющих импульсов регулирующих транзисторов. Эти

формирователи представляют собой двухвходовые двухпозиционные элементы, у которых входы для сигнала отпирания соединены вместе, а занирающий вход каждого формирователя, начиная с формирователя

заправляющих импульсов транзистора 2, подсоединены к участку коллектор-эмиттер предыдущего транзистора. При этом запирающий вход формирователя 25 служит для подачи сигнала запирания транзисторов импульсного регулятора, а соединенные вместе отпирающие входы формирователей образуют вход 23 для подачи сигнала отпирания этих транзисторов.

Предлагаемый импульсный регулятор

работает следующим образом.

В установившемся режиме работы напряжение на конденсаторе 17 равно (1-Y) и„, а напряжение на конденсаторе

19 равно vf/,/, где -у - относительная длительность импульсов напряжения на входе фильтра t/вх.ф по уровню 0,5 и„ - напряжение основного источника питания импульсного регулятора, приведенное к дополнительной обмотке дросселя. Суммарное напряжение на .конденсаторах 17, 19 (и на выходе каждого вспомогательного источника питания) U„.

Таким образом, в данной схеме соблюдается пропорциональная зависимость между напряжением на выходе каждого вспомогательного источника питания и напряжением основного источника питания, что требуется для правильного распределения напряжения между последовательно соединенными регулирующими транзисторами. Напряжение на выходе каждого вспомогательного источника питания должно быть равно и„1п (п - число транзисторов, соединенных последовательно).

Включение всех транзисторов происходит одновременно в момент (см. фиг. 2), соответствующий моменту подачи сигнала отпирания на отпирающий вход 23 блока управления. В интервале, когда все транзисторы открыты и напряжения на них УКЭ, . близки к нулю, диоды 13-15 закрыты, к диоду 14 приложено обратное напрял ение, равное и„1п с конденсаторов 17 и 19, к диоду 15 - обратное напряжение 2Unn с выходов вспомогательных источников питания 10 и 11, а к диоду-13 обратное напряжение . Таким образом, когда все транзисторы открыты, группа вспомогательных источников питания отключена от остальной части схемы. В некоторый момент подается сигнал на запирающий вход 24 блока управления и формирователь 25 вырабатывает запирающее напряжение на базе транзистора /. По истечении времени рассасывания, в момент /I, этот транзистор выключается, и перепад напряжения на его коллекторе воздействует на запирающий вход формирователя 26. На выходе этого формирователя появляется запирающее напряжение, поэтому через время рассасывания в момент t выключается транзистор 2 и т. д. Таким образом, транзисторы /-4 выключаются поочередно в моменты 1, 2, 3, и с интервалами, равными времени рассасывания соответствующего транзистора. При этом после выключения первого транзистора (с момента t до /s) ток дросселя 6 замыкается через транзисторы 2-4, группу вспомогательных источников питания 10-12 и диод /5, ко входу фильтра приложено суммарное напряжение всех вспомогательных источников питания /7всп к выключенному транзистору 1 прикладывается напряжение t/n - всп- После выключения второго транзистора (с момента 2 ДО /з) ток дросселя 6 замыкается через транзисторы 5 и 4, диоды 13, 14, два вспомогательных источника питания // и 12, к транзистору 2 прикладывается напряжение UJn с выхода вспомогательного источника питания 10 и т. д. После выключения последнего транзистора ток дросселя фильтра начинает замыкаться через обратный диод 9, приток энергии ко входу фильтра прекращается.

В режиме, когда все транзисторы выключены, напряжение на первом транзисторе поддерживается равным f/n-С всп, а на остальных t/n/n ввиду того, что диоды 13-15 открыты.

Предлагаемый импульсный регулятор по сравнению с известным может иметь принципиально более высокое входное напряжение, так как из него исключен инвертор, подключенный непосредственно к входным выводам регулятора (а это, как отмечалось, приводило к тому, что максимально допустимое входное напряжение определялось допустимыми напряжениями для элементов инвертора).

КПД рассмотренной схемы при прочих равных условиях больще, чем у известной, так как из нее исключена дополнительная

цепь преобразования энергии, состоящая из инвертора и трансформатора.

По этой же причине предлагаемый импульсный регулятор имеет меньшую массу, объем и стоимость.

Формула изобретения

Импульсный регулятор постоянного напряжения, содержащий сглаживающий дроссель, цепочку из ряда последовательно соединенных транзисторов, один конец которой подсоединен к первому входному выводу регулятора для подключения основного источника питания, а другой ее конец связан с выходным выводом регулятора, группу вспомогательных источников питания, образующих последовательную цепь, первый крайний вывод которой соединен

через диод с общей точкой входного и выходного выводов регулятора, второй крайний вывод - с общей точкой транзистора, подключенного к первому входному выводу регулятора, и следующего транзистора

цепочки, а промежуточные выводы цепи подключены через диоды к соответствующим общим точкам транзисторов цепочки, отличающийся тем, что, с целью повышения входного напряжения, каждый из

указанных вспомогательных источников питания содержит два однополупериодных выпрямителя, выходные выводы которых включены последовательно и согласно, а входные выводы подключены к разным дополнительным обмоткам сглаживающего дросселя, причем первый вывод одного из указанных выпрямителей подключен к началу соответствующей дополнительной обмотки дросселя, а первый входной вывод

другого выпрямителя - к концу дополнительной обмотки дросселя.

Источники информации, принятые во внимание при экспертизе:

1. Авторское свидетельство СССР № 906838, G 05 F 1/56, 1976.

2.Патент США № 3262015, кл. 317-20, 1966.

3.Авторское свидетельство СССР „NO 296089, G 05 F 1/56, 1971.

| название | год | авторы | номер документа |

|---|---|---|---|

| Импульсный регулятор постоянного напряжения | 1977 |

|

SU675554A1 |

| ИСТОЧНИК ПИТАНИЯ С БЕСТРАНСФОРМАТОРНЫМ ВХОДОМ | 1992 |

|

RU2009607C1 |

| Стабилизированный инвертор | 1981 |

|

SU964908A1 |

| Квазирезонансный преобразователь напряжения с улучшенной электромагнитной совместимостью | 2019 |

|

RU2727622C1 |

| Импульсный стабилизатор постоянного напряжения | 1980 |

|

SU951267A1 |

| Транзисторный импульсный регулятор с повышенным входным напряжением | 1986 |

|

SU1381461A1 |

| Стабилизированный выпрямитель | 1987 |

|

SU1423992A1 |

| Преобразователь постоянного напряжения в постоянное | 1980 |

|

SU928561A1 |

| Стабилизированный конвертор | 1979 |

|

SU773861A1 |

| Стабилизированный конвертор | 1978 |

|

SU748721A1 |

Авторы

Даты

1981-01-07—Публикация

1979-01-05—Подача