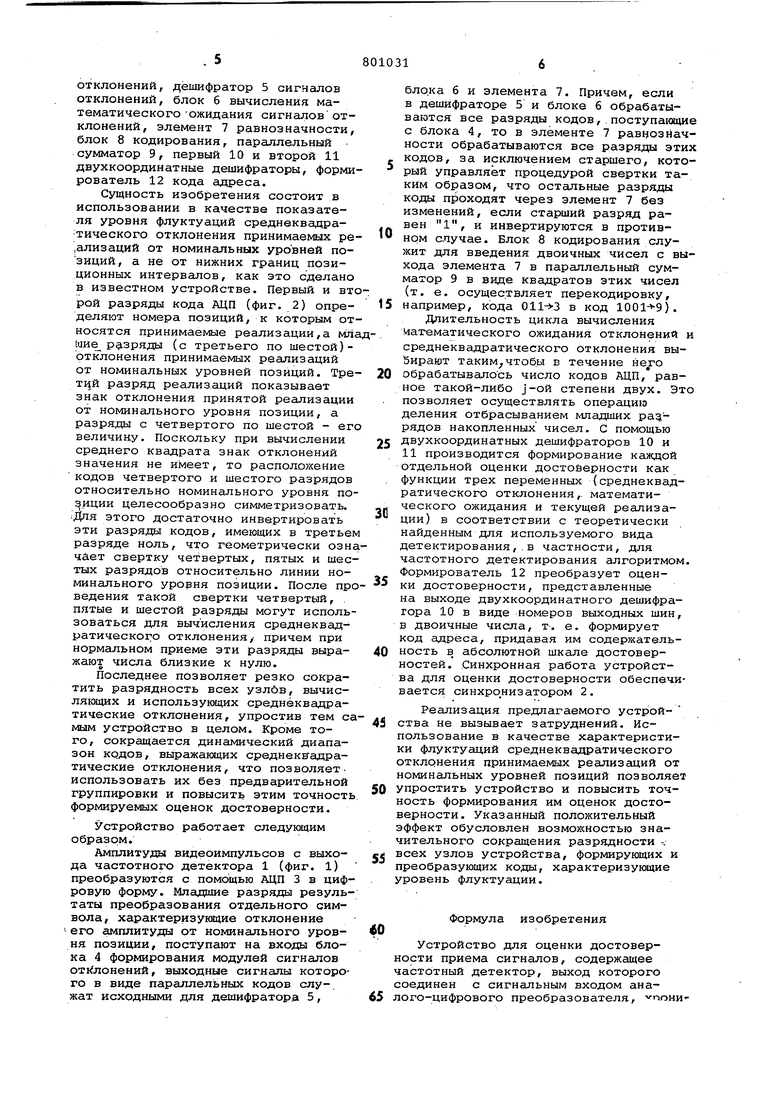

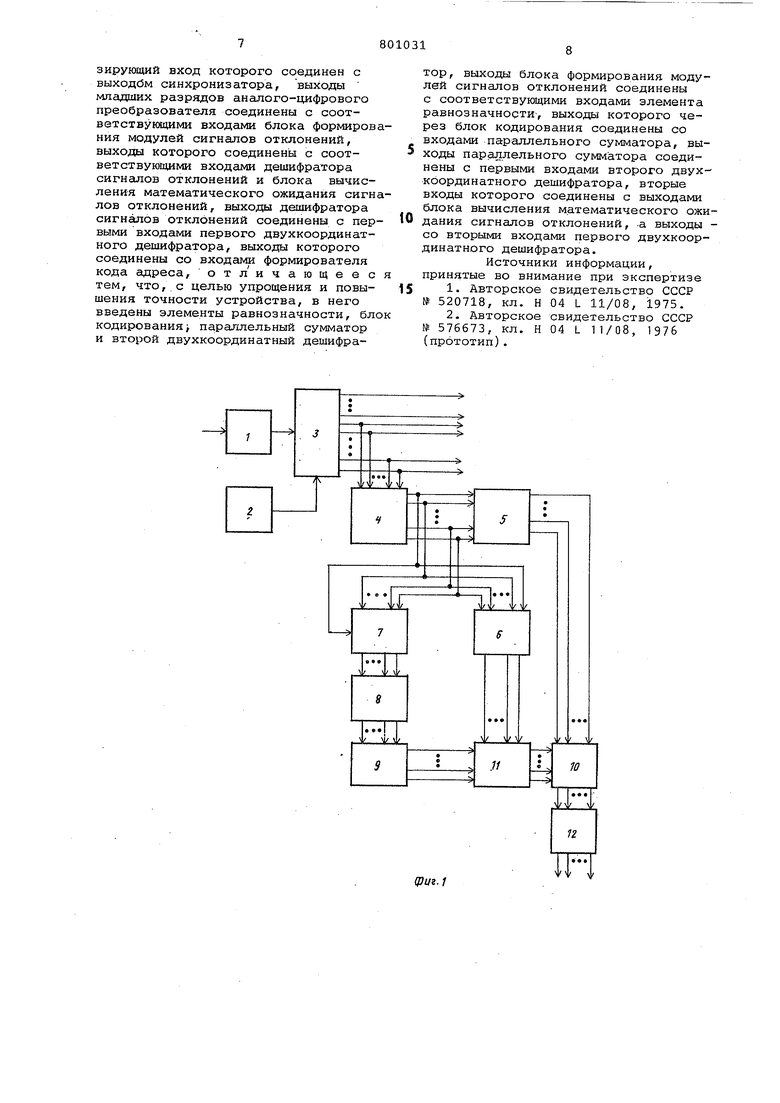

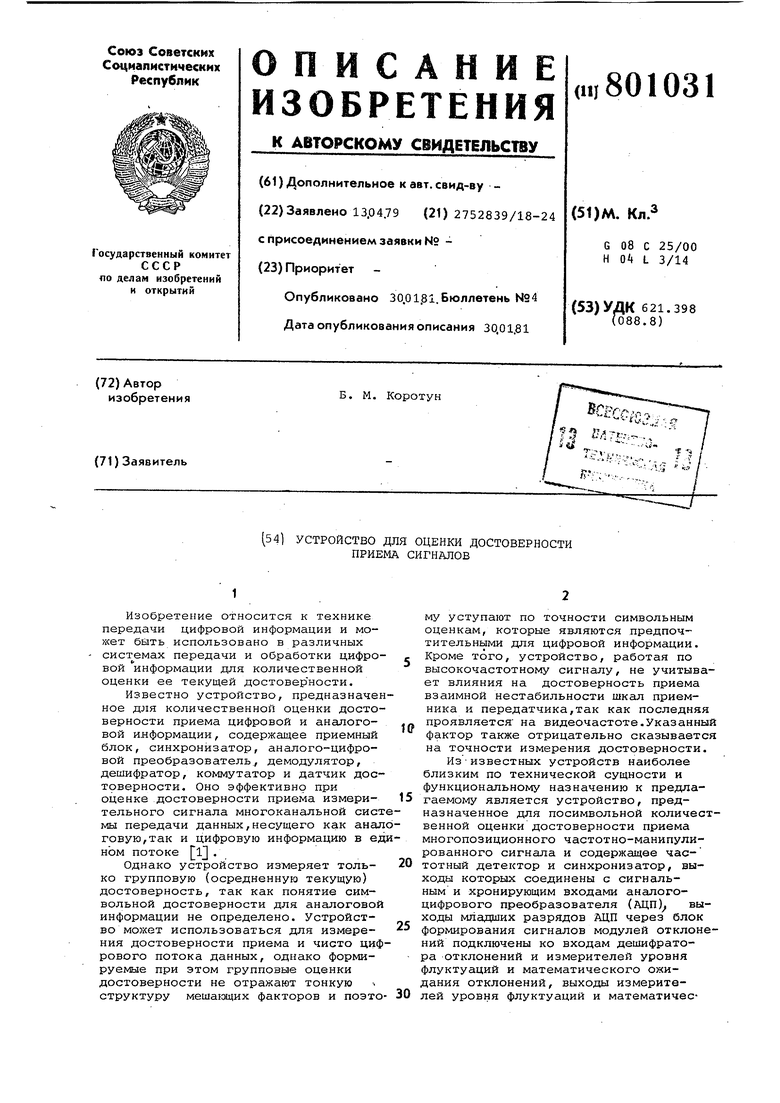

кого ожидания отклонений соединены соответственно с сигнальными и Управ ляющими входами корректора оценки уровня флуктуации, выходы которого через двухкоординатный дешифратор, соединенный второй группой своих входов с выходами дешифратора отклонений, подключены ко входам преобразователя номера шины в код. В этом устройстве используется АЦП со шкалой преобразуемых напряжений, в n-v-l / П раз (где п - позиционность ко да) превышающей нормальную шкалу напряжений передаваемого кода на его входе (т. е. шкалу напряжений при отсутствии помех). Число разрядов АЦП К выбрано существенно превышающи (т+ 2), где m - минимально допустимо число разрядов АЦП - такое, что В этом случае m старших разрядов Кразрядного слова, формируемого АЦП, определяют позицию, принимаемую в ка честве решения, а оставшиеся младшие разряды характеризуют отклонение принятой реализации от указанной позиции. Именно эти младшие разряды используются для формирования оценок достоверности, поступая, параллельно на измерители уровня флуктуации и ма тематического олсидания отклонений и дешифратор отклонений 2J . Поскольку на входы обоих измврите . лей поступают одни и те же коды, то вычисление математического ожидания отклонений и уровня флуктуации производится относительно одного и того же начала отсчета, которым в устройстве является нижняя граница позицио ного интервала, при этом уровень флуктуации по существу представляет собой второй нецентральный момент распределения кодов АЦП в позиционно интервале. Использование в качестве показателя уровня флуктуации второго нецентрального момента ведет . к определенным издержкам. С использованием для оценки уров флуктуации второго нецентрального м мента связан и второй недостаток иЧ вестного устройства.Выходные коды и (Мирителя уровня флуктуации имеют за счет операции возведения в квадрат оцень большой динамический диапазон Использование для индивидуальной обработки в корректоре оценки уровня флуктуации и далее в двухкоординатном дешифраторе всех.кодов, возможных навыходе измерителя, привело бы к чрезвычайной сложности и громоздко ти этих устройств. Поэтому выходные коды измерителя предварительно объе диняют в группы и каждой группе ставят в соответствие код, соответствующий, например, среднему коду группы. Он и подается на дальней шую обработку. Такая вынужденная ступенчатая аппроксимация выходных кодов измерителя уровней флуктуации снижает в конечном счете точность оценок достоверности, формируемых известным устройством. Совместное преобразование оценок уровней флуктуации и математических ожиданий отклонений является нелинейной операцией, и осуществление этого преобразования с помощью корректора оценок уровней флуктуации :целесообразно до тех пор, пока число различных кодов, подаваемых на сигнальные и управляющие входы корректора, невелико. При (Повышении точности оценок достоверности число таких кодов растет, корректор резко усложняется и коррекция, как принцип указанного выше совг местного преобразования, утрачивает свою эффективность. Цель изобретения - упрощение устройства и повышение точности формируемых им оценок достоверности. Указанная цель достигается тем, что в известное устройство для оценки достоверности приема сигналов, содержащее частотный детектор, выход которого соединен с сигнальным входом аналого-цифрового преобразователя, хронизирующий вход которого соединен с выходом синхронизатора, выходы младших разрядов аналого-цифрового преобразователя соединены с соответствующими входами блока формирования модулей сигналов отклонений, выходы которого соединены с соответствующими входами дешифратора сигналов отклонений и блока вычисления математического ожидания сигналов отклонений, выходы дешифратора сигналов отклонений соединены с первыми входами первого двухкоординатного дешифратора, выходы которого соединены со входами формирователя кода адреса, введены элемент равнозначности, блок кодирования, параллельный сумматор и второй двухкоординатный дешифратор, выходы блока формирования модулей сигналов отклонений соединены с соответствукицими входами элемента равнозначности, выходы которого через блок кодирования соединены со входами параллельного сумматора, выходы параллельного сумматора соединены с первыми входами второго двухкоординатного дешифратора, вторые входы которого соединены с выходами блока вычисления математического ожидания сигналов отклонений, а выходы - со вторыми входами первого двухкоординатного дешифратора. На фиг. 1 показана функциональная бло.к--схема устройства; на фиг. 2пример размещения кодов АЦП в позиционном интервале для случая использования четырехпозиционного кода и шестиразрядного АЦП. Устройство содержит частотный детектор 1, синхронизатор 2, аналогоцифровой преобразователь 3 (АЦП), блок 4 формирования модулей сигналов отклонений, дешифратор 5 сигнсшов отклонений, блок б вычисления математического Ожидания сигналовотклонений, элемент 7 равнозначности, блок 8 кодирования, параллельный сумматор 9, первый 10 и второй 11 двухкоординатные дешифраторы, форми рователь 12 кода адреса. Сущность изобретения состоит в использовании в качестве показателя уровня флуктуации среднеквадратического отклонения принимаемых ре ,ализаций от номинальных уровней позиций, а не от нижних границ позиционных интервалов, как это сделано в известном устройстве. Первый и вт рой разряды кода АЦП (фиг. 2) определяют номера позиций, к которым от носятся принимаемые реализации,а мл 1иие разряды (с третьего по шестой)отклонения принимаемых реализаций от номинальных уровней позиций. Тре разряд реализаций показывает знак отклонения принятой реализации от номинального уровня позиции, а разряды с четвертого по шестой - ег величину. Поскольку при вычислении среднего квадрата знак отклонений значения не имеет, то расположение кодов четвертого и шестого разрядов относительно номинального уровня по идии целесообразно симметризовать. Для этого достаточно инвертировать эти разряды кодов, имеющих в третье разряде ноль, что геометрически озн чает свертку четвертых, пятых и шес тых разрядов относительно линии номинального урорня позиции. После пр ведения такой свертки четвертый, пятые и шестой разряды могут исполь зоваться для вычисления среднеквадратического отклонения/ причем при нормальном приеме эти разряды выражают числа близкие к нулю. Последнее позволяет резко сократить разрядность всех узлбв, вычисляющих и использующих среднёквадратические отклонения, упростив тем с мым устройство в целом. Кроме того, сокращается динамический диапазон кодов, выражающих среднекнадратические отклонения, что позволяетиспользовать их без предварительной группировки и повысить этим точност формируемых оценок достоверности. Устройство работает следующим образом. Амплитуды видеоимпульсов с выхода частотного детектора 1 (фиг. 1) преобразуются с помощью АЦП 3 в циф ровую форму. Младшие разряды резуль таты преобразования отдельного символа, характеризующие отклонение 1 его амплитуды от номинального уровня позиции, поступают на входы блока 4 формирования модулей сигналов от1 лонений, выходные сигналы которого в виде параллельных кодов слу-. жат исходными для дешифратора 5, блока б и элемента 7. Причем, если в дешифраторе 5 и блоке 6 обрабатываются все разряды кодов,.поступающие с блока 4, то в элементе 7 равнозначности обрабатываются все разряды этих кодов, за исключением старшего, который управляет процедурой свертки таким образом, что остальные разряды коды проходят через элемент 7 без изменений, если старший разряд равен 1, и инвертируются в противном случае. Блок 8 кодирования служит для введения двоичных чисел с выхода элемента 7 в параллельный сумматор 9 в виде квадратов этих чисел (т. е. осуществляет перекодировку, например, кода в код 1001- -9). Длительность цикла вычисления (математического ожидания отклонений и среднеквадратического отклонения выбирают таким чтобы в течение него обрабатывалось число кодов АЦП, равное такой-либо j-ой степени двух. Это позволяет осуществлять операцию деления отбрасыванием младших радрядов накопленных чисел. С помощью двухкоординатных дешифраторов 10 и 11 производится фopгvIиpoвaниe каждой отдельной оценки достойерности как функции трех переменных (среднеквадратического отклонения, математического ожидания и текущей реализации) в соответствии с теоретически найденным для используемого вида детектирования,.в частности, для частотного детектирования алгоритмом. Формирователь 12 преобразует оценки достоверности, представленные на выходе двухкоординатного дешифратора 10 в виде номеров ВЫХОДНЕЛХ шин, в двоичные числа, т. е. формирует код адреса, придавая им содержательность в абсолютной шкале достоверностей. Синхронная работа устройства для оценки достоверности обеспечивается синхро.низатором 2. Реализация предлагаемого устройства не вызывает затруднений. Использование в качестве характеристики флуктуации среднеквадратического отклрнения принимаемых реализаций от номинальных уровней позиций позволяет упростить устройство и повысить точность формирования им оценок достоверности. Указанный положительный эффект обусловлен возможностью значительного сокращения разрядности -. всех узлов устройства, формирующих и преобразующих коды, характеризующие уровень флуктуации. Формула изобретения Устройство для оценки достоверности приема сигналов, содержащее частотный детектор, выход которого соединен с сигнальным входом анаого-цифрового преобразователя, понизирующий вход которого соединен с выходсЗм синхронизатора, выходы младших разрядов аналого-цифрового преобразователя соединены с соответствующими входами блока формирования модулей сигналов отклонений, выходы которого соединены с соответствующими входами дешифратора сигналов отклонений и блока вычисления математического ожидания сигналов отклонений, выходы дешифратора сигналов отклонений соединены с первыми входами первого двухкоординатного дешифратора, выходы которого соединены со входами формирователя кода адреса, отличающеес тем, что, с целью упрощения и повышения точности устройства, в него введены элементы равнозначности, бло кодирования; параллельный сумматор и второй двухкоординатный дешифратор, выходы блока формирования модулей сигналов отклонений соединены с соответствующими входами элемента равнозначности, выходы которого через блок кодирования соединены со входами параллельного сумматора, выходы параллельного сумматора соединены с первыми входами второго двухкоординатного дешифратора, вторые входы которого соединены с выходами блока вычисления математического ожидания сигналов отклонений, -а выходы со вторыми входами первого двухкоординатного дешифратора.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР

5 № 520718, кл. Н 04 L 11/08, 1975.

2.Авторское свидетельство СССР № 576673, кл. Н 04 L 11/08, 1976 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для оценки достоверности приема сигналов | 1976 |

|

SU576673A1 |

| Устройство для оценки достоверностипРиЕМА СигНАлОВ | 1979 |

|

SU809628A2 |

| Устройство для контроля достоверности информации | 1976 |

|

SU604174A1 |

| КАРДИОМОНИТОР КВАНТИЛЬНЫЙ | 1994 |

|

RU2107455C1 |

| Устройство для контроля достоверности телеметрической информации | 1976 |

|

SU616650A1 |

| Устройство для контроля телеметрической информации | 1980 |

|

SU920814A1 |

| Устройство для адаптивного кодирования стационарных случайных процессов | 1977 |

|

SU734717A1 |

| Устройство для автовыбора при сдвоенном приеме многопозиционнных сигналов | 1977 |

|

SU660279A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ КАЧЕСТВА КАНАЛА ПЕРЕДАЧИ ДАННЫХ | 2012 |

|

RU2504830C2 |

| Устройство для контроля аналоговых объектов | 1985 |

|

SU1288702A1 |

фиг.1

г/ Зр ifp 5р Sp

//

т 2

V J(ff

фиг. г

V А--/77

Авторы

Даты

1981-01-30—Публикация

1979-04-13—Подача