(54) ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Функциональный преобразователь | 1980 |

|

SU911560A1 |

| Преобразователь напряжения в интервал времени | 1979 |

|

SU1081787A2 |

| Преобразователь сопротивления в интервал времени | 1977 |

|

SU783976A1 |

| Интегрирующий время-импульсный преобразователь | 1976 |

|

SU930659A1 |

| Преобразователь напряжения в интервал времени | 1977 |

|

SU1014140A1 |

| Преобразователь напряжения в интервал времени | 1989 |

|

SU1683174A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1411974A1 |

| Аналого-цифровой преобразователь | 1981 |

|

SU1098101A1 |

| Преобразователь напряжения в интервалВРЕМЕНи | 1979 |

|

SU801239A1 |

| Преобразователь напряжения в интервал времени | 1975 |

|

SU1001462A1 |

Изобретение относится к цифровой электроизмерительной технике и может быть использовано при создании цифро вых измерителей интегральных парамет ров электрических сигналов переменно го и постоянного тока, а также в сос таве аналого-цифровых вычислительных машин в качестве функциональных преобразователей. Известен преобразователь, содержащий интегратор, подключаемый источ ник образцовых напряжений, два блока сравнения, генератор пилообразного напряжения, генератор тактовых импульсов, триггер и ключ Выходно интервал времени у него прямо пропорционален первой степени входного напряжения. Недостаток данного преобразователя заключается в невозможности получения временного интервала, прямо пропорционального квадрату входного напряжения. Наиболее близким по технической сущности к предлагаемому является преобразователь, содержащий блок сравнения, переключаемый источник образцовых напряжений, компаратор знака, электронный переключатель,генератор тактовых импульсов, триггер и цепь сброса. Этот преобразователь имеет интервал времени, прямо , пропорциональный первой степени входного напряжения 2. Недостатком известного функционального преобразователя является отсутствие возможности получения выходного интервала времени, прямо пропорционального квадрату входного напряжения, что при имеющихся преимуществах сужает область его примене- . ния при преобразовании интегральных характеристик электрических сигналов переменного тока. Цель изобретения - расширение класса воспроизводимых функций. Указанная цель достигается тем, что в известный функциональный преобразователь, содержащий два интегратора, причем первый вход первого ин-; тегратора соединен с входной шиной преобразователя, а выход первого интегратора через компаратор знака п адключей к первому входу источника р6разцовых напряжений, второй вход которого соединен с выходом первого блока сравнения, подключенного входами к выходам первого и второго интегIpaTOpOB, первый триггер, первый {вход которого соединен с выходом генератора тактовых импульсов, второй вход подключен к выходу первого блока сравнения, а выход является первым выходом преобразователя и подключен к первому входу цепи сброса, выход которой связан со входом сброса второго интегратора и управляющему входу первого переключателя, сигнальный вход которого соединен с выходом источника образцовых напряжений, а первый выход подключен ко второму входу первого интегратора, введены второй блок сравнения, второй триггер и второй переключатель, управляющий вход которого подключен к выходу первого триггера, сигнальные входы соединены соответственно с входной шиной преобразователя и вторым выходом первого переключателя, а выход подключен ко входу второго интегратора, выход которого через второй блок сравнения соединен со вторым входом цепи сброса и первым входом второго триггера, выход которого является вторым выходом преобразователя,а второй вход подключен к выходу первого блока сравнения.

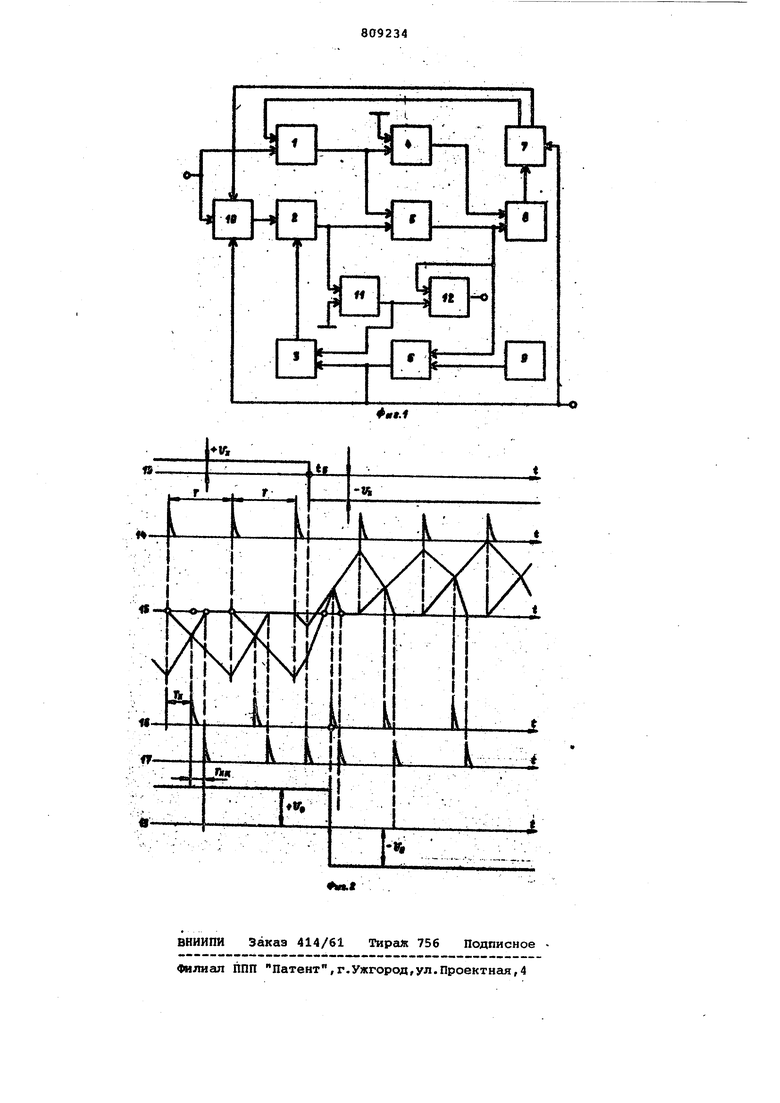

На фиг. 1 представлена структурная схема преобразователя; на фиг.2 временные диаграммы его работы.

Преобразователь (фиг. 1) содержит первый 1 и второй 2 интеграторы, цепи 3 сброса, компаратор 4 знака, первый блок 5 сравнения, первый триггер б, первый переключатель 7, источник. 8 образцовых напряжений, генератор 9, тактовых импульсов, второй переключатель 10, второй блок 11 сравнения, второй триггер 12.

На временных диаграммах работы преобразователя (фиг. 2) обозначены 13 - формэ напряжения на входной шине преобразователя,. 14 - форма сигнала на выходе генератора 9 тактовых импульсов, 15 - форма напряжений на входах первого блока 5 сравнения, 16 - форма сигнала на выходе первого блока 5 сравнения, 17 - форма.сигнала на выходе второго блока 13 сравнения, 18 - форма напряжения на выходе переключаемого источника 8 образцовых напряжений.

Устройство работает следующим образом.

Пусть на входную шину подано положительное преобразуемое напряжение (tU,j) . В момент времени t импульс с выхода генератора 9 тактовых импульсов вызывает срабатывание первого триггера б. При этом первый электронный переключатель 7 подключает положительное образцовое напряжение (tUo) с выхода переключаемого источника 8 обра,зцовых напряжений к одному из входов первого интегратора 1, второй электронный переключатель 10 подключает преобразуемое напряжение и ко входу втброго интегратора 2.В этот же момент времени отключается

цепь 3 сброса. В результате выходное напряжение первого интегратора 1 начинает линейно возрастать со скоростью , а выходное напряжение второго интегратора 2 - линейно убывать со скоростью ( t - постоянная времени интеграторов 1 и 2). в момент времени t2 выходные напряжения обоих интеграторов 1 и 2 оказываются равными, что приводит к срабатыванию первого блока 5 сравнения. Импульс с последнего вызывает срабатывание первого б и второго 13 триггеров.При этом второй злектронный переключатель 10 отключает преобразуемое напряжение DX от входа второго интегратора 5 2. Первый электронный переключатель 7 отключает образцовое напряжение UQ от входа первого интегратора 1 и подключает его через второй электронный переключатель 10 ко входу второго интегратора 2. В результате выходное напряжение первого интегратора .1 начинает линейно убывать со скоростью , а ВЕлходное напряжение второго интегратора 2 - линейно возрастать со скоростью . В моЭ . te

мент времени t выходное напряжение второго интегратора 2 достигает нуля, что приводит к срабатыванию второго блока 11 сравнения. Импульс с последнего вызывает срабатывание второго триггера 12 и цепи 3 сброса. В результате выходное напряжение второго интегратора 2 поддерживается равным нулю до прихода очередного тактового импульса. В момент времени t приходит очередной тактовый импульс с выхода генератора 9 тактовых импульсов, вновь срабатывает первый триггер 6 и цикл работы повторяется.

При смене знака преобразуемого напряжения, например в момент времени tJ, происходят следующие процессы. Начиная с момента времени t, выходное напряжение первого интегратора 1, которое до этого момента времени возрастало со скоростью , продолжает возрастать, но с большей скоростью, равной Ру . Выходное напряжение второго интегратора 2, которое до момента времени t убывало со скоростью-, начинает возрастать с той же скоростью. В момент времени ti выходное напряжение первого интегратора 1 достигает нуля, что приводит к срабатыванию компаратора 4 знака, импульс с которого подготавливает переключение источника 8 образцовых напряжений. В момент времени tf выходные напряжения интеграторюв 1 и 2 оказываются равными, что приводит к срабатыванию первого блока 5 сравнения. Импульс с последнего вызывает срабатывание первого 6 и второго 13 триггеров. При этом второй электронный переключатель 10 отключает преобразуемое напряжение 5 (Uji) от входа второго интегратора

Функциональный интегрирующий преобразователь, наряду с получением информации о первой степени преобразуемого напряжения позволяет обеспечить получение информации о его квадрате с сохранением высокой точности преобразования. Расширение функциональных возможностей наличие унифицированного выходного параметра, высокая точность преобразования выгодно отличают предлагаемое устройство от известных. Формула изобретения Функциональный преобразователь, содержащий два интегратора, причем первый вход первого интегратора соединен е входной шиной преобразователя, а выход первого интегратора через компаратор знака подключен к первому входу источника образцовых напряжений, второй вход которого соединен с выходом первого блока сравнения, подключенного входами К выходам первого и второго интеграторов, первый триггер, первый вход которого соединен с выходом генератора тактовых импульсов, второй вход подключен к выходу первого блока сравнения, а выход является первым выходом преобразователя и подключен к первому входу цепи сброса, выход которой связан со входом сброса второго интегратора и управляющему входу первого переключателя, сигнальный вход которого соединен с выходом источника образцовых напряжений, а первый выход подключен ко второму входу первого интегратора, отличающийся тем, что, с целью расширения класса воспроизводимых функций, в него введены второй блок сравнения, второй триггер и второй переключатель,управляющий вход которого подключен к выходу первого триггера, сигнальные входы соединены соответственно с входной шиной преобразователя и вторым выходом первого переключателя,а выход подключен ко входу второго ИН-. тегратора, выход которого через второй блок сравнения соединен со вторым входом цепи сброса и первым входом второго триггера, выход которого является вторым выходом преобразователя, а второй вход подключен к выходу первого блока сравнения. Источники информации, принятые во внимание при экспертизе 1.Патент США № 3745556, кл. G 06 G 7/26, опублик. 1973. 2.Авторское свидетельство СССР по заявке № 2037545/24, кл. G Об G 7/26, 1974 (прототип).

с;т

цС

«2

Авторы

Даты

1981-02-28—Публикация

1979-04-28—Подача