(54) КОМПАРАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь сигнала | 1979 |

|

SU813762A1 |

| Компаратор | 1978 |

|

SU748851A1 |

| Способ преобразования перемещения в напряжение и устройство для его реализации (его варианты) | 1981 |

|

SU1026081A1 |

| Пиковый детектор | 1979 |

|

SU864152A1 |

| Функциональный преобразователь | 1985 |

|

SU1267445A2 |

| СИСТЕМА ЭЛЕКТРОПИТАНИЯ КОМПЛЕКСА КОРАБЕЛЬНОЙ РАДИОЭЛЕКТРОННОЙ АППАРАТУРЫ | 1998 |

|

RU2124260C1 |

| Устройство для управления трехфазным непосредственным преобразователем частоты | 1981 |

|

SU995259A1 |

| Операционный усилитель | 1976 |

|

SU614442A1 |

| Устройство для допускового контроля напряжений | 1981 |

|

SU1091124A1 |

| Амплитудный преобразователь | 1981 |

|

SU960645A1 |

I

Изобретение относится к измерительной технике, в частности к измерению постоянных и переменных напряжений и токов при цифровой обработке сигналов.

Известны компараторы, выполненные на дискретных элементах, например на подобранных транзисторных дифференциальных парах 1.

Недостатком известных компараторов является ограниченная разрешающая способность.

Известен также компаратор, содержащий дифференциальный усилитель, диодно-резистивную цепь и усилитель-ограничитель 2.

Недостатками такого компаратора являются невысокая точность, стабильность и ограниченная разрещающая способность.

Пель изобретения - повышение точности, стабильности и разрешающей способности сравнения сигналов постоянного и неременного токов малых уровней.

Указанная цель достигается тем, что в компаратор, содержащий дифференциальный усилитель, диодно-резисторную цепь и усилитель-ограничитель, введены три ключа, блок управления ключами, два суммирующих резистора и конденсатор, причем

вход дифференциального усилителя через суммирующие резисторы и два ключа соединен с входными щина.ми, а выход - через последовательно соединеннные конденсатор, диодно-резисторную цепь и третий ключ соединен с входом усилителя-ограничителя, при этом, блок управления ключами соединен с входами каждого из трех ключей.

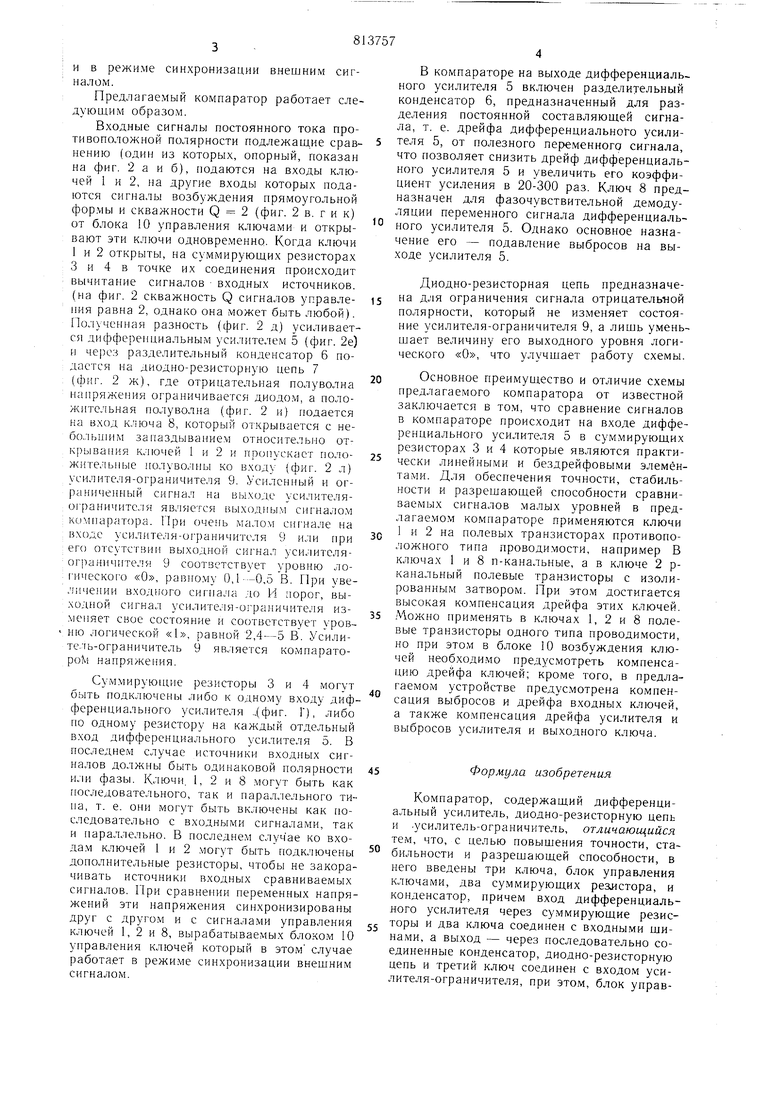

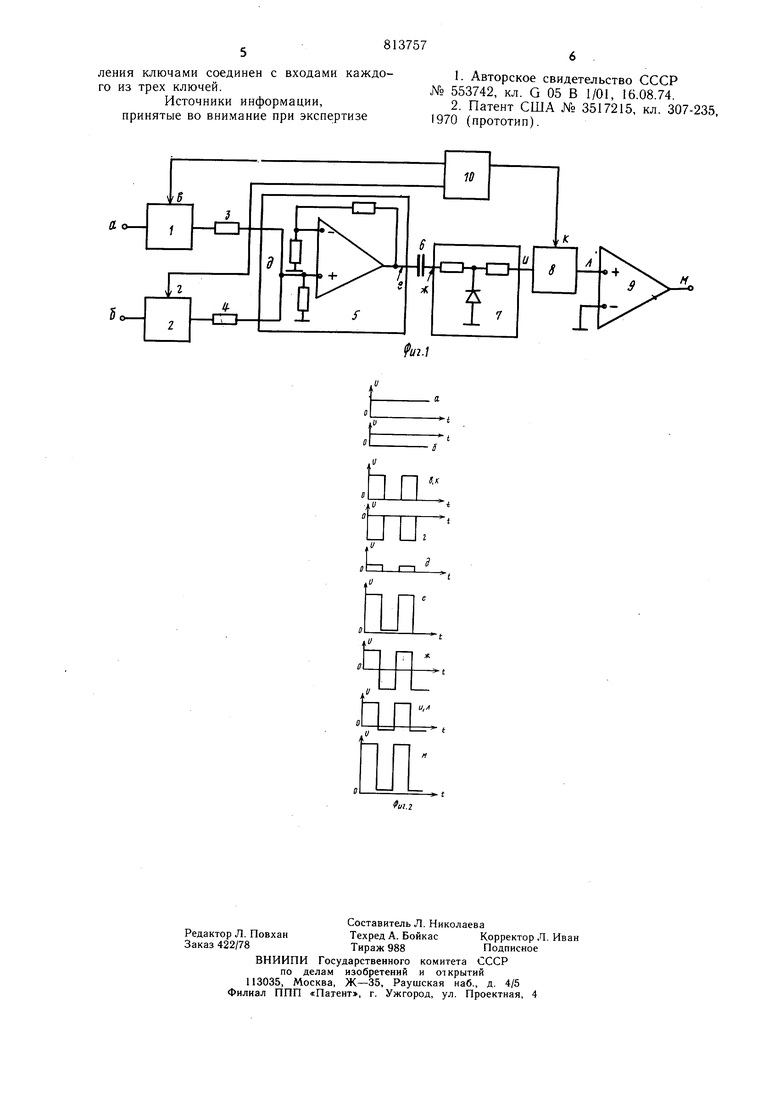

На фиг. 1 представлена функциональная схема компаратора; на фиг. 2 - временные диаграммы.

Схема содержит ключи 1 и 2, на входы которых подаются входные сигналы, подлежащие сравнению, выходы которых через суммирующие резисторы 3 и 4 подключены ко входу дифференциального усилителя 5. Выход дифференциального усилителя 5 через разделительный конденсатор 6 подключен ко входу диодно-резисторной цепи 7, выход которой, в свою очередь, через ключ 8 подключен ко входу усилителя-ограничителя 9. Выходной сигнал усилителя-ограничителя является выходом компаратора. Для управления ключами 1, 2 и 8 на их входы подаются сигналы возбуждения от блока 10 управления клк)чами, который может работать как в автоколебательном, так И в режиме синхронизации внешним сигналом. Прбх лагаемый компаратор работает следующим образом. Входные сигналы постоянного тока противоположной полярности подлежаш,ие сравнению (один из которых, опорный, показан на фиг. 2 а и б), подаются на входы ключей 1 и 2, на другие входы которых подаются сигналы возбуждения прямоугольной формы и скважности Q 2 (фиг. 2 в. г и к) от блока 10 управления ключами и открывают эти ключи одновременно. Когда ключи 1 и 2 открыты, на суммирующих резисторах 3 и 4 в точке их соединения происходит выч.чтание сигналов входных источников, (на фиг. 2 скважность Q сигналов управления равна 2, однако она может быть любой). По;|учснная разность (фиг. 2 д) усиливается дифференпиальным усилителем 5 (фиг. 2е) и че)ез разделительный конденсатор 6 подается на диодно-резисторную цепь 7 (фиг. 2 ж), где отрицательная полуволна напряжения ограничивается диодо.м, а положительная полуволна (фиг. 2 и) подается на вход ключа 8, который открывается с неболылим запаздыванием относительно открывания ключей 1 и 2 и пропускает положительные полуволны ко входу (фиг. 2 л) усилителя-ограничителя 9. Усиленный н ограниченный сигнал на Е5ыходе усилителяограничите.ля является выходным сигнало.м компаратора. При очень малом сигнале на входе усил.чтеля-ограничителя 9 и;п1 при его отсутствии выходной сигнал усилителяограничители 9 соответствует уровню ло ического «О, равио.му 0,1--0,5 В. При увеличении входного до И порог, выходной сигнал усилителя-ограничителя из.меияет свое состояние и соответствует уровню логической «1, равной 2,4-5 В. Усилите-1ь-ограннчитель 9 является компаратоpok напряжения. Суммирующие резисторы 3 и 4 могут быть подключены либо к одному входу диф ференциального усилителя (фиг. Г), либо по одному резистору на каждый отдельный вход дифференциального усилителя 5. В последнем случае источники входных сигналов должны быть одинаковой полярности и;1и фазы. Ключи. 1, 2 и 8 .могут быть как последовательного, так и параллельного типа, т. е. они могут быть включены как последовательно с входными сигналами, так и 1араллельно. В последнем случае ко входа.м ключей 1 и 2 могут быть подключены дополнительные резисторы, чтобы не закора чивать источники входных сравниваемых сигналов. При сравнении переменных напря жений эти напряжения синхронизированы друг с другом и с сигнала.ми управления ключей 1, 2 и 8, вырабатывае.мых блоком 10 управления ключей который в этом случае работает в режиме синхронизации внешним сигналом. В компараторе на выходе дифференциалього усилителя 5 включен разделительный онденсатор 6, предназначенный для разеления постоянной составляющей сигнаа, т. е. дрейфа дифференциального усилиеля 5, от полезного пере.менното сигнала, то позволяет снизить дрейф дифференциалього усилителя 5 и увеличить его коэффииент усиления в 20-300 раз. Ключ 8 предазначен для фазочувствительной демодуяции переменного сигнала дифференциалього усилителя 5. Однако основное назнаение его - подавление выбросов на выоде усилителя 5. Диодно-резисторная цепь предназначена для ограничения сигнала отрицательной полярности, который не изменяет состояние усилителя-ограничителя 9, а лищь уменьшает величину его выходного уровня логического «О, что улучшает работу схемы. Основное преимущество и отличие схемы предлагаемого компаратора от известной заключается в том, что сравнение сигналов в компараторе происходит на входе дифференциального усилителя 5 в сум.мирующих резисторах 3 и 4 которые являются практически линейными и бездрейфовыми элементами. Для обеспечения точности, стабильности и разрешающей способности сравниваемых сигналов малых уровней в предлагаемом ко.мпараторе применяются ключи 1 и 2 на полевых транзисторах противоположного типа проводимости, например В ключах 1 и 8 л-канальные, а в ключе 2 рканальный полевые транзисторы с изолированным затвором. При этом достигается высокая ко.мпенсация дрейфа этих ключей. Можно при.менять в ключах 1, 2 и 8 полевые транзисторы одного типа проводимости, но при этом в блоке 10 возбуждения ключей необходи.мо предус.мотреть компенсацию дрейфа ключей; кроме того, в предлагаемом устройстве предусмотрена компенсация выбросов и дрейфа входных ключей, а также ко.мпенсация дрейфа усилителя и выбросов усилителя и выходного ключа. Формула изобретения Компаратор, содержащий дифференциальный усилитель, диодно-резисторную цепь и .усилитель-ограничитель, отличающийся тем, что, с целью повыщения точности, стабильности и разрещающей способности, в него введены три ключа, блок управления ключами, два суммирующих резлстора, и конденсатор, причем вход дифференциального усилителя через су.ммирующие резисторы и два ключа соединен с входны.ми щинами, а выход - через последовательно соединенные конденсатор, диодно-резисторную цепь и третий ключ соединен с входом усилителя-ограничителя, при этом, блок управления ключами соединен с входами каждого из трех ключей.

Источники информации, принятые во внимание при экспертизе

а

и

L

Авторы

Даты

1981-03-15—Публикация

1979-03-27—Подача