1

Изобретение относится к импульсной технике и предназначено для использования в системах телемеханики ля распознавания и разделения по соответствующим каналам импульсных сиг-5 налов по признаку длительности.

Известны селекторы импульсных сигналов, содержащие входной, выходной вентили и схему управления выходным вентилем, состоящую из счетчика эре- О мени, одновибратора и логических элементов. Распознавание сигна.пов в селекторах происходит по принципу счета импульсов опорной частоты в течение времени наличия огибающей входно-15 го сигнала 1 .

Недостатком таких селекторов является возможность ложного срабатывания и ограничения возможности селекции сигналов только одной фикси- 20 рованной длительности.

Известен также селектор, содержащий входной логический элемент И, один вход которого соединен с выходом генератора опорных импульсов, второй 25 вход соединен со входной клеммой,третий вход соединен с выходом RS-триггера, а выход соединен с суммируквдим входом счетчика, установочный вход которого соединен со входом RS-триг- 30

гера и через формирователь фронта сигнала и входной инвертор со входом селектора, а выход через формирователь стробирующих импульсов соединен со вторым входом RS-триггера и входом выходного логического элемента И, второй вход которого через формирователь среза входного сигнала и входной инвертор соединен с входной клеммой 2 .

Недостатком такого селектора является его одноканальность, т.е. ограничение возможности селектирования сигналов, поступакхдих из канала связи на вход селектора только одной фиксированной длительности.

Цель изобретения - расширение функциональных возможностей селектора, т.е. по распознаванию и разделению по соответствующим каналам из принятой смеси сигналов импульсов, кратных порциальной длительности дС, т.е. импульсов с длительностью , где К 1, 2, 3,..., К упричем минимальная длительность принимаемого сигнала может быть равна ut, а максимальнаяЦ ду Кгуи х-Лг;.

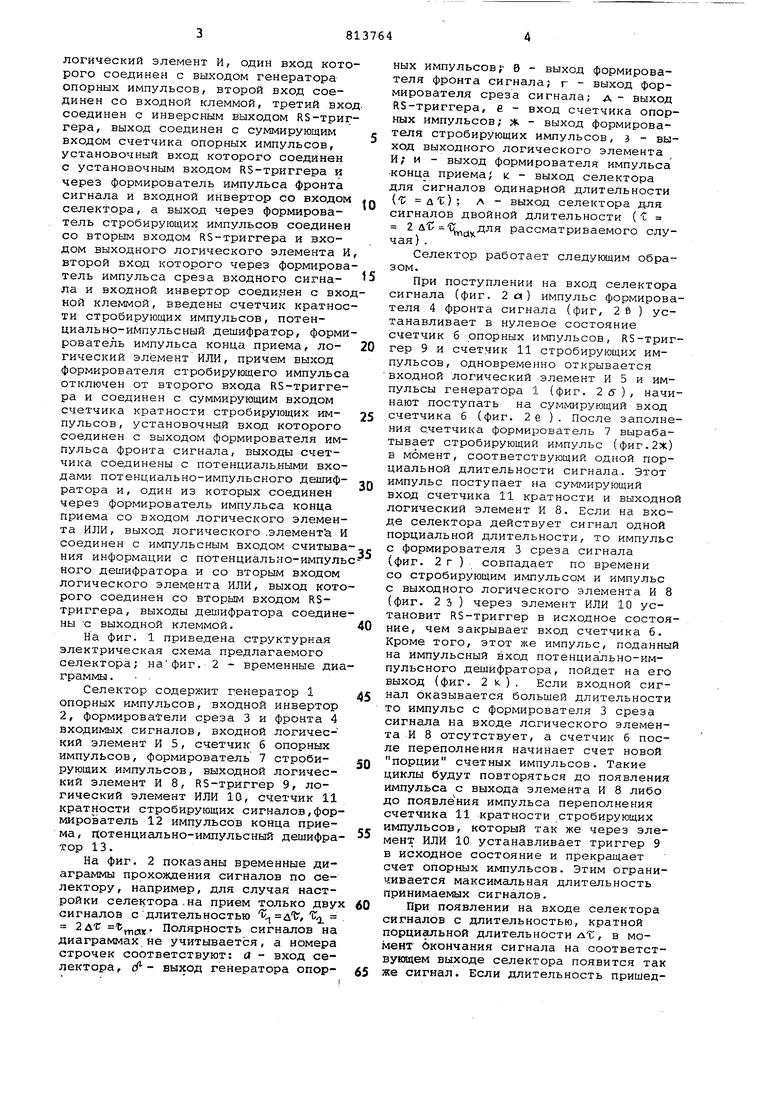

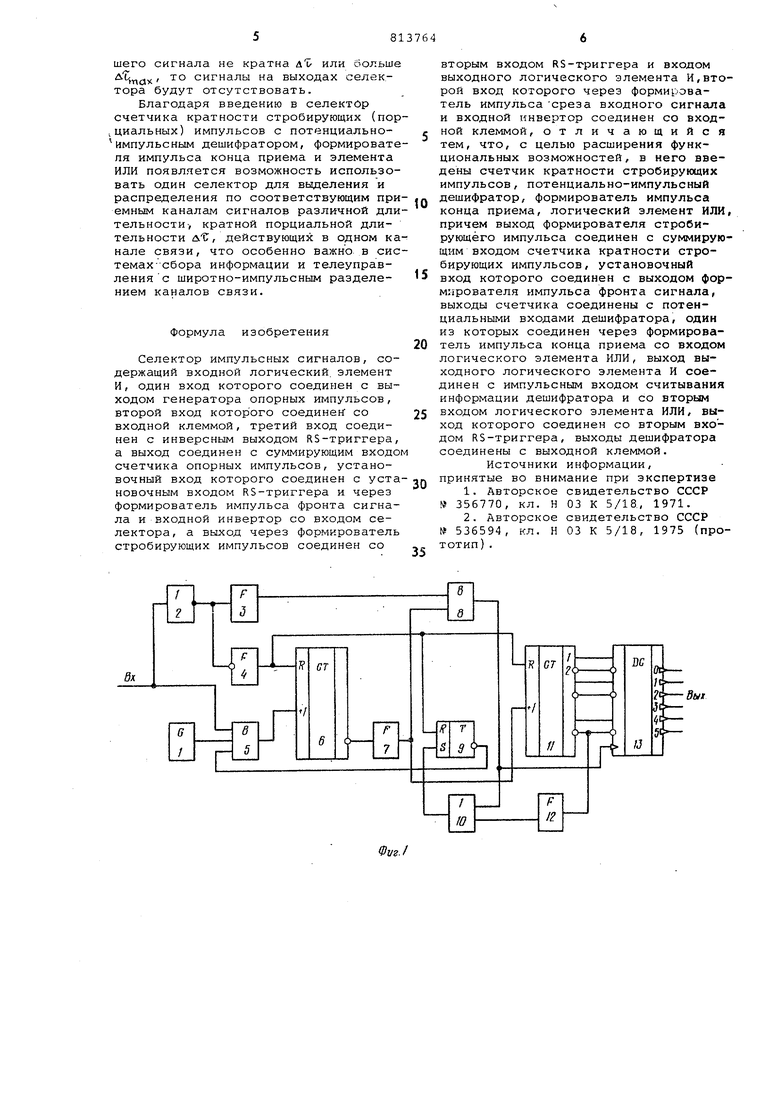

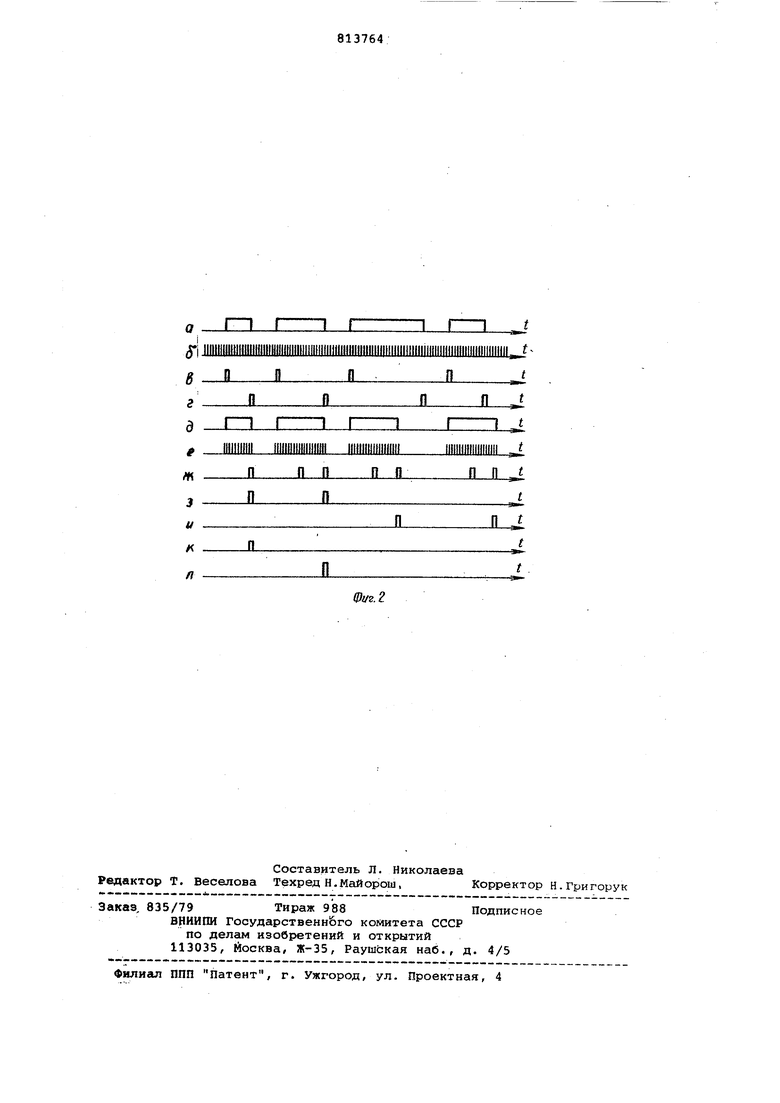

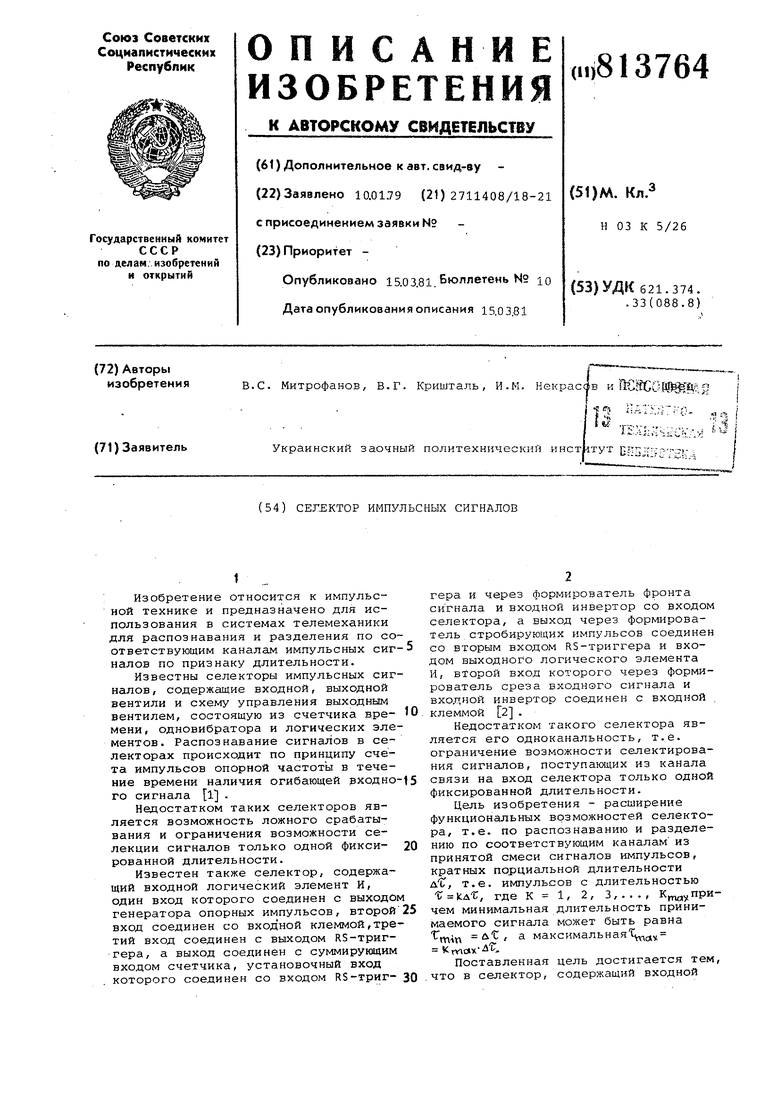

Поставленная цель достигается тем .что в селектор, содержащий входной логический элемент И, один вход кото рого соединен с выходом генератора опорных импульсов, второй вход соединен со входной клеммой, третий вхо соединен с инверсным выходом RS-триг гера, выход соединен с суммирующим входом счетчика опорных импульсов, установочный вход которого соединен с установочным входом RS-триггера и через формирователь импульса фронта сигнала и входной инвертор со входом селектора, а выход через формирователь стробирующих импульсов соединен со вторым входом RS-триггера и входом выходного логического элемента И второй вход которого через тель импульса среза входного сигнала и входной инвертор соединен с вхо ной клеммой, введены счетчик кратнос ти стробирующих импульсов, потенциально-импульсный дешифратор, форми рователь импульса конца приема, логический элемент ИЛИ, причем выход формирователя стробирующего импульса отключен от второго входа RS-триггера и соединен с суммирующим входом счетчика кратности стробирующих импульсов, установочный вход которого соединен с выходом формирователя импульса фронта сигнала, выходы счетчика соединены с потенциальными входами потенциально-импульсного дешифратора и, один из которых соединен через формирователь импульса конца приема со входом логического элемента ИЛИ, выход логического .элемента И соединен с импульсным входом считыва ния информации с потенциально-импуль ного дешифратора и со вторым входом логического элемента ИЛИ, выход кото рого соединен со вторым входом RSтриггера, выходы дешифратора соедине ны С выходной клеммой. На фиг. 1 приведена структурная электрическая схема предлагаемого селектора; нафиг. 2 - временные диа граммы . Селектор содержит генератор 1 опорных импульсов, входной инвертор 2, формирователи среза 3 и фронта 4 входимых сигналов, входной логический элемент И 5, счетчик б опорных импульсов, формирователь 7 стробирующих импульсов, выходной логический элемент И 8, RS-триггер 9, логический элемент ИЛИ 10, счетчик 11 кратности стробирующих сигналов,формирователь 12 импульсов конца приема. Потенциально-импульсный дешифратор 13. На фиг. 2 показаны временные диаграммы прохождения сигналов по селектору, например, для случая настройки селектора.на прием только двух сигналов сдлительностью 1-,д&, % . Полярность сигналов на диаграммах не учитывается, а номера строчек соответствуют: d - вход селектора, ( - выход генератора опорных импульсов } в - выход формирователя фронта сигнала; г - выход формирователя среза сигнала; А - выход RS-триггера, е - вход счетчика опорных импульсов; ;. - выход формирователя стробирующих импульсов, 3 - выход выходного логического элемента И/ и - выход формирователя импульса конца приема; к - выход селектора для сигналов одинарной длительности ( -&. л - выход селектора для сигналов двойной длительности (1 2 дС . рассматриваемого случая) . Селектор работает следующим образом. При поступлении на вход селектора сигнала (фиг. 2 а) импульс формирователя 4 фронта сигнала (фиг, 2 В ) устанавливает в нулевое состояние счетчик б опорных импульсов, RS-триггер 9 и счетчик 11 стробирующих импульсов, одновременно открывается входной логический элемент и 5 и импульсы генератора 1 (фиг. 2б), начинают поступать на суммирующий вход счетчика 6 (фиг. 2е ). После заполнения с.четчика формирователь 7 вырабатывает стробирующий импульс (фиг.2ж) в момент, соответствующий одной порциальной длительности сигнала. Этот импульс поступает на суммирующий вход счетчика 11 кратности и выходной логический элемент И 8. Если на входе селектора действует сигнал одной порциальной длительности, то импульс с формирователя 3 среза сигнала (фиг. 2 г ). совпадает по времени со стробирующим импульсом и импульс с выходного логического элемента И 8 (фиг. 2 ъ ) через элемент ИЛИ 10 установит RS-триггер в исходное состояние, чем закрывает вход счетчика 6. Кроме того, этот же импульс, поданный на импульсный вход потенциально-импульсного дешифратора, пойдет на его выход (фиг. 2 к ). Если входной сигнал оказывается большей длительности то импульс с формирователя 3 среза сигнала на входе логического элемента И 8 отсутствует, а счетчик 6 после переполнения начинает счет новой порции счетных импульсов. Такие циклы будут повторяться до появления импульса с выхода элемента И 8 либо до появления импульса переполнения счетчика 11 кратности стробирующих импульсов, который так же через элемент ИЛИ 10 устанавливает триггер 9 в исходное состояние и прекращает счет опорных импульсов. Этим ограничивается максимальная длительность принимаемых сигналов. При появлении на входе селектора сигналов с длительностью, кратной порциальной длительности .at;, в момент Окончания сигнала на соответствующем выходе селектора появится так же сигнал. Если длительность пришедшего сигнала не кратна ди или больш Нпсзх сигналы на выходах селектора будут отсутствовать. Благодаря введению в селектор счетчика кратности стробирующих (по циальных) импульсов с потенциально Импульсным дешифратором, формироват ля импульса конца приема и элемента ИЛИ появляется возможность использо вать один селектор для вьвделения и распределения по соответствующим пр емным каналам сигналов различной дл тельности-, кратной порциальной длительности , действующих в одном к нале связи, что особенно важно в си темах сбора информации и телеуправления с широтно-импульснвлм разделением каналов связи. Формула изобретения Селектор импульсных сигналов, содержащий входной логический, элемент И, один вход которого соединен с выходом генератора опорных импульсов, второй вход которого соединен со входной клеммой, третий вход соединен с инверсным выходом RS-триггера а выход соединен с суммирующим входо счетчика опорных импульсов, установочный вход которого соединен с уста ковочным входом RS-триггера и через формирователь импульса фронта сигнала и входной инвертор со входом селектора, а выход через формирователь стробирующих импульсов соединен со вторым входом RS-т-риггера и входом выходного логического элемента И,второй вход которого через формирователь импульса среза входного сигнала и входной инвертор соединен со входной клеммой, отличающийся тем, что, с целью расширения функциональных возможностей, в него введены счетчик кратности стробирующих импульсов, потенциально-импульсный дещифратор, формирователь импульса конца приема, логический элемент ИЛИ, причем выход формирователя стробирующёго импульса соединен с суммирующим входом счетчика кратности стробирующих импульсов, установочный вход которого соединен с выходом формирователя импульса фронта сигнала, выходы счетчика соединены с потенциальными входами дешифратора, один из которых соединен через формирователь импульса конца приема со входом логического элемента ИЛИ, выход выходного логического элемента И соединен с импульсным входом считывания информации дешифратора и со вторым входом логического элемента ИЛИ, выход которого соединен со вторым входом RS-триггера, выходы дешифратора соединены с выходкой клеммой. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 356770, кл. Н 03 К 5/18, 1971. 2.Авторское свидетельство СССР № 536594, кл, Н 03 К 5/18, 1975 (прототип) .

а

(Г1 B-SL

ГП Г

1L

ЛП

JL

3JLJL

П П

| название | год | авторы | номер документа |

|---|---|---|---|

| Селектор импульсных сигналов | 1982 |

|

SU1058043A1 |

| Селектор импульсных сигналов | 1980 |

|

SU892694A2 |

| Селектор импульсов | 1979 |

|

SU815890A1 |

| Селектор импульсных сигналов | 1979 |

|

SU822336A1 |

| Селектор импульсов | 1981 |

|

SU961132A1 |

| Селектор импульсных сигналов | 1979 |

|

SU799123A2 |

| Логический пробник | 1987 |

|

SU1525636A1 |

| Селектор импульсов | 1980 |

|

SU875616A1 |

| Селектор импульсных сигналов | 1982 |

|

SU1058042A1 |

| Селектор сигналов по длительности | 1982 |

|

SU1064450A1 |

Авторы

Даты

1981-03-15—Публикация

1979-01-10—Подача