(54) ТРАНЗИСТОРНЫЙ ИНВЕРТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Двухтактный инвертор | 1978 |

|

SU748747A1 |

| Двухтактный инвертор | 1990 |

|

SU1746502A1 |

| ПОЛУПРОВОДНИКОВЫЙ ПУСКО-РЕГУЛИРУЮЩИЙ АППАРАТ ДЛЯ ПИТАНИЯ ГАЗОРАЗРЯДНЫХ ЛАМП | 1996 |

|

RU2103844C1 |

| Устройство для управления транзисторным инвертором | 1983 |

|

SU1124420A1 |

| Магнитно-транзисторный ключ | 1979 |

|

SU843234A1 |

| Преобразователь постоянного напряжения | 1990 |

|

SU1778889A1 |

| Нерегулируемый преобразователь постоянного напряжения | 1987 |

|

SU1467700A1 |

| Способ управления двухтактным инвертором | 1981 |

|

SU1014121A1 |

| Инвертор | 1979 |

|

SU845251A1 |

| Магнитно-транзисторный ключ | 1977 |

|

SU746935A1 |

1

Изобретение относится к электротехнике и может найти применение в системах преобразования электрической энергии, в частности в устройствах электропитания электронной или иной аппаратуры в электроприводе, в системах регулирования и автоматики

Известны устройства управления транзисторным инвертором, осуществлямхкие синхронизацию процесса переключения транзисторов короткими импульсами 1 , 2 .

Недостаток известных устройств их спожность. В первом устройстве это выражается в необходимости использования дополнительного трансформатора в цепи управления, а во втором - в усложении силового транс форматора, содержащего две обмотки обратной связи.

Известно устройство управления транзисторным инвертором, в котором параллельно база-эмиттерным переходам силовых транзисторов включены выходные цепи шунтирующих транзисторов, а их базы связаны с источником управляющего сигнала З.

Недостаток этого устройства состоит в необходимости значительной мощности сигнала управления, которым шунтирующие транзисторы должны быть открыты и способны пропустить ток, превышающий ток базы силовых транзисторов.

Наиболее близким по технической сущности к предложенному устройству является инвертор, выполненный по автогенёраторной схеме и содержащий силовые транзисторы, базы которых через токоорганичительные резисторы присоединены к обмотке положительной обратной связи, а коллекторы к первичным обмоткам силового транс форматора, вторичные обмотки которого подключены к выходным выводам, а также коммутирующий транзистор, коллектор которого через коммутирующие диоды связан с выводё1ми обмотки положительной обратной связи, а базас источником сигнала управления, и шунтирующие транзисторы, выходные цепи которых включены параллельно переходам база-эмиттер силовых транзисторов инвертора 4j.

Недостаток этого устройства - излишние потери мощности во время коммутационного процесса за счет удвоения тока обмотки полржительной обратной связи, а также необходимость

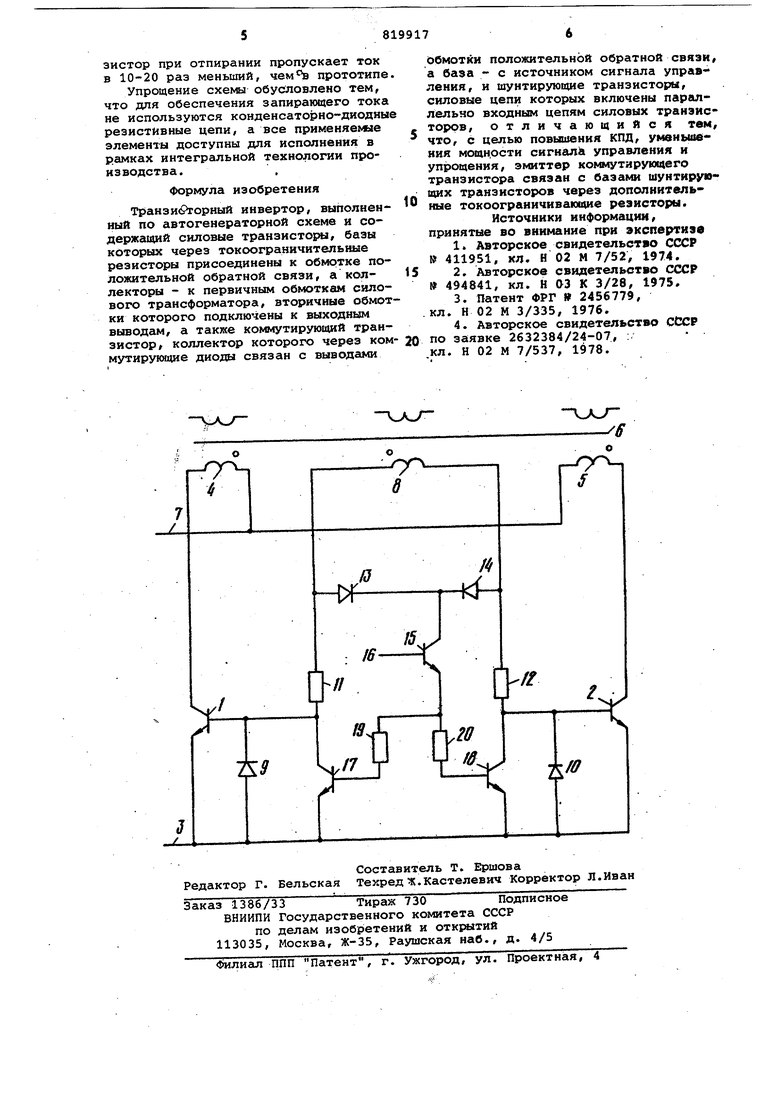

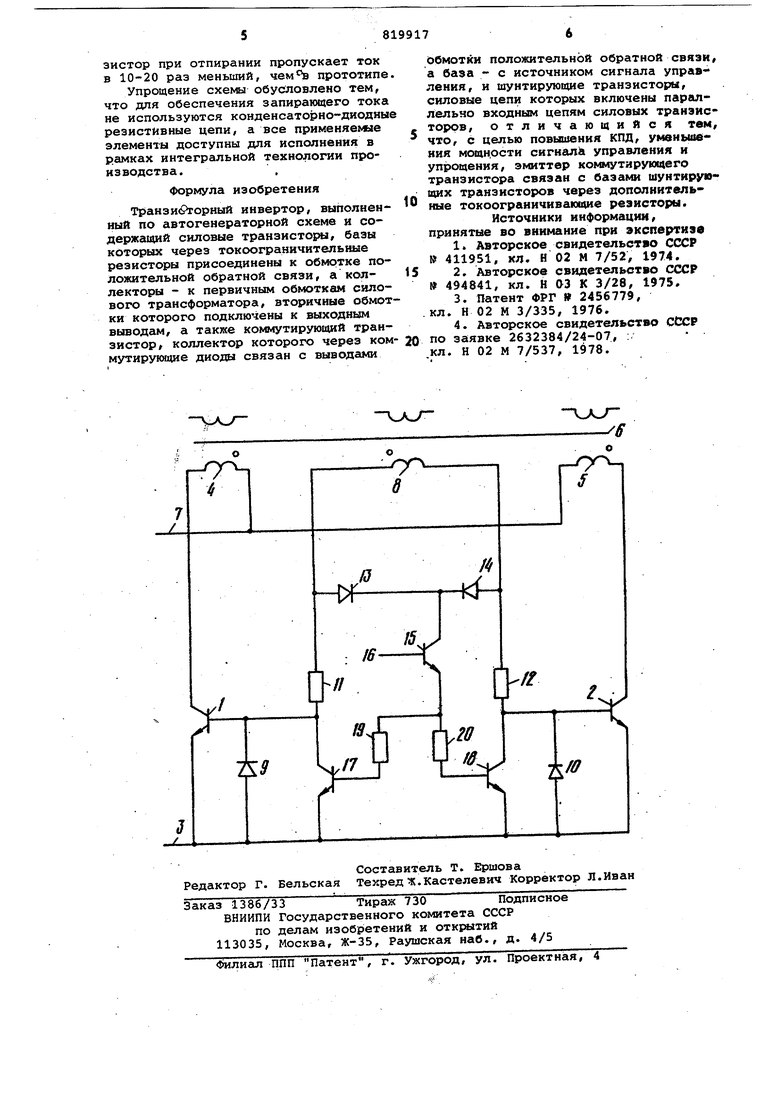

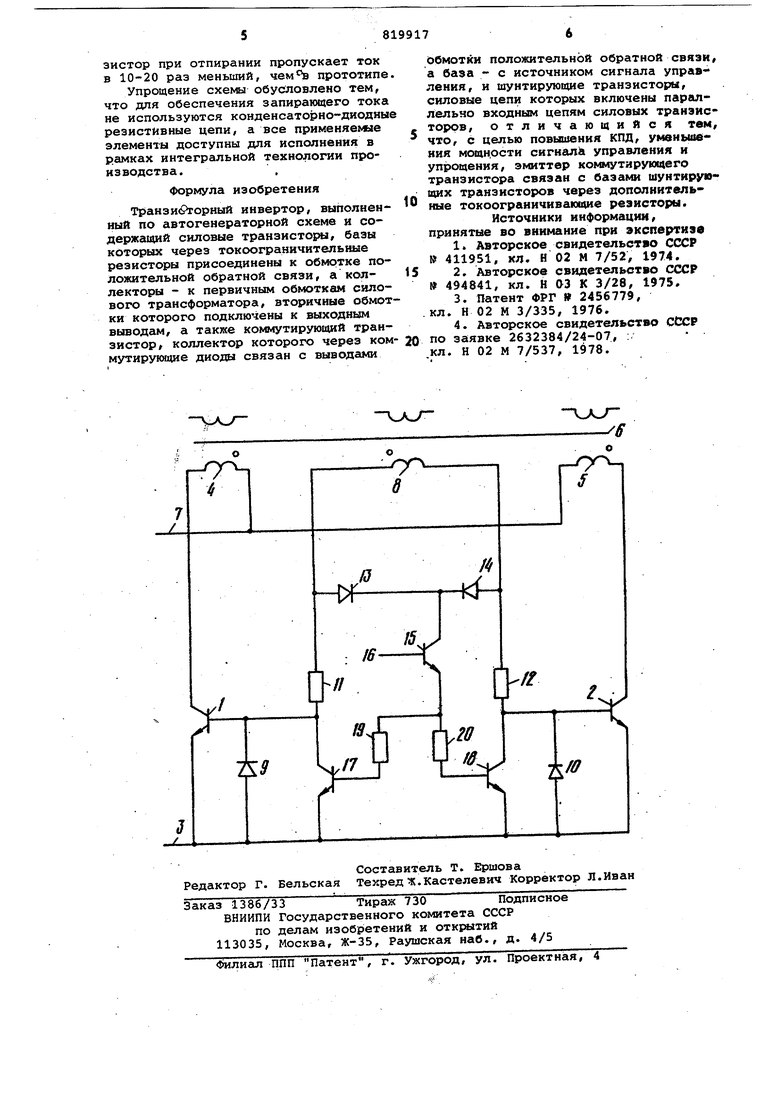

наличия значительной величины тока управления, так как этот ток должен обеспечить протекание по коллекторно цепи коммутирующего транзистора тока превьвиаклцего удвоенный ток обмотки по ожительнрй обратной связи. Цель изобретения - повьааение КПД уменьшение мощности сигнала управления и упрощение устройства. Это достигается тем, что в предложенном инверторе эмиттер коммутирующего транзистора связан с базами шунтирующих транзисторов через дополнительные токоограничивающие резисторы. На чертеже изображена электрическая схема устройства, где эмиттеры силовых транзисторов 1 и 2 соединены с первой шиной питания 3. Коллекторы этих транзисторов подключены через секции 4 и 5 первичной обмотки трансформатора 6 к второй шине п тания 7.Трансформатор 6 имеет обмот 8 положительной обратной связи и со купность вторичных обмоток, к которы подключены нагрузки. Параллельно база-эмиттерным переходам силовых транзисторов 1 и 2 включены шунтирующие диоды 9 и 10. Базы силовых транзисторов 1 и 2 соединены с выводами обмотки 8 положительной обратной связи через токоограничивающие резисторы 11 и 12. Выводы обмотки 8 через коммутирующие диоды 13 и 14 ёоединены с коллектором коммутирующего транзистора 15, база которого связана с источником 16 управлякмдего сигнала, а эмиттер связан с базами шунтирующих транзисторов 17 и 18 через дополнительные токоограничивакхцие резисторы 19 и 20. Выходные цепи шунтируикдах транзисторов 17 и 18 включены параллельно входным цепям силовых транзисторов 1 и 2. Принцип действия устройства управления силов(1ми транзисторами инвертора состоит в следующем. В проводящем состоянии, например находится силовой транзистор 1. Состояние насьнцения этог.о транзистора обеспечивается током обмотки 8 положительной обратной связи, протекающем через резисторы 11 и 12. За счет падения напряжения на шунтирующем диоде 10 силовой транзистор 2 поддерживается в режиме отсечки. Если сигналом управления отпирает ся коммутирующий транзистор 15, то ток через резистор 11 уменьшается за счет протекания части тока обмотки положительной обратной связи через коммутирующий диод 13 и коммутирующий транзистор 15. Половина тока коммутирующего транзистора через резистор 19 поступает в базу шунтирующего транзистора 17. Коллекторный ток этого транзистора обеспечивает отрицательный ток базы силового тран зистора 1, что вызывает форсирование режима запирания последнего. После прекращения действия управляющего сигнала отпирание силового транзистора 2 происходит током обмотки 8 положительной обратной связи за счет энергии, накопленной в трансформаторе б. Если управляющий импульс имеет длительность, превышакнцую время вывода накопленной энергии из трансформатора 6, то по окончании управляющего импульса отпирается силовой транзистор 1 током смещения, задавааNbiM в базу от источника питания, таким образом срывается генерация в автогенераторной схеме. В этом режиме ток источника сигнала, задаваекий в базовую цепь коммутирующего транзистора, не усиливается им и распределяется по входным цепям шунтирующих транзисторов 17 и 18. Эти транзисторы обеспечивают форсированное запирание силовых транзисторов, пока в схеме имеется генерация, и обеспечивают срыв генерации путем поддержания режима отсечки силовых транзисторов 1 и 2. Уменьшение потерь мощности в таком устройстве по сравнению с известным устройством - прототипом 4 обусловлено следую1г1ими причинами. Уменьшен ток цепи положительной обратной связи во время коммутационного процесса. В прототипе этот ток удваивается во время коммутационного процесса, а в данном устройстве управления он увеличивается только на величину токов базы шунтирующих транзисторов. Эти токи могут быть меньшими, чем ток цепи положительной обратной связи в 10-30 раз. , Отсутствуют потери в резисторах цепей запирания силовых транзисторов, ограничивакядих ток разряда конденсаторов этих цепей, имеющихся в известном усч ройстве. Отсутствует необходимость одновременного задания отпирающего тока по параллельным ветвям в базовые цепи коммутирующего и шунтирующих транзисторов, как в прототипе. Это также позволяет уменьшить мощность сигнала управления. РО время коммутационного процесса по мере уменьшения тока цепи положительной обратной связи автоматически уменьшается также и ток, задаваендлй в базовые цепи шунтирующих транзисторов. После запирания силовых транзисторов и вывода энергии из трансформатора э.тот ток снижается до уровня, определяемого величиной тока источника сигнала управления. Возможность уменьшения необходимой мощности сигнала„ управления обусловлено тем, чтб коммутирующий транэистор при отпирании пропускает ток в 10-20 раз меньший, чем прототипе

Упрощение схемы обусловлено тем, что для обеспечения запирающего тока не используются конденсаторно-диодны резистивные цепи, а все применяемые элементы доступны для исполнения в рамках интегральной технологии производства.

Формула изобретения

Транзи 9горный инвертор, выполнен ный по автогенераторной схеме и содержащий силовые транзисторы, базы которых через токоограничительные резисторы присоединены к обмотке положительной обратной связи, а коллекторы - к первичным обмоткам силового трансформатора, вторичные обмотки которого подключены к выходным выводам, а также коммутирующий транзистор, коллектор которого через ком мутирующие диода связан с выводами

Обмотки положительной обратной связи, а база - с источником сигнала управления, и шунтирующие транзисторы, силовые цепи которых включены параллельно входным цепям силовых транзисторов, отличающийся тем, что, с целью повышения КПД, уменьшения мощнрсти сигнгш управления и упрощения, эмиттер коммутирующего транзистора связан с базами шунтирующих транзисторов через дополнительные токоограиичивающие резисторы.

Источники информации, принятые во внимание при экспертизе

.кл. Н 02 М 7/537, 1978.

Авторы

Даты

1981-04-07—Публикация

1979-05-25—Подача