I

Изобретение относится к области контроля и измерений.

Известны логические тестеры, содержащие щуп, эмиттерный повторитель,, инвертор и элементы индикации I. Этому устройству свойственны узкие функциональные возможности.

Наиболее близким техническим решением к изобретению является логический тестер, содержащий щуп, который через основной элемент индикации соединен с входом эмиттерного повторителя, выход.которого через основной инвертор, а вход непосредственно подключены к входам элемента И-НЕ, выход которого соединен с входом интегрирующей цепочки 2.

Целью изобретения является расщирение функциональных возможностей логического тестера.

Достигается это за счет того, что в логическом тестере, содержащем шуп, который через основной элемент индикации соединен с входом эмиттерного повторителя, выход которого через основной инвертор, а вход непосредственно подключены к входам элемента И-НЕ, выход которого соединен С входом интегрирующей цепочки, введены стабилитрон, замыкающая кнопка установки, RS-триггеры на элементах И-НЕ, дополнительные элементы индикации и дополнительные инверторы и резистор, при этом стабилитрон включен между входом эмиттерного повторителя и общей щиной, а замыкающая кнопка установки - между точкой объединения нулевых входов RS-триггеров и общей шиной, причем единичный вход первого RS-триггера соединен с выходом интегрирующей цепочки, единичный выход через последовательно включенные первые дополнительные инвертор и элемент индикации соединен с плюсовой шиной источника питания, а, нулевой выход через второй дополнительный элемент индикации - с плюсовой щиной источника питания, единичный вход второго RS-триггера подключен к выходу основного инвертора, единичный выход через последовательно включенные второй дополнительный инвертор и третий дополнательный элемент индикации соединен с плюсовой шиной источника питания, а нулевой выход через четвертый дополнительный элемент индикации - с плюсовой шиной

источника питания, единичный вход третьего RS-триггера подключен ко входу эмиттерного повторителя, единичный выход через последовательно включенные третий дополнительный инвертор и пятый дополнительный элемент индикации соединен с плюсовой шиной источника питания, а нулевой выход через шестой дополнительный элемент индикации - с плюсовой шиной источника .питания, при этим точка объединения нулевых входов RS-триггеров через резистор соединена с плюсовой шиной источника питания.

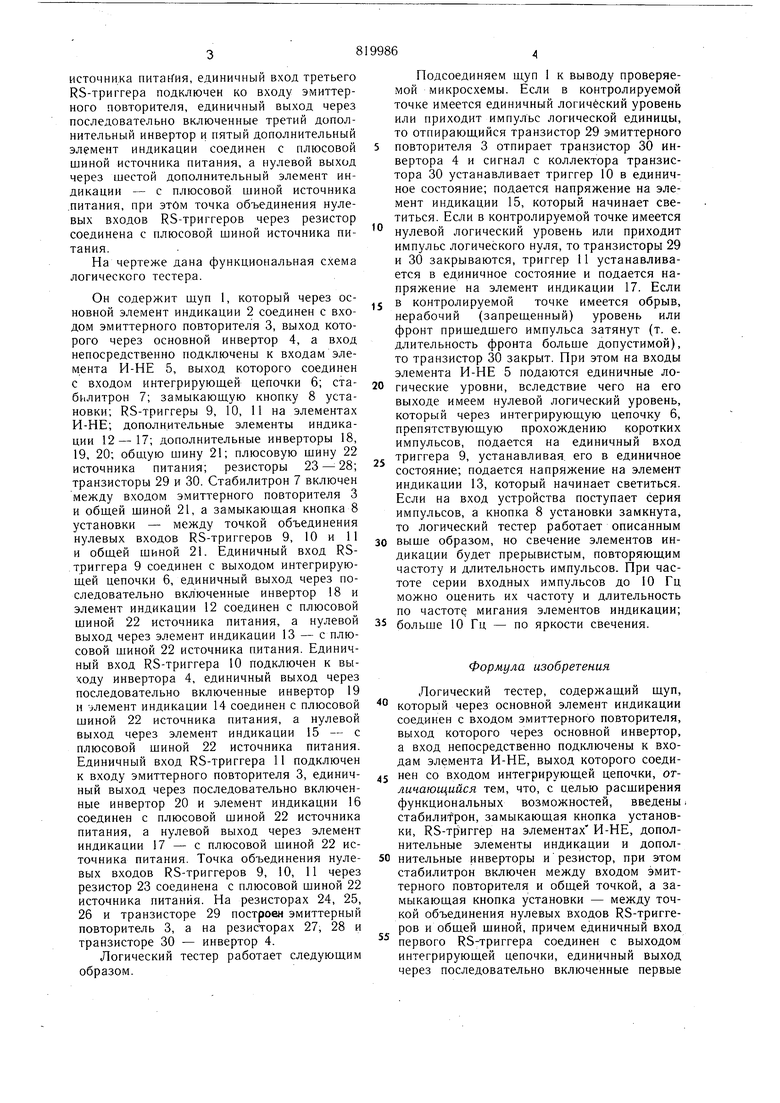

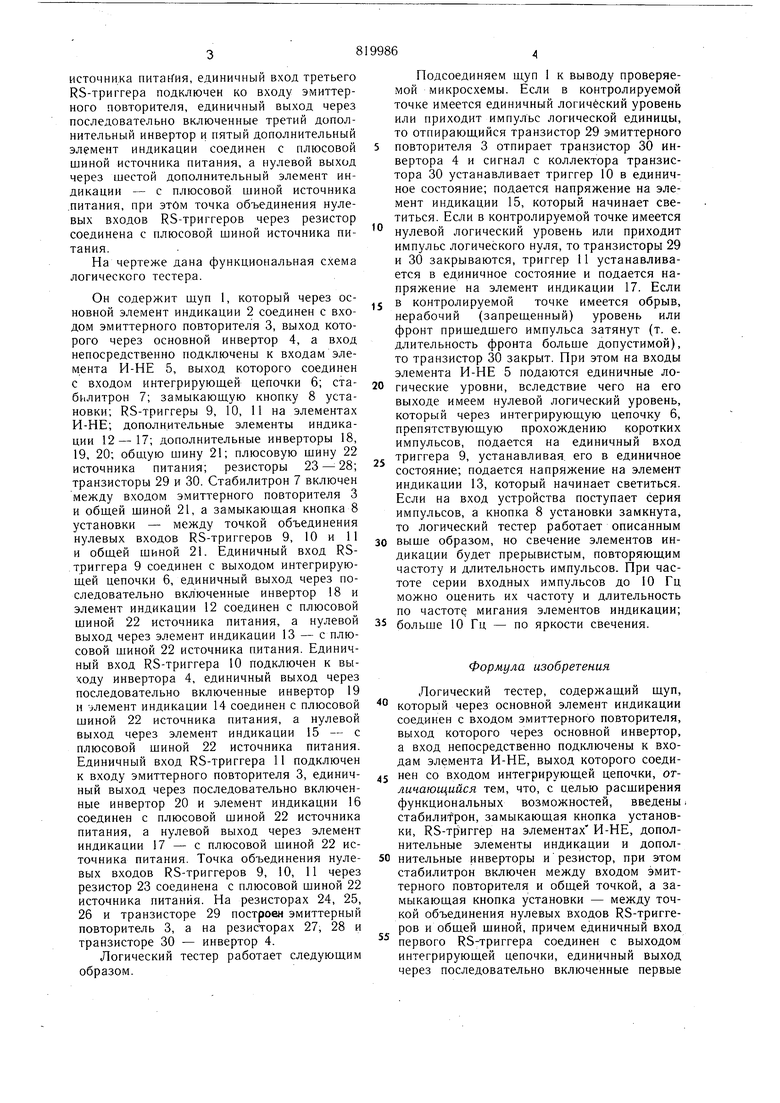

На чертеже дана функциональная схема логического тестера.

Он содержит щуп 1, который через основной элемент индикации 2 соединен с входом эмиттерного повторителя 3, выход которого через основной инвертор 4, а вход непосредственно подключены к входам элемента И-НЕ 5, выход которого соединен с входом интегрируюшей цепочки 6; стабилитрон 7; замыкающую кнопку 8 установки; RS-триггеры 9, 10, 11 на элементах И-НЕ; дополнительные элементы индикации 12 - 17; дополнительные инверторы 18, 19, 20; общую шину 21; плюсовую шину 22 источника питания; резисторы транзисторы 29 и 30. Стабилитрон 7 включен между входом эмиттерного повторителя 3 и общей щиной 21, а замыкающая кнопка 8 установки - между точкой объединения нулевых входов RS-триггеров 9, 10 и 11 и общей шиной 21. Единичный вход RSтриггера 9 соединен с выходом интегрирующей цепочки 6, единичный выход через последовательно включенные инвертор 18 и элемент индикации 12 соединен с плюсовой шиной 22 источника питания, а нулевой выход через элемент индикации 13 - с плюсовой шиной 22 источника питания. Единичный вход RS-триггера 10 подключен к выходу инвертора 4, единичный выход через последовательно включенные инвертор 19 и элемент индикации 14 соединен с плюсовой шиной 22 источника питания, а нулевой выход через элемент индикации 15 - с плюсовой шиной 22 источника питания. Единичный вход RS-триггера И подключен к входу эмиттерного повторителя 3, единичный выход через последовательно включенные инвертор 20 и элемент индикации 16 соединен с плюсовой шиной 22 источника питания, а нулевой выход через элемент индикации 17 - с плюсовой шиной 22 источника питания. Точка объединения нулевых входов RS-триггеров 9, 10, 11 через резистор 23 соединена с плюсовой шиной 22 источника питания. На резисторах 24, 25, 26 и транзисторе 29 построен эмиттерный повторитель 3, а на резисторах 27, 28 и транзисторе 30 - инвертор 4.

Логический тестер работает следующим образом.

Подсоединяем щуп 1 к выводу проверяемой микросхемы. Если в контролируемой точке имеется единичный логический уровень или приходит импульс логической единицы, то отпирающийся транзистор 29 эмиттерного

повторителя 3 отпирает транзистор 30 инвертора 4 и сигнал с коллектора транзистора 30 устанавливает триггер 10 в единичное состояние; подается напряжение на элемент индикации 15, который начинает светиться. Если в контролируемой точке имеется нулевой логический уровень или приходит импульс логического нуля, то транзисторы 29 и 30 закрываются, триггер 11 устанавливается в единичное состояние и подается напряжение на элемент индикации 17. Если

в контролируемой точке имеется обрыв, нерабочий (запрещенный) уровень или фронт прищедшего импульса затянут (т. е. длительность фронта больше допустимой), то транзистор 30 закрыт. При этом на входы элемента И-НЕ 5 подаются единичные логические уровни, вследствие чего на его выходе имеем нулевой логический уровень, который через интегрирующую цепочку 6, препятствующую прохождению коротких импульсов, подается на единичный вход

. триггера 9, устанавливая его в единичное состояние; подается напряжение на элемент индикации 13, который начинает светиться. Если на вход устройства поступает серия импульсов, а кнопка 8 установки замкнута, то логический тестер работает описанным

0 выше образом, но свечение элементов индикации будет прерывистым, повторяющим частоту и длительность импульсов. При частоте серии входных импульсов до 10 Гц можно оценить их частоту и длительность по частоте мигания элементов индикации;

5 больше 10 Гц - по яркости свечения.

Формула изобретения

Логический тестер, содержащий щуп, который через основной элемент индикации соединен с входом эмиттерного повторителя, выход которого через основной инвертор, а вход непосредственно подключены к входам элемента И-НЕ, выход которого соединен со входом интегрирующей цепочки, отличающийся тем, что, с целью расщирения функциональных возможностей, введены i cтaбилиfpoн, замыкающая кнопка установки, RS-триггер на элементах И-НЕ, дополнительные элементы индикации и дополнительные инверторы и резистор, при этом стабилитрон включен между входом эмиттерного повторителя и общей точкой, а замыкающая кнопка установки - между точкой объединения нулевых входов RS-триггеров и общей шиной, причем единичный вход первого RS-триггера соединен с выходом интегрирующей цепочки, единичный выход через последовательно включенные первые

дополнительные инвертор и элемент индикации соединен с плюсовой шииой источника питания, а нулевой выход через второй дополнительный элемент индикации - с плюсовой шиной источника питания, единичный вход второго RS-триггера подключен к выходу основного инвертора, единичный выход через последовательно включенные второй дополнительный инвертор и третий дополнительный элемент индикации соединен с плюсовой шиной источника питания, а нулевой выход через четвертый дoпoлниJ тельный элемент индикации - с плюсовой шиной источника питания, единичный вход третьего RS-триггера подключен к входу эмиттерного повторителя, единичный выход через последовательно включенные третий

дополнительный инвертор и пятый дополнительный элемент индикации соединен с плюсовой шиной источника питания, а Kyj левой выход через шестой дополнительный элемент индикации - с плюсовой шиной источника питания, при этом точка объединения нулевых входов Rb-триггеров через резистор соединена с плюсовой шиной источника питания.

Источники информации, принятые во внимание при экспертизе 1. Быданов В. и др. Испытатель логических устройств , «Радио, № И, 1977,

с. 28.

2 Назаров Н., Логический тестер. «Радно, № 9, 1976, с. 46. рис. 1 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| ЛОГИЧЕСКИЙ ТЕСТЕР | 1997 |

|

RU2133475C1 |

| Согласующее устройство | 1977 |

|

SU660213A1 |

| Генератор импульсных сигналов | 1981 |

|

SU980026A1 |

| Логический пробник | 1990 |

|

SU1839242A1 |

| Электронная приставка к транзисторной системе зажигания | 1991 |

|

SU1800086A1 |

| Логический зонд | 1980 |

|

SU911734A2 |

| Формирователь импульсов | 1980 |

|

SU886225A1 |

| Бесконтактное поляризованное реле | 1981 |

|

SU972663A1 |

| Устройство для контроля и диагностики цифровых устройств | 1988 |

|

SU1583886A2 |

| ЭНЕРГОСБЕРЕГАЮЩЕЕ УСТРОЙСТВО ЭЛЕКТРОСНАБЖЕНИЯ (КВАРТИРЫ, ДОМА, ПОМЕСТЬЯ) С ДИСТАНЦИОННЫМ УПРАВЛЕНИЕМ | 2008 |

|

RU2409825C2 |

Авторы

Даты

1981-04-07—Публикация

1979-01-04—Подача