(54) УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ АНАЛОГОВЫХ СИГНАЛОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления аналоговых сигналов | 1978 |

|

SU752367A1 |

| Логарифмический преобразователь | 1979 |

|

SU877570A2 |

| Устройство для получения попарных произведений нескольких сигналов | 1978 |

|

SU767781A1 |

| Логарифмический преобразователь | 1970 |

|

SU868785A2 |

| Логарифмический преобразователь | 1978 |

|

SU752372A1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОЙ НАСТРОЙКИ КОЛЕБАТЕЛЬНОГО КОНТУРА УСИЛИТЕЛЯ МОЩНОСТИ | 1990 |

|

RU2017327C1 |

| Устройство для измерения параметров резонансных контуров | 1982 |

|

SU1071972A1 |

| Многоканальный имитатор канала магнитной записи | 1990 |

|

SU1767529A1 |

| Двухчастотный измеритель погрешностей делителей напряжения | 1980 |

|

SU918911A1 |

| УСТРОЙСТВО ДЛЯ СОЗДАНИЯ ПРИЦЕЛЬНЫХ ПОМЕХ РАДИОЛОКАЦИОННЫМ СТАНЦИЯМ | 2006 |

|

RU2329603C2 |

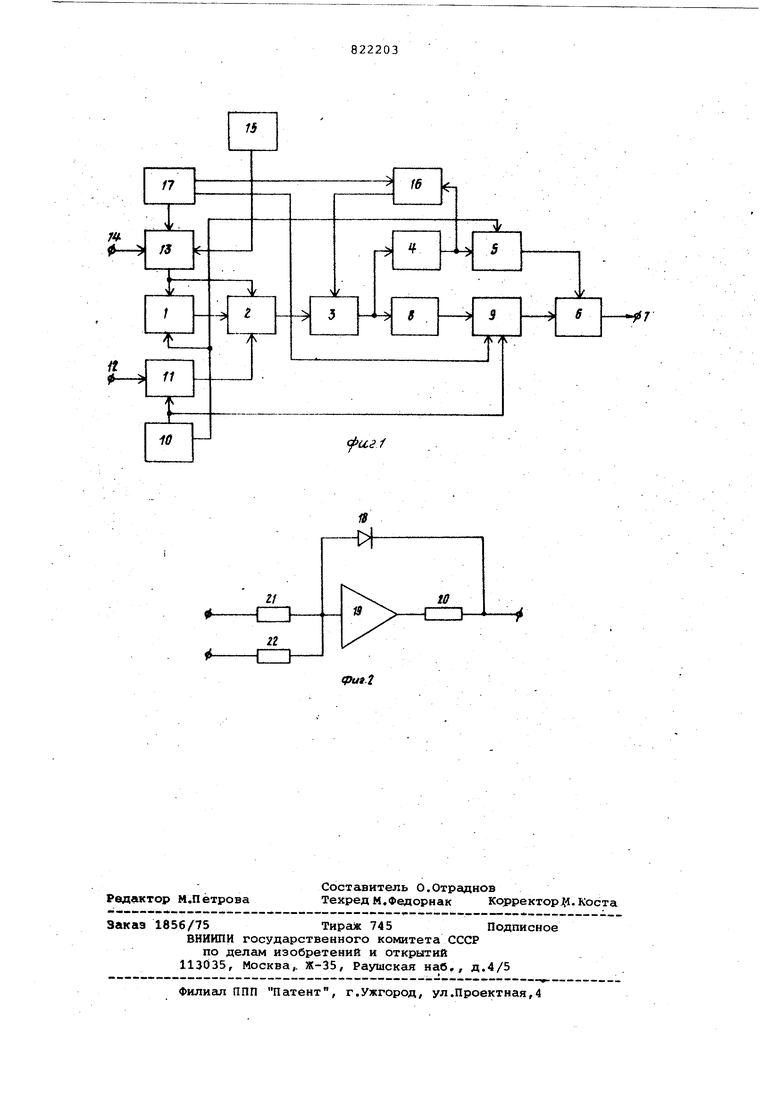

Изобретение относится к электрическим вычислительным устройствам и может быть использовано в аналоговых вычислительных меииинах. Известно устройствЬ деления анало говых сиг напов, содержащее cyfrMaTop, логарифмические преобразователи, бло ки вычитания, фильтр Т . Однако это устройство обладает. низкой точностью работы. Наиболее близким к предлагаемому является устройство деления аналоговых сигналов, содержащее соединенные последовательно балансный амплитудный модулятор, сумматор, логарифмический преобразователь, первый полосовой усилитель, первый синхронный детектор и блок автоматической регулировки усиления, выход которого яеляется выходом устройства, соеданенные последовательно второй полосово усилитель и второй синхронный детектор, генератор гармонических колебаний, первый выход которого подключен к управляющему входу первого синхрон jHoro детектора и первому вxoдif балан ного гилплитудного модулятора, второйвыход генератора гармонических коле баний присоединен к управлякщему вход второго синхронного детектора и первому входу дополнительного балансного амплитудного модулятора, выход которого соединен со вторым входом сУмматора, второй вход дополнительного балансного амплитудного модулятора подключен ко входу делимого устройст-, на, выход второго синхронного детектора присоединен ко второму входу блока автоматической регулировки усиления, второй вход балансного амплитуд- ного модулятора соединен с третьим входом сумматора, входы первого и второго полосовых усилителей объединены 2 . Недостатком данного устройства является невысокс1Я точность работы вследствие нестабильности логарифмического преобразователя на начальном участке квазилогарифмической характеристики при изменении окружающей температуры. Цель изобретения - повышение точности работы путем коррекции формы характеристики логарифмического преобразователя в зависимости от уровня сигнала-делителя. Поставленная цель достигается тем, что в устройство введены коммутатор, синхронный детектор огибающей,генератор коммутирующих импульсов и источник постоянного напряжения,причем сигнальный вход синхронного детектора огибающей соединен с выходом первого полосового усилителя, выход синхро-нного детектора огибающей подключен к управляющему входу логарифмического преобразователя, первый вход коммутатора соединен со входом делителя уст ройства, ко второму входу коммутатор присоединен выход источника постоянного напряжения,выход коммутатора подключен ко второму входу балансного амплитудного модулятора, управляющий вход коммутатора соединен с первым вы ходом генератора коммут 1руклцих импульсов, второй и третий выходы кото рого подключены к управляющим входам синхронного детектора огибающей и вто рого синхронного детектора соответст венно, а также тем, что логарифмичес кий преобразователь содержит операционный усилитель, к инвертирукицему входу которого подключен .анод логарифмирующего диода, катод ко- орого является выходом логарифмического пр образователя, и через токозадающяй резистор соединен с выходом операционного усилителя, инвертирующий вход которого через первый и второй масштабные резисторы подключен к сигнальному и управл5Пощему входам ло гарифмического преобразователя соответственно. На фиг.1 изображена функциональная схема предлагаемого устройства деления аналоговых сигналов,на фиг.2 структурная схема логарифмического преобразователя. Устройство содержит (фиг.1) (балансный, амплитудный модулятор 1, сумматор 2, логарифмический преобразователь 3, первый полосовой усилитель 4, первый синхронный детектор 5, блок 6 автоматической регулировки усиления, выход 7 устройства, второй полосовой усилитель 8, второй синхронный детектор 9, генератор 10 гармонических колебаний, дополнитель ный балансный амплитудный модулятор 11, вход 12 делимого устройства, ком мутатор 13, вход 14 делителя устройства, источник 15 постоянного напряжения, синхронный детектор 16 огибающей, генератор 17 коюнутирующих импульсов (фиг.1}В логарифмический преобразователь (фиг.2) входит логарифмирующий диод 18, операционный усилитель 19, токозадающий резистор 20, масштабные резисторы 21 и 22. Устройство деления аналоговых сигналов работает следующим образом На вход логарифмического преобра.зователя 3 поступает напряжение UexWUoli) К„ид„ЫпU),l4«,UoWsincoji, И) де К. , К - коэффициенты передачи балансного амплитудного модулятора 1 и дополнительного балансного амплитудного модулятора 11; (д)., частоты несущих генератора гармонических колебаний 10, которые модулируются соответственно балансным амплитудным модулятором 1 и дополнительным балансным амплитудным модулятором 11; напряжение сигнала-делимого. ,T tir+ isnpH| t T, ДА напряжение сигнала-делите- U,g - напряжение источника 15 постоянного напряжения; Т - период повторения сигнала генератора 17 коммутирующих импульсов. Переменная составлякяцая на выходе огарифмического преобразователя 3 содержит следующие составляющие: H(t),(U4Jsinco,t при , + X ((Ог1приО 1 Т 7 1 т+ (4) Ч1-,,(,)21при|Д Т,,(б) где (- термический потенцигш логарифмирукнцего диода; М(1).,д)- отношение производных квазилогарифмической и логарифмической характеристик при значении Уд м(и,5) - то же при значении, и,, й«1плитуда составляющей (3) выделяется на выходе второго полосового усилителя 8, а составляющие (4) ij(5)на выходе первого полосового усилителя 4 . Разность амплитуд составлякяцих (4) и (5), соответствующих напряжению сигнала-делителя и напряжению источ ника 15 постоянного напряжения, выделяется синхронным детектором 16 огибагацей и используется в качестве смещения логарифмического преоб7 разов ателя 3 р1Я коррекции формы его характеристики. Эта коррекция приводит к тому, что величины M(UA.) и MdJjg) отличаются друг от друга намайую величину, т.е. обеспечивается необходимая протяженность логарифмического участка характеристики логарифмического преобразователя 3. . На выходе второго синхронного детектора 9 выделяется напряжение, прямо пропорциональное напряжению, определяемым соотношением (3)/ а на выходе первого синхронного детектора 5 - напряжение, определяемое соотношениями (6) и (7). Блок автоматической регулировки усиления 6 изменяет свое усиление обратно пропорционально его входным сигналам.В результате напряжени на выходе 7 устройства может быть . сделано независящим от температуры и дрейфа операционного.усилителя. Таким образом, преимущество устройства деления аналоговых сигна лов заключается в повышении точност работы, что обусловлено использован ем коррекции характеристики логариф мического преобразователя 3. В резу льтате появляется возможность работы при. входных напряжениях сигналаделителя на один-два порядка меньше чем в известном устройстве,так как уменьшены искажения формы начальног участка характеристик логарифмичеср ого преобразователя 3. Формула изобретения 1. Устройство для деления аналоговых сигналов, содержащее соединенные последовательно балансный амплитудный модулятор, сумматор, логарифмический преобразователь, первый полосовой усилитель, первый синхронный детектор и блок автоматической регулировки усиления, выход которого ,является выходом устройства, соединенные последовательно второй полосовой усилитель и второй синхронный детектор, генератор гармонических колебаний, первый выход которого подключен к управляющему входу перво го синхронного детектора и первому входу балансного амплитудного модулятора, второй выход генератора гармонических колебаний, присоединен к управляющему входу второго синхронного детектора и дервому входу допол нительного балансного амплитудного модулятора, выход которого соединен со вторым входом сумматора, второй вход дополнительного балансного амплитудного модулятора подключен ко входу де7№1мого устройства, выход второго синхронного детектора присое динен ко второму входу блока автоматической регулировки усиления, второй вход балансного амплитудного модулятора соединен с третьим входом сумматора, входы первого и второго полосовых усилителей объединены, о тличающееся тем, что, с с целью повышения точности работы, в него введены коммутатор, синхронный детектор огибающей, генератор комму-. тирующих импульсов и источник постоянного напряжения, причем сигнальный вход синхронного детектора огибающей соединен с -выходом первого полосового усилителя, выход синхронного детектора огибающей подключен к управляющему входу логарифмического преобразователя, первый вход коммутатора соединен со входом делителя устройства, ко второму входу коммутатора присоединен выход источника постоянного напряжения, выход коммутатора подключен ко второму входу балансного амплитудного модулятора, управляющий вход коммутатора соединен с первым выходом генератора коммутирующих импульсов, второй и третий выходы которого подключены к управляющим входам синхронного детектора огибающей и второго синхронного детектора соответственно. 2. Устройство по П.1, отли ч а ю щ е е с я тем, что логарифмический преобразователь содержит операционный усилитель, к инвертирующему входу которого подключен анод логарифмирующего диода, катод которого является выходом логарифмического преобразователя и через токозадающий резистор соединен с выходом операционного усилителя, инвертирукщий вход которого через первый и второй масштабные резисторы подключен к сигнальному и управляющему входам лог рифмического преобразователя соответственно. Источники информации, принятые во внимание при экспертиз-е 1.Патент Франции 2138206, кл.С Об G 7/00,.г опублик.1973. 2.Авторское свидетельство СССР по заявке № 2651450/18-24, кл. G 06 G 7/16, 25.01.79.

Авторы

Даты

1981-04-15—Публикация

1979-06-11—Подача