1

Изобретение относится к вычислительной технике и может быть применено в аналоговых счетно-решающих устройствах.

Известно устройство, являющееся сумматором четырех переменных, представленных 5-ю разрядами позиционного двоичного кода, содержащее обратиNwe операционные усилители по числу разрядов Машинных переменных, блок сброса, блок регистрации переполнения и блоки переноса. Каждый обратимый операционный усилитель состоит из усилителя постоянного тока с большим коэффициентом усиления и пяти вспомогательных резисторов l.

Недостатком этого устройства является ограниченное быстродействие объясняемое необходимостью формирования сигналов переноса.

Наиболее близким техническим решением по технической сущности и достигаемому результату к предлагаемому является устройство, содерж

щее блок переноса, операционный усилитель, функциональный преобразователь. К потенциально-нулевой точке операционного усилителя подсоединены h основных резисторов, а к выходу подключены п вспомогательных резисторов. Входы функционального преобразователя ёоединелы с основными , и через переключатели - с вспвмогатапьными резисторами. Выход преобразователя подключен через допол ительный резистор к потенциальнонулевой точке усилителя и непосредственно к входу блока переноса fz.

Недостаток этого устройства - ограниченные функциональные возможности, заключающиеся в однонаправленности прохождения информации и невозможности работы с непозипионными кодами, например, в системе octaточных классов.

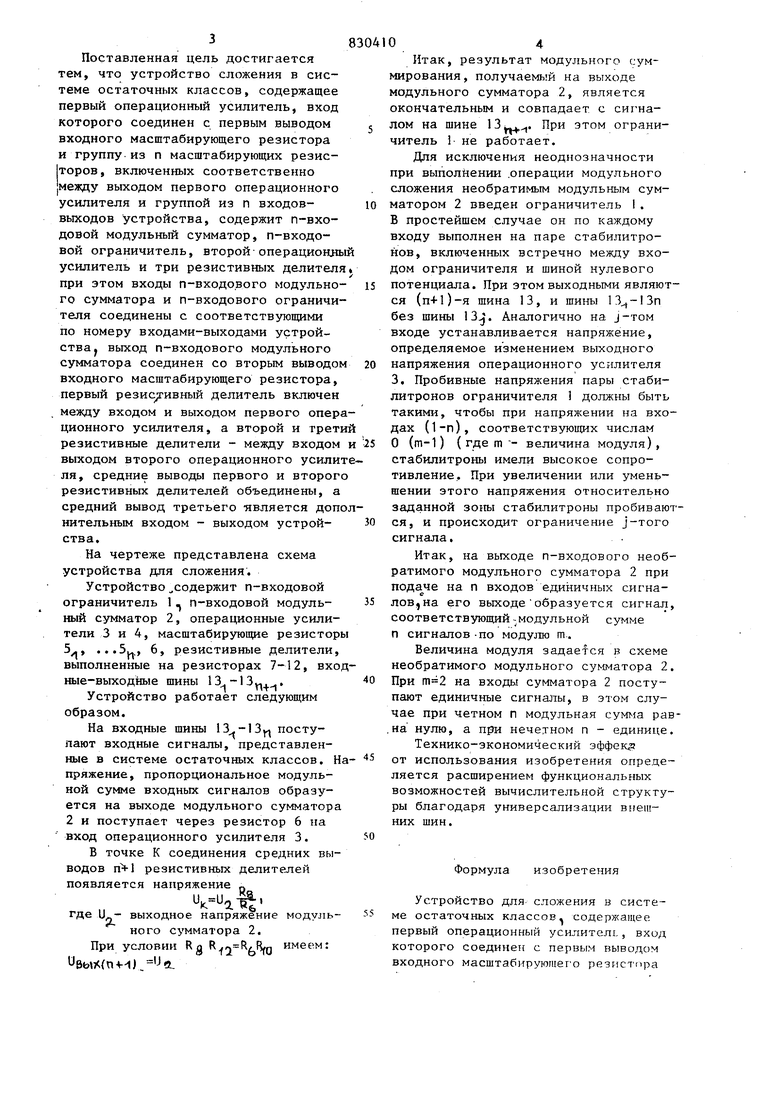

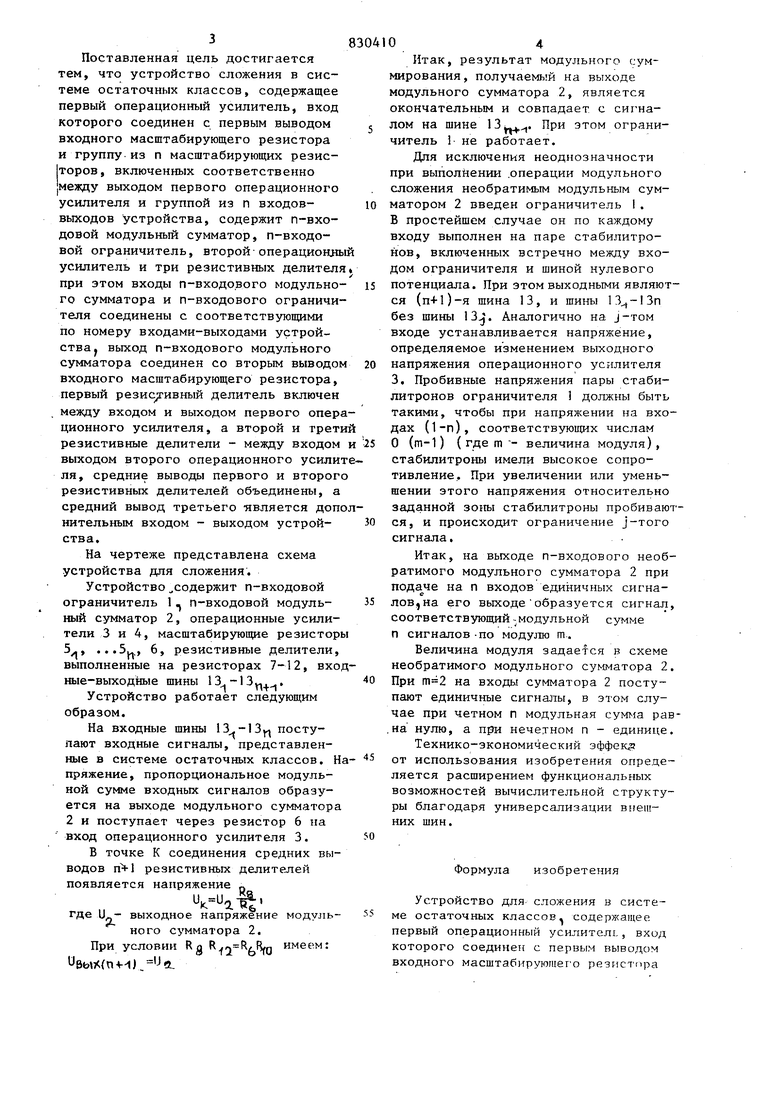

Цель изобретения - расширение функциональных вoз foжнocтcй путем обеспечения обрат11г ост11 г.. Поставленная цель достигается тем, что устройство сложения в системе остаточных классов, содержащее первый операционный усилитель, вход которого соединен с первым выводом входного масштабирующего резистора и группу-из п масштабирующих резисторов, включенных соответственно меяоду выходом первого операционного усилителя и группой из п входоввыходов устройства, содержит п-входовой модульный сумматор, п-входовой ограничитель, второй-операционны усилитель и три резистивных делител при этом входы п-входового модульно го сумматора и п-входового ограничи теля соединены с соответствующими по номеру входами-выходами устройства выход п-входового модульного сумматора соединен со вторым выводо входного масштабирующего резистора, первый резис ивный делитель включен между входом и выходом первого опер ционного усилителя, а второй и трет резистивные делители - между входом выходом второго операционного усили ля, средние выводы первого и второг резистивных делителей объединены, а средний вывод третьего является доп нительным входом - выходом устройства. На чертеже представлена схема устройства для сложения. Устройство содержит п-входовой ограничитель 1 п-входовой модульный сумматор 2, операционные усилители 3 и 4, масштабирующие резистор 5, ...5.,, 6, резистивные делители, выполненные на резисторах 7-12, вхо ные-выходные шины Устройство работает следующим образом. На входные шины 13.-13, поступают входные сигналы, представленные в системе остаточных классов. Н пряжение, пропорциональное модульной сумме входных сигналов образуется на выходе модульного сумматора 2 и поступает через резистор 6 на вход операционного усилителя 3. В точке К соединения средних выводов резистивных делителей появляется напряжение „ ,где выходное напряжение модульного сумматора 2. При условии Rg имеем: ВЫ7(П4--(). 4 Итак, результат модульного сумирования , получаемый на выходе одульного сумматора 2, является окончательным и совпадает с сигнаом на шине 13. При этом ограничитель 1 не работает. Для исключения неоднозначности при выполнении .операции модульного сложения необратимым модульным сумматором 2 введен ограничитель 1, В простейшем случае он по каждому входу выполнен на паре стабилитронов, включенных встречно между входом ограничителя и шиной нулевого потенциала. При зтом выходными являются (п+1)-я шина 13, и шины без шины 13,. Аналогично на J-TOM входе устанавливается напряжение, определяемое изменением выходного напряжения операционного усилителя 3, Пробивные напряжения пары стабилитронов ограничителя 1 должны быть такими, чтобы при напряжении на входах (1-п), соответствующих числам О (т-1) ( где m - величина модуля), стабилитроны имели высокое сопротивление. При увеличении или уменьшении этого напряжения относительно заданной зоны стабилитроны пробиваются, и происходит ограничение j-того сигнала. Итак, на выходе п-входового необратимого модульного сумматора 2 при подаче на п входов единичных сигналов,на его выходеобразуется сигнал, соответствующий-модульной сумме п сигналов -по модулю гл. Величина модуля задается в схеме необратимого модульного сумматора 2. При на входы сумматора 2 поступают единичные сигналы, в этом случае при четном п модульная сумма рав.на нулю, а при нечетном п - единице. Технико-экономический эффект от использования изобретения определяется расширением функциональных возможностей вычислительной структуры благодаря универсализации BEieiiiних шин. Формула изобретения Устройство для- сложения в системе остаточных классов содержащее первый операционный усилител., вход которого соединен с первым выводом входного масштабирующего реэистг1ра

5

и группу из п масштабирующих резисторов, включенных соответственно между выходом первого операционного .усилителя и группой из п входов выходов устройства, отличаю щ е ес я тем, что, с целью расшчрения функциональных возможностей за счет обеспечения обратимости сложения, устройство содержит п-входовой модульный сумматор, п-входовой ограничитель, второй операционный усилитель и три резистивных делителя, при этом входы п-входового модульного сумматора и п-входового ограничителя соединены с соответств ющими по номеру входами- выходами устройства, выход п-входового модульного сумматора соединен со вторым выводом входного масштабирую06

щего резистора, первцй резистивный делитель включен между входом и выходом первого операционного усилителя, а второй и третий резистивные делители - между входом и выходом второго операционного усилителя, средлие выводы первого и второго резистивных делителей объединены, а средний вывод третьего является дополнительным входом - выходом устройства.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 4083236, кл. G Об G 7/14, 1971.

2.Авторское свидетельство СССР № 430380, кл. G06 F 7/50, 1971 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| ФОРМИРОВАТЕЛЬ ГАРМОНИЧЕСКОГО СИГНАЛА | 2015 |

|

RU2565424C1 |

| Сравнивающее устройство | 1977 |

|

SU708297A1 |

| Ждущий мультивибратор | 1981 |

|

SU1005275A1 |

| Формирователь сигнала с заданными значениями коэффициента нелинейных искажений | 1991 |

|

SU1802303A1 |

| ИЗМЕРИТЕЛЬ ВИБРАЦИИ | 2020 |

|

RU2754243C1 |

| Многоканальный синхронный фильтр | 1983 |

|

SU1092707A1 |

| Стабилизирующий источник постоянного тока | 1988 |

|

SU1552155A1 |

| Устройство для извлечения квадратного корня | 1981 |

|

SU1005082A1 |

| Устройство для получения тригонометрических функций | 1987 |

|

SU1506457A1 |

| ПРЕОБРАЗОВАТЕЛЬ СОПРОТИВЛЕНИЯ И ТЕРМО-ЭДС В НАПРЯЖЕНИЕ | 2015 |

|

RU2612200C1 |

Авторы

Даты

1981-05-15—Публикация

1979-07-20—Подача