(54) КОМПЕНСАЦИОННЫЙ ФАЗОМЕТР

| название | год | авторы | номер документа |

|---|---|---|---|

| Коммутационный фазометр | 1977 |

|

SU732761A1 |

| Цифровой коммутационный фазометр | 1978 |

|

SU765749A1 |

| Инфранизкочастотный фазометр | 1975 |

|

SU736004A1 |

| Измеритель разности фаз | 1974 |

|

SU516000A1 |

| Фазометр | 1980 |

|

SU960657A1 |

| Измеритель разности фаз | 1978 |

|

SU890263A2 |

| Одноканальный инфранизкочастотныйфАзОМЕТР | 1979 |

|

SU834591A1 |

| Двухканальный коммутатор гармонических сигналов | 1979 |

|

SU790303A1 |

| Способ измерения дискретного спектра времен релаксации диэлектрических материалов и сред и устройство для его осуществления | 1986 |

|

SU1402910A1 |

| КОМПАРАЦИОННЫЙ ИЗМЕРИТЕЛЬ ФАЗОВЫХ ОТКЛОНЕНИЙ | 1971 |

|

SU320783A1 |

Изобретение относится к фазоизмерцтепъной технике и может быть испол зовано при создании широкополосных цифровых фазометров. Известен цифровой автокомпенсаци- онный фазометр с использованием цифро вых фазовращателей на основе двух один ковых синхронно работающих пересчетны триггерных систем, на вход которых подаются импульсы задающего генератора f 5 . Недостатком этого фазометра является необходимость ручной перестройк частоты импульсного генератора при изменении частоты сравниваемых по фор ме напряжений, что уменьщает быстродействие устройства. Известен широкополосный цифровой автокомпенсациднный фазометр, .содержащий в двух каналах последовательно соединенныеформирователь коротких импульсов, фазоинвертор и автоматический переключатель, интегратор, дв элемента совпадения, пересчетные триггерные схемы, отсчетш 1Й блок zl. Принцип действия этого фазометра заключается в периодическом изменении фазы входных напряжений на 180° в преобразовательных каналах фазометра и введении компенсирующего фазового сдвига между модулирующими напряжениями. Однако, при периодической коммутации сравниваемых по фазе сигналов в каналах фазометра возникают переходные процессы, обуславливая случайные погрешности измерения. При этом, прскольку импульсы коммутации (выходного сигнала пересчетных схем) и сравниваемые сигналы независимы друг от друга, то фазовые .сдвиги (во многом определяющие длительность и амплитуду переходного процесса)коммутируемых сигналов относительно импульсов коммутации изменяются во времени, что не позволяет учесть влияние преходных процессов при калибровке прибора.

Для уменьшения влияния переходных процессов увеличивают соотношение периода коммутации к периоду коммутируемых сигналов, что при заданной нижней частоте сравниваемых по фазе сигналов приводит к резкому уменьшению быстродействия фазометра.

Цель изобретения - повышение быстродействия и точности измерения, путе синхронизации имцульсов коммутации таким образом, что период коммутации становится кратным периоду коммутируемых сигналов во всем частотном диапазоне их изменения.

Поставленная цель достигается тем, что в компенсационный фазометр, содержащий в двух каналах последовательно соединенные фазоинвертор, автоматический переключатель и формирователь коротких импульсов, выходами соединенные со входами фазового детектора, выход которого через интегратор соединен с потенциальными входами элементов И, выходы которых соединены с первыми входами пересчетных схем первые выходы которых соединень с отсчетным блоком, а вторые - со входами автоматических переключателей, введены треквходовый элемент И, первый и второй одновибраторы и первый и второй дискриминаторы, причем выход второго дискриминатора соединен с импульсными входами элементов И, а вход - со входом второго одновибратора и с третьим входом трехвходового элемента И, первый вход которого соединен с выходом первого дискриминатора, входом соединенного со входом одного из фазоинверторов, второй с выходом второго одновибратора, а вьгход - с импульсными входами пересчетных схем и со входом первого одновибратора, выход которого соединен со входом второго одновибратора.

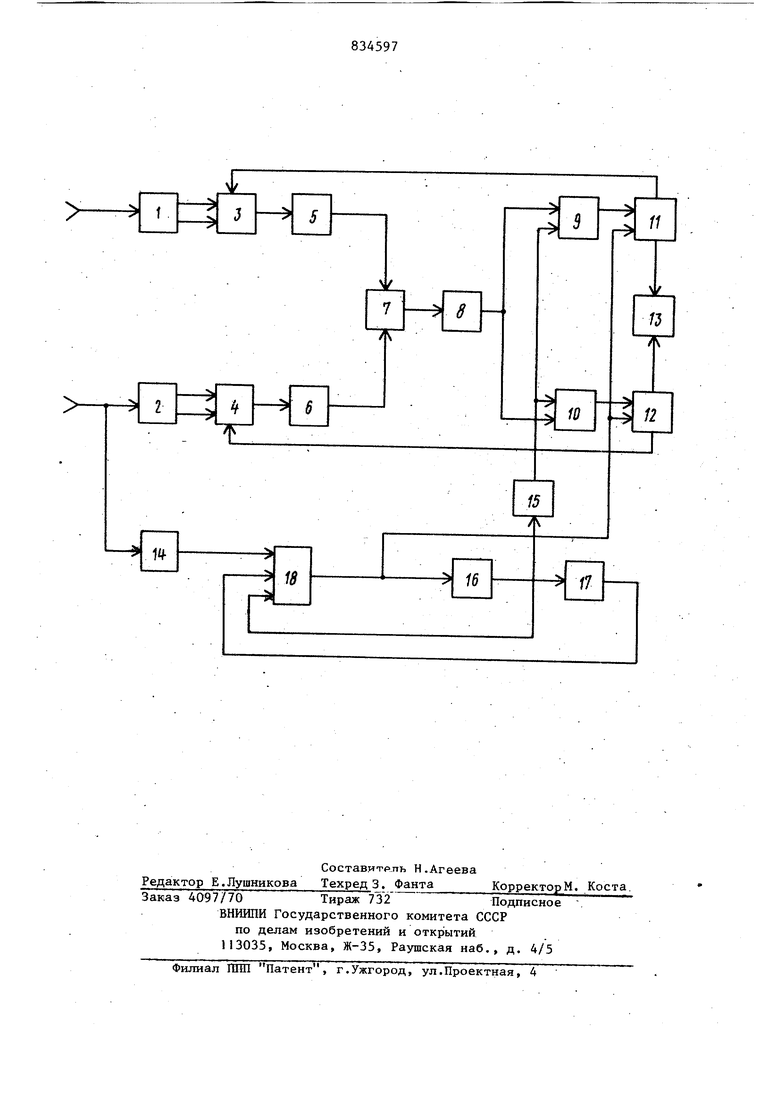

На чертеже представлена блок-схема комйенсациошюго фазометра

Фазометр содержит первый 1, вТор9Й 2 фазоинверторы, первый 3 и второй 4 .автоматические переключатели, первый 5 и второй 6 формирователи коротких импульсов, фазовый детектор 7, интегратор 8, первый 9 и второй 10 элементы И, первую 11 и вторую 12 пересчетные схемы, отсчетный блок 13, первый 14 и второй 15 дискриминаторы первый 16 и второй 17 одновибраторы и трехвходовый элемент И 18.

Устройство работает следующим образом.Сравниваемые по фазе напряжения поступают на фазовые инверторы I и 2, каждый из которых расщепляет входной сигнал на два противофазных напряжения.

При непрерывной работе автоматических переключателей 3 и 4 на формирователи коротких импульсов 5 и 6 поочередно воздействуют пакеты противофазных напряжений. Выходы формирователей 5 и 6 соединены со входами двухполярного фазового детектора 7, имеющего пилообразную, симметричную относительно нуля амплитудно-фазовую характеристику.

Управление работой переключателей 3 и 4 осуществляется импульсами синхронизированного генератора через пересчетные схемы 11 и 12, выполняющие роль дискретных фазовращателей. Коэффициент пересчета выбирается.равным , где п - целое число, определяемое допустимой дискретностью компенсирующего сдвига фаз.

При наличии фазового сдвига между выходными напряжениями пересчетных схем 11 и. 12 на фазовый детектор 7 поступают последовательности импульсов то в фазе (или обе последовательности в противофазе), то одна из последовательностей в фазе, а другая в противофазе. В результате в течение одного пернода коммутации импульсов на выходе фазового детектора 7 действует положительное или отрицательное напряжение.

Оно воздействует на интегратор 8 (фильтр постоянн9 го тока), через который проходит сГреднее значение напряжения. Если частота переключений меньше частоты следования импульсов, то время .действия положительного и отрицательного напряжения определяется фазовым сдвигом между напряжениями на выходах пересчетнык схем 11 и 12. Среднее значение напряжения на выходе интегратора 8 пропорционально разности измеряемого и компенсирующего фазового сдвига.

Измерение фазового- сдвига осуществляется путем его уравновешивания компенсирующим сдвигом фаз между напряжениями, управляющими работой автоматических перключателей. Регулирование фазового сдвига между выходными напряжениями пересчетных схем П и 12 достигается временным сдвигом моментов их заполнения. Для этого одно их входных напряжений подается на ди скриминатор 14, выходные импульсы ко торого поступают на трехвходовый эле мент 18, С выхода элемента И 18 импульсы поступают на пересчетные схемь 11 и 12, ас выхода дискриминатора 15 на импульсные входы элементов И 9 и 10. На их потенциальные входы поступает выходное напряжение интегратора 8, При этом один из элементов И открывается напряжением положительно полярности, другой - напряжением отрицательной полярности. Через открытый элемент И импульсы поступают на вход одной из пересчетных схем. Выбор полярности элементов И осуществляется таким образом, чтобы сдвиг фаз между выходными напряжениями пересчетных схем изменялся-в сторону компенсации измеряемого фаз. При достижении компенсации выход , ное напряжение интегратора примет ну левое значение и подача дополнительных импульсов с дискриминатора 15 на пересчетные схемы прекращается разностью кодов, представленных состояниями триггеров пересчетных схем 11 и 12. Разностный код преобразуется в десятичный и индицируется на отсчетном блоке 13. Отличительной особенностью компенсационного фазометра является синхронизация запускающих импульсов пересчетных схем одним из сравниваемых сигналов. При этом поскольку период запускающих импульсов кратен периоду сравниваемых сигналов, то период выходных сигналов пересчетных схем в установившемся режиме также кратен периоду сравниваемых сигналов. Это является одним из условий стабилизации переходного процесса в каналах фазометра, что позволяет значительно уменьшить соотношение периода коммутационных импульсов с периодом сравниваемых сигналов и как след-j ствие повысить, быстродействие и точность компенсационного фазометра. Формула изобретения Компенсационный фазометр содержащий в двух Каналах последовательно соединенные фазоинвертор, автоматический переключатель и формирователь коротких импульсов, выходами соединенные со входами фазового детектора, выход которого через интегратор соединен с потенциальными входами элементов И, выходы которых соединены с первыми входами пересчетных схем первые выходы которых соединены с отсчетным блоком, вторые - со входами автоматический переключателей, отличающийся тем, что, с целью повышения быстродействия и точности измерения, в него введены трехвходовьй элемент И, первый и второй одНовибраторы и первый и второй дискриминаторы, причем выход второго дискриминатЬра соединен с импульсными входами элементов И, а вход - со входом второго одновибратора и с третьим входом трехвходового элемента И, первый вход которого соединен с выходом первого дискриминатора, входом соединенного со входом одного из фазоинверторов, второй - с выходом второго одновибратора, а выход - с импульсными входами пересчетных схем и со входом первого одновибратора, выход которого соединен со входом второго одновибратора. Источники информации, ринятые во внимание при экспертизе 1.Авторское свидетельство СССР 245913, кл. G 01 R 19/02, 1969. 2.Авторское свидетельство СССР 351179, кл. G 01 R 25/04, 1972.

Авторы

Даты

1981-05-30—Публикация

1979-07-09—Подача