Изобретение относится к электротехники и может быть использовано для производства блоков радиоэлектронной аппаратуры на базе печатных плат.

Известно устройство для сборки печатных плат, содержащее монтажные посты, носитель информации с выходам по числу монтажных постов и блок управления носителем информации с входами по числу монтажных постов, причем каждый монтажный пост состоит иэ накопителя для радиоэлементов, бЛока подсветки коммутационного аппа рата l .

Однако устройство не обеспечивает высокой производительности и облгщает узкими Технологическими возможностями .

Цель изобретения - повышение производительности и расширение технологических возможностей. Поставленная цель достигается тем, что, в устройство для многоцелевой сборки печатных плат, содержащем монтажные посты, носитель информации с выходами по числу монтажных постов и блок управления носителем информации с «ходами по числу монтажных постов/

каждый монтажный пост снабжен буферным запоминающим блоком и блоком оперативной памяти, подключенным своим первым выходом к накопителю электрорадиОэлементов, вторым выходом ко входу блока подсветки, а входом к первому выходу буферного запоминающего блока, в свою очередь,, подключенного первым входом к первому выходу блока коммутации, а второй вход - к выходу носителя информации, причем второй выход коммутационного блока подключён к из входов блока управления, а вход коммутационного блока ко Второму выходу буферного запоминающего блока

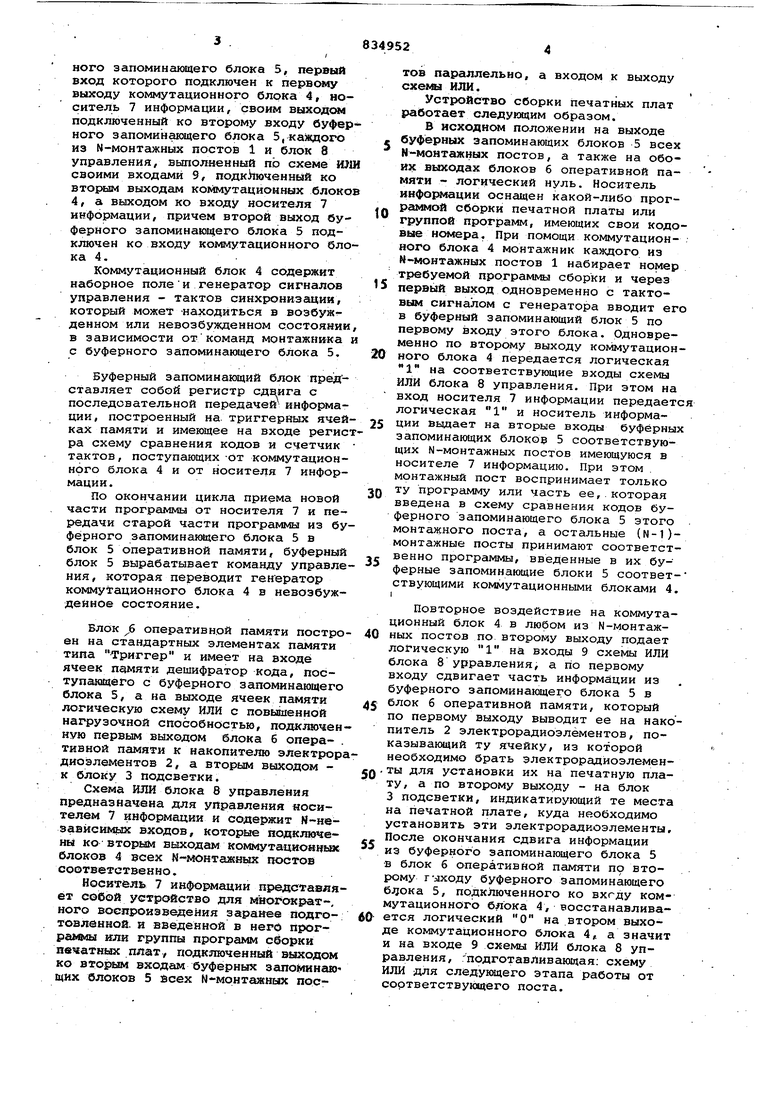

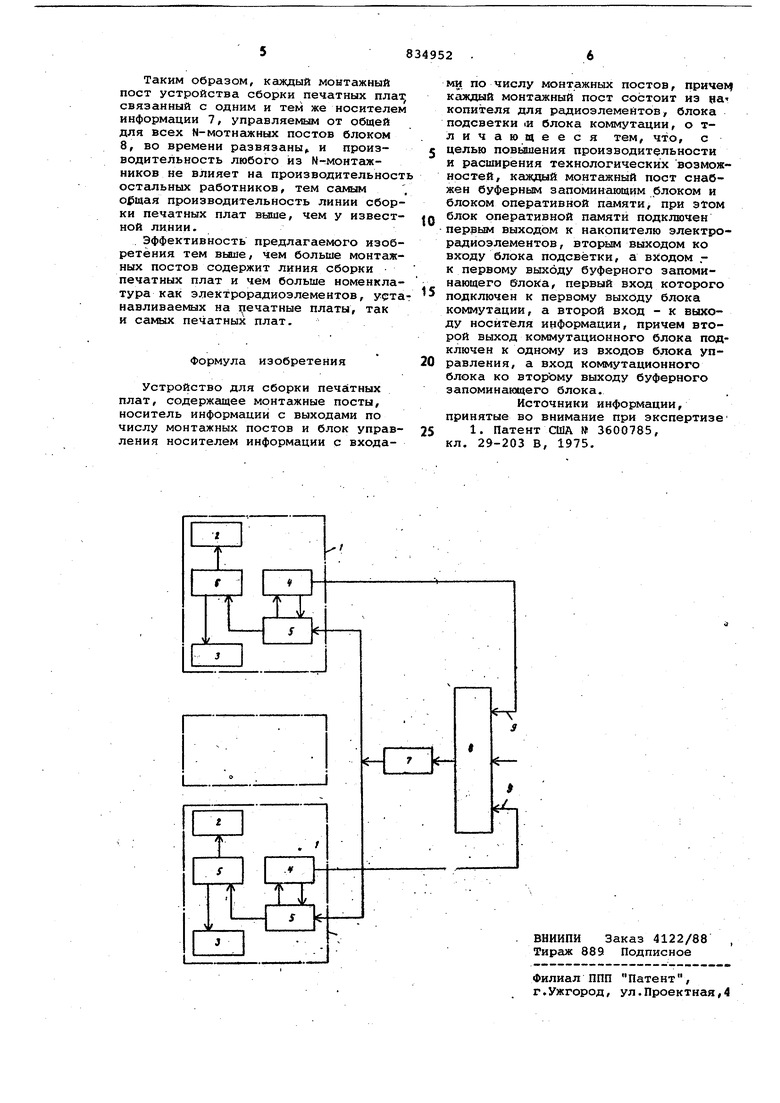

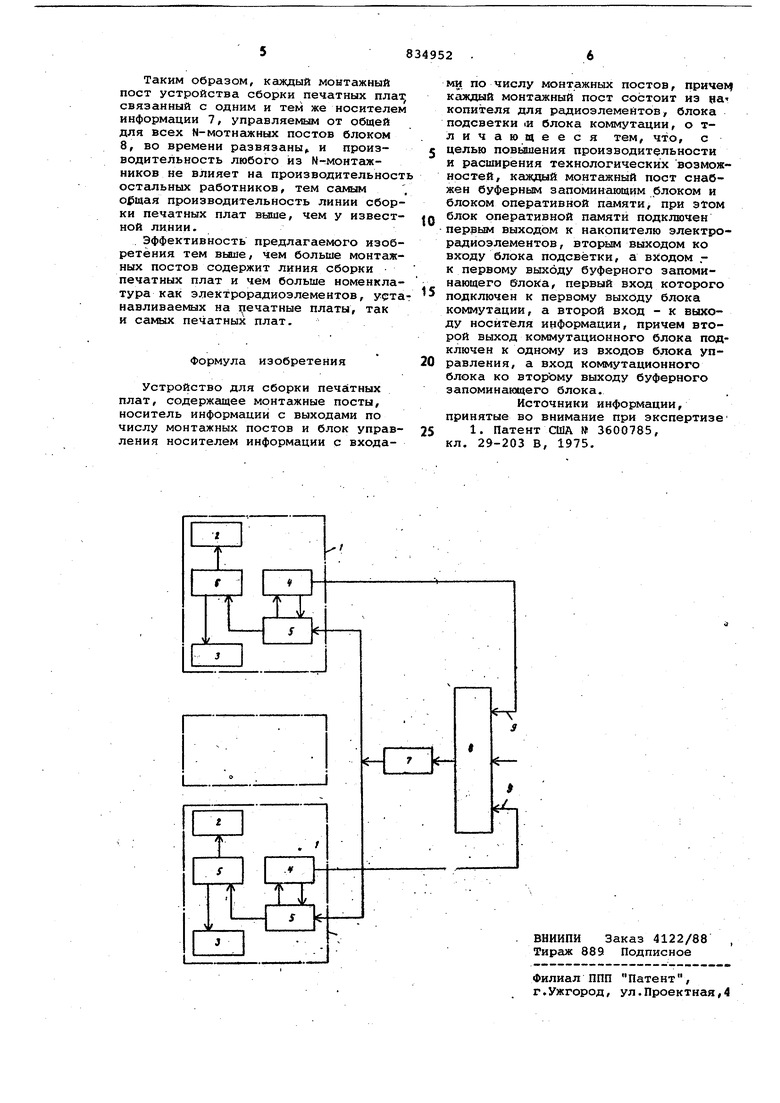

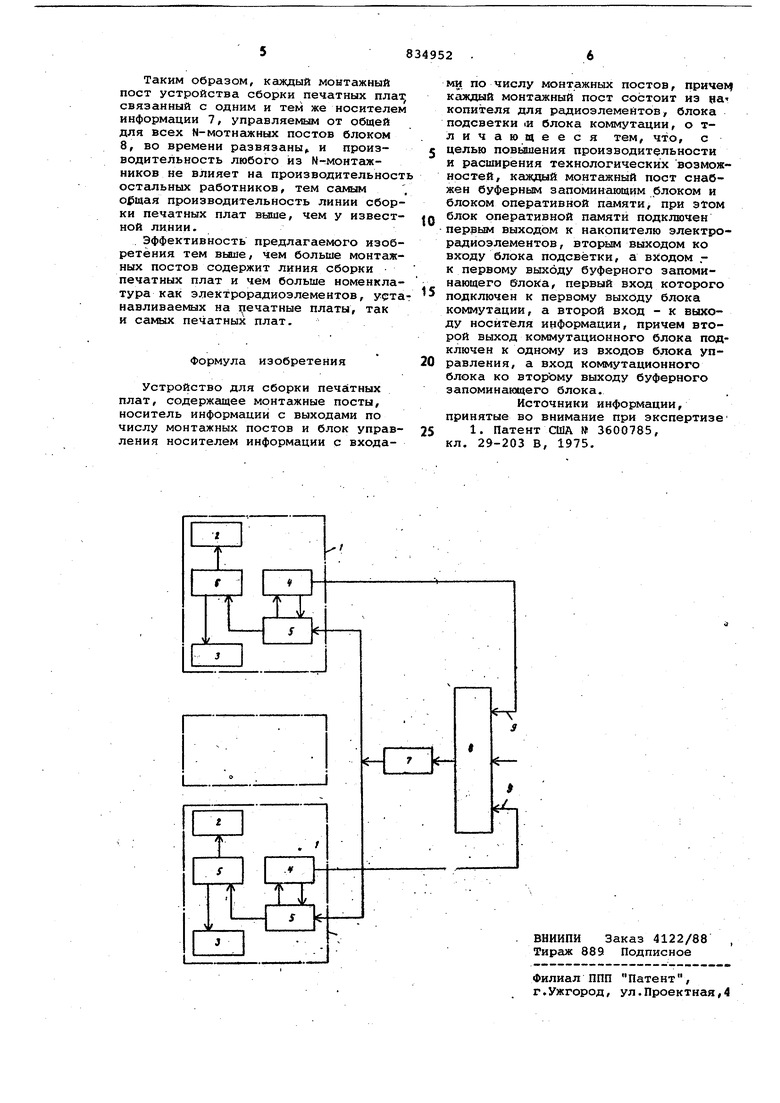

На чертеже изображена блок-схема устройства.

Устройство содержит N-монтажных постсгв 1, каждый из которых имеет накопитель 2 электрорадиоэлементов, блок 3 подсветки, коммутационУ1ый блок 4, буферный запоминающий блок 5 и блок 6 оперативной памяти, своим первым выходом подключенный к соответствующему накопителю 2 электрорадиоэлементов, вторым выходом к соответствующему блоку 3 подсвет. ки, а входом к первому выходу буферного запоминающего блока 5, первый вход которого подключен к первому выходу коммутационного блока 4, носитель 7 информации, своим выходсш подключенный ко второму входу буферного запоминающего блока 5,каждого из N-монтажных постов 1 и блок 8 управления, выполненный по схеме Ш1И своими входами 9, подключенный ко вторым выходам коммутационных блоков 4, а выходом ко входу носителя 7 информации, причем второй выход буферного запоминающего блока 5 подключен ко входу коммутационного блока 4.

Коммутационный блок 4 содержит наборное поле и генератор сигналов управления - тактов синхронизации, который может находиться в возбуж денном или невозбужденном с.остояйии, в зависимости откоманд монтажника и с буферного запоминающего блока 5,

Буферный запоминающий блок представляет собой регистр сд&ига с последовательной передачей информации , построенный на. триггерйых ячейках памяти и имеющее на входе регистра схему сравнения кодов и счетчик тактов, поступающих -от коммутационного блока 4 и от носителя 7 информации.

По окончании цикла приема новой части программы от носителя 7 и передачи старой части программы из буферного запоминающего блока 5 в блок 5 оперативной памяти, буферный блок 5 вырабатывает команду управления, которая переводит генератор коммутационного блока 4 в невозбужденное состояние.

Блок 6 оперативной памяти построен на стандартных элементах памяти типа Триггер и имеет на входе ячеек памяти дешифратор кода, поступающего с буферного запоминающего блока 5, а на выходе ячеек памяти логическую схему ИЛИ с повышенной нагрузочной способностью, подк шченную первым выходом блока б опера- . тивной памяти к накопителю электрорадиоэлементов 2, а вторым выходом к блоку 3 подсветки.

Схема ИЛИ блока 8 управления предназначена для управления носителем 7 информации и содержит N-независимых входов, которые подкл1 }чены ко вторым выходам коммутационньас блоков 4 Н-монтажных постов соответственно.

Носитель 7 информации представляет собой устройство для многократ-, ного воспроизведения заранее подготовленной, и введенной в него прогреаФал клк группы программ сборки печатных плат, подключенный выходом ко вторым вкодам буферных запоминающих блоков 5 дсек Ымонтажных постов параллельно, а входом к выходу схеш ИЛИ.

Устройство сборки печатных плат работает следующим образом.

В исходном положении на выходе буферных запоминающих блоков 5 всех N-монтажных постов, а также на обоих выходах блоков б оперативной памяти - логический нуль. Носитель инфОЕФюции оснащен какой-либо прогpa 04Oй сборки печатной платы или группой программ, имеющих свои кодовые номера. При помощи коммутационного блока 4 монтажник каждого из К-монтажных постов 1 набирает номер требуемой програмиш сборки и через первый выход одновременно с тактовым сигналом с генератора вводит его в буферный запоминающий блок 5 по первому входу этого блока. Одновременно по второму выходу коммутационного блока 4 передается логическая 1 на соответствующие входы схемы ИЛИ блока 8 управления. При этом на вход носителя 7 информации передаетс логическая 1 и носитель информации вьщает на вторые входы буферных запоминающих блоков 5 соответствующих N-монтажных постов имеющуюся в носителе 7 информацию. При этом монтажный пост воспринимает только ту программу или часть ее,.которая введена в схему сравнения кодов буферного запоминающего блока 5 этого монтажного поста, а остальные (N-1)монтажные посты принимают соответственно программы, введенные в их буферные запоминающие блоки 5 соответствующими коммутационными блоками 4.

Повторное воздействие на коммутационный блок 4 в любом из N-монтажных постов по второму выходу подает логическую 1 на входы 9 схемы ИЛИ блока 8 урравления, а по первому входу сдвигает часть информации из буферного запоминакщего блока 5 в блок б оперативной памяти, который по первому ВЫХОДУ выводит ее на накопитель 2 электрорадиоэлёментов, показывакмций ту ячейку, из которой необходимо брать электрорадйоэлемен.ты для установки их на печатную плату, а по второму выходу - на блок 3 подсветки, индикатиоующий те места на печатной плате, куда необходимо установить эти электрорадиоэлементы, После окончания сдвига информации из буферного запоминающего блока 5 в блок б оперативной памяти по второму г аходу буферного запоминающего 6jjoKa 5, подключенного ко вхгду коммутационного блока 4, восстанавливается логический О на втором выходе коммутационного блока 4, а значит и на входе 9 схемы ИЛИ блока 8 управления, подготавливающая; схему ИЛИ для следуницего этапа работы от соответствующего поста. Таким образом, каждый монтажный пост устройства сборки печатных плат; связанный с одним и тем же носителем информации 7, управляемым от общей для всех М-мотнс1Жных постов блоком 8, во времени развязаны, и производительность любого из N-монтажников не влияет на производительност остальных работников, тем самым производительность линии сборки печатных плат вьаае, чем у известной линии. Эффективность предлагаемого изобретения тем вьаае, чем больше монтажных постов содержит линия сборки печатных плат и чем больше номенклатура как электрорадиоэлементов, урта навливаемых на печатные платы, так и самых печатных плат. Формула изобретения Устройство для сборки печатных плат, содержащее монтажные посты, носитель информации с выходами по числу монтажных постов и блок управления носителем информации с входами по числу монтажных постов, npH4ei f каждый монтс1жный пост состоит из на копителя для радиоэлемейтов, блока подсветки 1И блока коммутации, о тличаюцееся тем, что, с целью повышения производительности и расширения технологических возможностей, каждый монтажный пост снабжен буферным запоминающим блоком и блоком оперативной памяти, при afoM блок оперативной памяти подключен перрым выходом к накопителю электрорадиоэлементов, вторым выходом ко входу блока подсветки, а входом ,к первому выходу буферного запоминающего блока, первый вход которого подключен к первому выходу блока кo вvIyтaции, а второй вход - к выходу носителя информации, причем второй выход коммутационного блока подключен к одному из входов блока управления, а вход коммутационного блока ко второму выходу буферного запоминающего блока. Источники информации, принятые во внимание при экспертизе 1. Патент США № 3600785, кл. 29-203 В, 1975.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для установки радиоэлементов на печатную плату | 1976 |

|

SU612429A1 |

| Устройство для установки радиоэлементов на печатную плату | 1977 |

|

SU641690A1 |

| Линия сборки блоков радиоэлектронной аппаратуры | 1980 |

|

SU886344A1 |

| УСТРОЙСТВО НАКОПЛЕНИЯ И ОБРАБОТКИ ИНФОРМАЦИИ (УНОИ) | 2008 |

|

RU2398279C2 |

| Устройство для автоматического проектирования сборки печатной платы | 1983 |

|

SU1125630A1 |

| Устройство для монтажа радиоэлементовНА плАТу | 1979 |

|

SU828451A1 |

| АВТОМАТИЗИРОВАННОЕ УСТРОЙСТВО КОНТРОЛЯ РАБОТОСПОСОБНОСТИ И ДИАГНОСТИКИ НЕИСПРАВНОСТЕЙ РАДИОЭЛЕКТРОННОЙ АППАРАТУРЫ | 2019 |

|

RU2715425C1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ДАННЫХ С МИКРОСХЕМ | 2017 |

|

RU2656582C1 |

| Устройство для отображения информации | 1977 |

|

SU734759A1 |

| СИСТЕМЫ И СПОСОБЫ ОБЕСПЕЧЕНИЯ ДИНАМИЧЕСКОГО МОДУЛЬНОГО УСТРОЙСТВА ОБРАБОТКИ ДАННЫХ | 2003 |

|

RU2386163C2 |

Авторы

Даты

1981-05-30—Публикация

1979-07-05—Подача