. .1

Изобретение относится к электротехнике и может быть использовано в качестве вторичного источника питания.

Известен сТгабилизированный однотактный конвертор, содержащий усилитель мощности с трансформатором, выходная обмотка которого через выпрямитель и фильтр подключена к выходным клеммам, блоКи запуска и управ.ленкя 1.

Однако данный конвертор обладает недостаточно высоким КПД,обусловленным большими потерями в силовом транзисторе усилителя мощности.

Наиболее близким к изобретению является конвертор, содержащий усилитель мощности, входом питания подключенный к входным клеммам, вторичная обмотка трансформатора которого через выпрямитель и фильтр соединена с выходными клеммами,формирователь управляющих импульсов,вхо которого подключен к выходным клемMaiM, управляющий трансформатор,первая обмотка которого подсоединена к управляющему входу усилителя мощности, и первый дополнительный транзистор, коллектор которого подключен

к первому выводу второй обмотки управляющего трансформатора 2.

К его недостаткам следует отнести недостаточно высокий КПД и малую надежность, что обусловлено необходимостью расчета цепей насыщения и запирания силового транзистора усилителя мощности с учетом большого технологического и температурного

0 разбросов его характеристик.

Цель изобретения - повышение надежности и КПД устройства .

Поставленная цель достигается тем, что в стабилизированном однотактном

5 конверторе выход формирователя импульсов через введенный инвертор соединен с одним входом введенного узла совпадения, другой вход которого подключен к выходу выпрямителя,

0 выход введенного узла совпадения через первый введенный импульсный усилитель с двухтактным выходным каскадом соединен с базой первого дополнительного транзистора, эмиттер ко5торого через первый введенный токозада-. ющий резистор подключен к первой входной , выход формирователя импульсов через второй введенный импульсный усилитель с двухтактным выходным каскадом соединен с базой

0

йторого дополнительного транзистора, коллектор которого подключен к первому выводу третьей обгдотки управляющетО трансформатора, а эмиттер через второй введенный токозадающий резистор к первой входной клемме, вторые выводы второй и третьей обмоток управляющего трансформатора подключены к второй входной клекме, первые выводы питания первого и второго введенных импульсных усилителей соединены с первой входной клеммой, а вторые выводы питания через вспомогательный стабилизатор - с второй входной клеглмой.

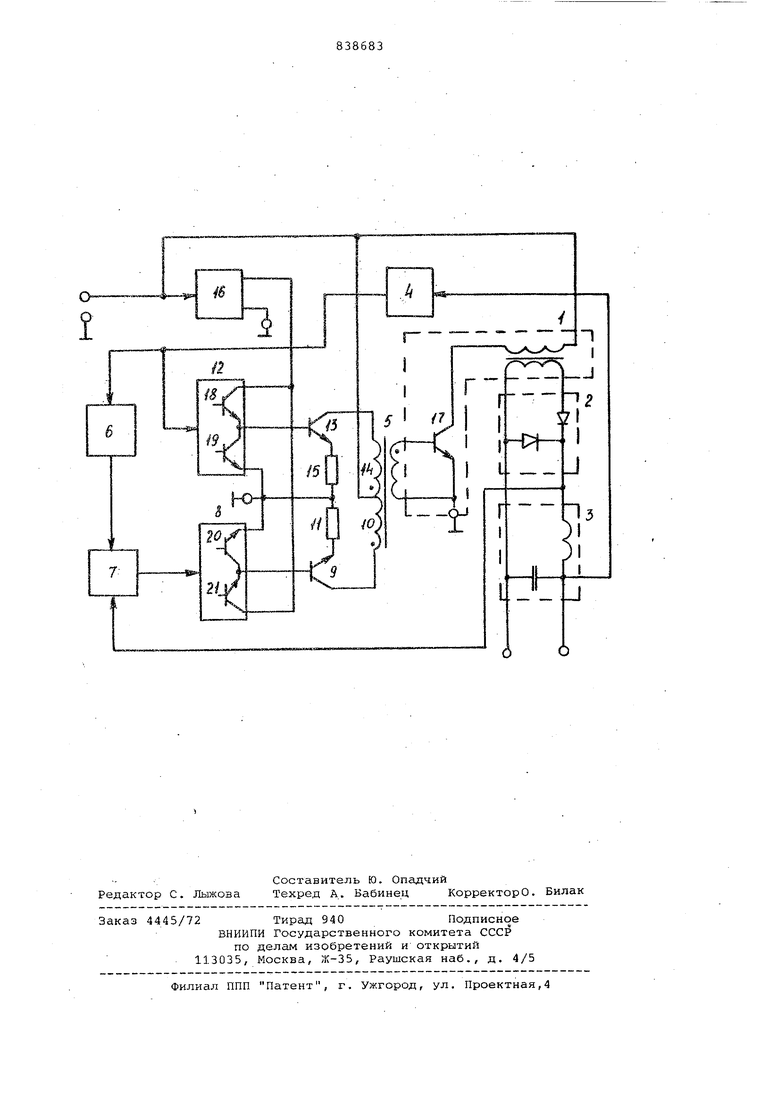

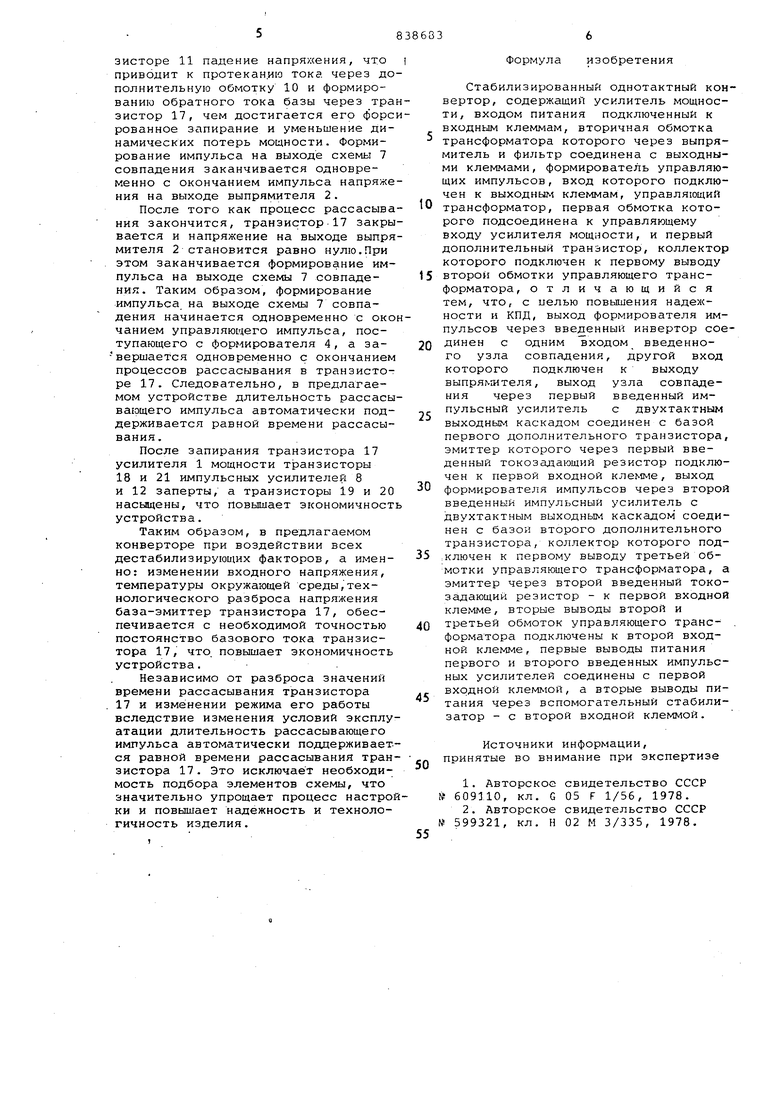

На чертеже представлена схема предлагаемого стабилизированного однотактного конвертора.

Однотактный стабилизированный конвертор содержит усилитель 1 мощности с выходным трансформатором, вторичная обмотка которого через выпрямитель 2 и фильтр 3 соединена с ВЫХОДЫЫГ.1И клеммами, формирователь 4 импульсов, управляющий трансформатор 5, вход формирователя 4 импульсов соединен с выходными клеммами, а выход через инвертор б - с первым входом схемы 7 совпадения, второй вход которой подключен, к выходу выпрямителя 2, выход схемы 7 совпадения соединен со входом первого импульсного усилителя 8, выход которого соединен с базой первого дополнительного транзистора 9, коллектор которого соединен с второй обмоткой 10 трансформатора 5, а эмитер через первый токозадающий резистор 11 - к первой входной клемме, выход формирователя соединен также со входом второго импульсного усилителя 12, выход которого соединен с базой второго дополнительного транзистора 13, коллектор которого подключен к третьей обмотке 14 трансформатора 5, а эмиттер через второй токозадаю1дий резистор 15 к первой входной клемме. По цепи питания первый и второй импульсные усилители подключены к выходу вспомогательног стабилизатора 16. Вторые выводы второй 10 и третьей 14 обмоток управляющего трансформатора 5 подсоеднены к второйвходной клемме, а первая обмотка подключена к управляющему переходу силового транзис-тора 17 усилителя 1 мощности. Выходные каскады импульсных усилителей 8 и 12 выполнены по двухтактной схеме соответственно на транзисторах 18, 19 и 20, 21.

Работает устройство следующим образом.

Усилитель 1 мощности с помощью формирователя 4 осуществляет преобразование постоянного входного напржения в импульсное,.которое затем выпрямляется выпрямителем 2 и через фильтр 3 поступает на входные

клеммы, причем длительность выходных ;импульсов формирователя 4 такова, что при действии всех дестабилизирующих факторов выходное напряжение конвертора остается постоянным.

При появлении на выходе формирователя 4 импульсов управляющего сигнала выходной транзистор 19 импульсного усилителя 12 запирается, а транзистор 18насыщается. Выходное напряжение стабилизатора 16 через транзистор 18 усилителя 12 прикладывается к базе транзистора 13 относительно общего входного вывода , со.здавая падение напряжения на втором токозадающем резисторе 15. Транзистор 13 открывается и через третью обмотку, 14 управляющего трансформатора 5 течет ток, что приводит к формированию на обмотке 14 управляющего импульса. Снимаемый с перво : обмотки трансформатора 5 управляющий импульс прикладывается непосредственно к переходу база-эмиттер транзистора 17 усилителя 1 мощности, открывая его на время длительности импульса. Ток в первичной обмотке 14 трансформатора 5 определяется только значением выходного напряжения стабилизатора 16 и величиной токозадающего резистора 15 и не зависит от параметров транзистора 17.

Таким образом, в предлагаемом конверторе обеспечивается постоянство величины тока базы транзистора 17, усилителя 1 мощности независимо от разброса значений напряхсения базаэмиттер в транзисторе 17. Это позволяет исключить устанавливаемый в цепи базы транзистора усилителя мощности для компенсации разброса напряжения база-эмиттер резистор и связанные с ним потери мощности на управление, что повышает КПД всего устройства. .

Одновременно импульсы с выхода формирователя 4 импульсов через инветор 6 поступают на вход схемы 7 совпадения, в которой осуществляется сложение импульсов с выхода инвертора б с импульсами, поступающими с вьжода выпрямителя 2. Так как сложение импульсов с выхода выпрямителя 2 осуществляется с инвертированными импульсами формирователя 4, то передний фронт импульсов с выхода схемы 7 совпадения формируется одновременно с задним фронтом импульса с выхода формирователя 4. Импульс с выхода схемы 7 совпадения поступает на вход первого импульсного усилителя 8. При этом транзистор .20 запирается, а транзистор 21 открывается . Напряжение с выхода стабилизатора 16 напряжения через открытый транзистор 21 поступает на базу первого дополнительного транзистора 9. Транзистор 9 отпирается, создавая на первом токозадающем резисторе 11 падение напря), что приводит к протеканию тока через до полнительную обмотку 10 и формированию обратного тока базы через тра зистор 17, чем достигается его форс рованное запирание и уменьшение динамических потерь мощности. Формирование импульса на выходе схемы 7 совпадения заканчивается одновременно с окончанием импульса напряже ния на выходе выпрямителя 2. После того как процесс рассасыва ния закончится, транзистор 17 закры вается и напряжение на выходе выпря мителя 2 становится равно нулю.При этом заканчивается формирование импульса на выходе 7 совпадения. Таким образом, формирование импульса на выходе схемы 7 совпадения начинается одновременно с око чанием управляющего импульса, поступающего с формирователя 4, а завершается одновременно с окончанием процессов рассасывания в транзисторе 17. Следовательно, в предлагаемом устройстве длительность рассасы вающего импульса автоматически поддерживается равной времени рассасывания. После запирания транзистора 17 усилителя 1 мощности транзисторы 18 и 21 импульсных усилителей 8 и 12 заперты, а транзисторы 19 и 20 насыщены, что повышает экономичност устройства. Таким образом, в предлагаемом конверторе при воздействии всех дестабилизирующих факторов, а именно: изменении входного напряжения, температуры окружающей среды,технологического разброса напряжения база-эмиттер транзистора 17, обеспечивается с необходимой точностью постоянство базового тока транзистора 17, что. повышает экономичность устройства. Независимо от разброса значений времени рассасывания транзистора 17 и изменении режима его работы вследствие изменения условий эксплу атации длительность рассасывающего импульса автоматически поддерживает ся равной времени рассасывания тран зистора 17. Это исключает необходимость подбора элементов схемы, что значительно упрощает процесс настро ки и повышает надежность и технологичность изделия. Формула изобретения Стабилизированный однотактный конвертор, содержащий усилитель мощности, входом питания подключенный к входным клеммам, вторичная обмотка трансформатора которого через выпрямитель и фильтр соединена с выходными клеммами, формирователь управляющих импульсов, вход которого подключен к выходным клеммам, управляющий трансформатор, первая обмотка которого подсоединена к управляющему входу усилителя мощности, и первый дополнительный транзистор, коллектор которого подключен к первому выводу второй обмотки управляющего трансформатора , отличающийся тем, что, с иелью повышения надежности и КПД, выход формирователя импульсов через введенный инвертор соединен с одним Бходом введенного узла совпсщения, другой вход которого подключен к выходу выпрямителя, выход узла совпадения через первый введенный импульсный усилитель с двухтактным выходным каскадом соединен с базой первого дополнительного транзистора, эмиттер которого через первый введенный токозадающий резистор подключен к первой входной клемме, выход формирователя импульсов через второй введенный импульсный усилитель с двухтактным выходным каскадом соединен с базой второго дополнительного транзистора, коллектор которого подключен к первому выводу третьей обмотки управляющего трансформатора, а эмиттер через второй введенный токозадающий резистор - к первой входной клемме, вторые выводы второй и третьей обмоток управляющего трансформатора подключены к второй входной клемме, первые выводы питания первого и второго введенных импульсных усилителей соединены с первой входной клеммой, а вторые выводы питания через вспомогательный стабилизатор - с второй входной клеммой. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 609110, кл. G 05 F 1/56, 1978. 2.Авторское свидетельство СССР 599321, кл. Н 02 М 3/335, 1978.

| название | год | авторы | номер документа |

|---|---|---|---|

| Стабилизированный транзисторный конвертор | 1977 |

|

SU736289A1 |

| Стабилизированный конвертор | 1978 |

|

SU748721A1 |

| Формирователь управляющих импульсов | 1990 |

|

SU1714767A1 |

| Стабилизирующий конвертор | 1980 |

|

SU902010A1 |

| Стабилизированный конвертор | 1979 |

|

SU892425A1 |

| Стабилизированный конвертор | 1977 |

|

SU663041A1 |

| Стабилизированный преобразователь постоянного напряжения | 1981 |

|

SU982164A1 |

| Стабилизированный источник питания | 1979 |

|

SU788094A1 |

| Мостовой преобразователь напряжения | 1984 |

|

SU1182609A1 |

| Стабилизированный преобразователь постоянного напряжения в постоянное | 1976 |

|

SU656162A1 |

Авторы

Даты

1981-06-15—Публикация

1979-10-26—Подача