(54) ПРЕОБРАЗОВАТЕЛЬ ПОСТОЯННОГО НАПРЯЖЕНИЯ В ПЕРЕМЕННОЕ

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь постоянного напряжения в однофазное переменное с амплитудно-импульсной модуляцией | 1981 |

|

SU997204A1 |

| Преобразователь постоянного напряжения в многофазное переменное | 1977 |

|

SU780125A1 |

| Тяговый преобразователь постоянного напряжения в трехфазное переменное | 1989 |

|

SU1690137A1 |

| Устройство принудительной коммутации тиристоров преобразователя (его варианты) | 1984 |

|

SU1264270A1 |

| Устройство принудительной коммутации тиристоров преобразователя | 1985 |

|

SU1302392A1 |

| Преобразователь постоянного напряжения в постоянное | 1980 |

|

SU928561A1 |

| Тиристорный преобразователь постоянного тока в переменный | 1979 |

|

SU868954A1 |

| Способ пуска последовательного инвертора и устройство для его осуществления | 1979 |

|

SU862347A1 |

| Тиристорный инвертор напряжения с искусственной коммутацией | 1987 |

|

SU1575279A1 |

| Устройство для принудительной коммутации тиристоров преобразователя | 1985 |

|

SU1302406A1 |

; .

Изобретение относится к силовой преобразовательной технике и может быть использовано в регулируемых втЪричных источниках питания с синусоидсшьным выходным напряжением..

Известны автономные инверторы с амплитудно-импульсной модуляцией кривой выходного напряжения. Инвертор . позволяет формировать ступенчатую кривую с нулевой полкой Ц.

Однако, только применительно к чисто активной нагрузке, работа его на RL-нагрузку сопровождается вырождением нулевой полки, и, следовательно, искажением гармонического состава напряжения на нагрузке и зависимостью от параметр ов нагрузки.

Известен преобразователь постоянного напряжения в переменное, в которс применена группа управляемых вентилей, обратного тока, включенных встречно по отношению к на:пряжению источника питания, которую коммутируют синхронно с группой вентилей прямого тока. Это обеспечивает обмен реактивной энергией между нагрузкой и питающей сетью, при этом форма кривой выходного напряжения такого инвертора не зависит от нагрузки 2.

Недостатком такого преобразователя является большая установленная мощность трансформатора, ак как он работает на частоте выходного напряжения.

Известна также более перспективна схема Салтерса, в которой к первичной обмотке трайсформатора подсоединены параллельный инвертор, а три

вторичных обмотки трансформатора

подключаются в соответствукхцей последовательности к нагрузке с помсицью тиристоров. В данном случае трансформатор работает на более высокой чаIS стоте по сравнению свыходной, что позволяет использовать трансформатор с меньшими весом и габаритами 3. Однако схема Салтерса не позволяет производить независимое от параметров нагрузки амплитудно-импульсное регулирование напряжения на нагрузке, что значительно сужает область ее применения.

Известен автономный инвертор, силовая сЛема и система управления которого использованы в качестве прототипа для силовой части и системы управления предлагаемого инвертора. Он соде1«ит однофазный мостовой инвертор d повентильной коммутацией.

к выходу которого подключен трансформатор с секционированной вторичной обмоткой, каждый из промежуточных выводов которой соединен с выходными зажимами преобразователя через пары встречно-параллельно включенных тиристоров, и имеет датчик тока в силовой цепи. Устройство для управления инвертором содержит четыре дополнительных схемы совпадения, управляемые от ячеек регистра сдвига, от регулятора длительности импульсов а также от датчиков тока. Независимость выходного напряжения от параметров нагрузки достигается тем, что в момент времени, когда из-за активно-индуктивного характера нагруки задерживается выключение какоголибо тиристора коммутатора, схема управления вырабатывает импульс на включение следунмдего тиристора коммутатора, который выключает предыдущий тиристор и создает другой путь току самоиндукции нагрузки 4 .

Недостатком данной схемы инвертора является то, что расширение диапазона работы на активно-индуктивную нагрузку достигается за счет обратных связей силовых цепей инвертора с системой управления. Это увеличивает сложность системы управления и снижает надежность работы устройства в целом. Ухудшается помехозащищенность из-за связи системы управления с током нагрузки.

Цель изобретения - повышение функциона1{ ной надежности преобразователя. I

Указанная цель достигается тем,

что в преобразователе постоянного напряжения в переменное с амплитудноимпульсной модуляцией выходного напр.ржения, содержащем однофазный инвертор напряжения, выходом подключеченный к первичной обмотке трансформатора, вторичная обмотка которого выполнена с отводами, причем один промежуточный отвод связан с первым выходным выводом преобразователя, остальные промежуточные вцводы вториной обмотки и ее концы через встречно-парсшлельно включенные тиристоры коммутатора связаны со вторым выходным выводом преобразователя, тиристорный блок принудительной коммутации, выходные выводы которого связаны «ерез разделительные вентили с силовыми электродами тиристоров коммутач ора, блок управления, выполненный виде последовательно связанных между собой задающего генератора, регулятора длительности импульсов, п-канального распределителя импульсов , логического и усилительноразвязывающего узлов управления тиристорами коммутатора и тиристорами блока принудительной коммутации, а также связанной с задающим генераTopcw длительности импульсов схемы

управления тиристорами инвертора; выводы блока принудительной коммутации подключены к точкам соединения анодов и к точкам соединения катодов двух из трех пар введенных разделительных вентилей, разноименные электроды разных пар разделительных вентилей соединены между собой через дополнительно введенные коммутирующие дроссели, средние точки обмоток которых образуют выходные выводы преобразователя, причем обмотка одного из коммутирующих дросселей шунтирована третьей парой последовательно соединенных разделительных вентилей, точка соединения которых подключена к упомянутому одному промежуточному отводу вторичной обмотки трансформатора, а к концам обмоток второго.коммутирующего дросселя подключены соответственно точки объединения анодов тиристоров коммутатора

Кроме того, преобразователь, при необходимости получения трехступенчатого выходного напряжения, снабжен элементом задержки, логическими элементами И, ИЛИ, а п-канальный распределитель импульсов выполнен с числом каналов, равным 10-ти, причем вход элемента задержки соединен со входом распределителя импульсов, а его выход подключен к логическому узлу и к первому входу логического элемента И, выход которого связан через усилительно-развязывающий каскад с тиристором блока принудительной коммутации, ко второму входу логического элемента И подключен выход логического элемента ИЛИ, входы которого соединены со вторым, третьим, седьмым каналами распределителя импульсов.

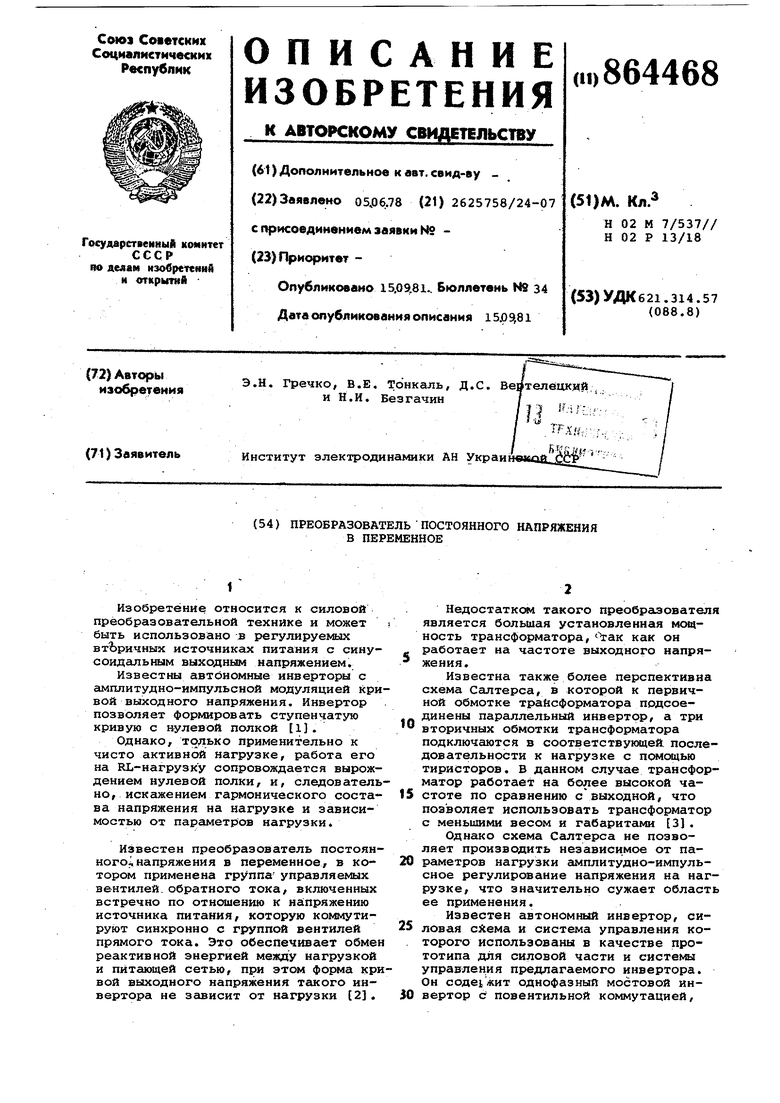

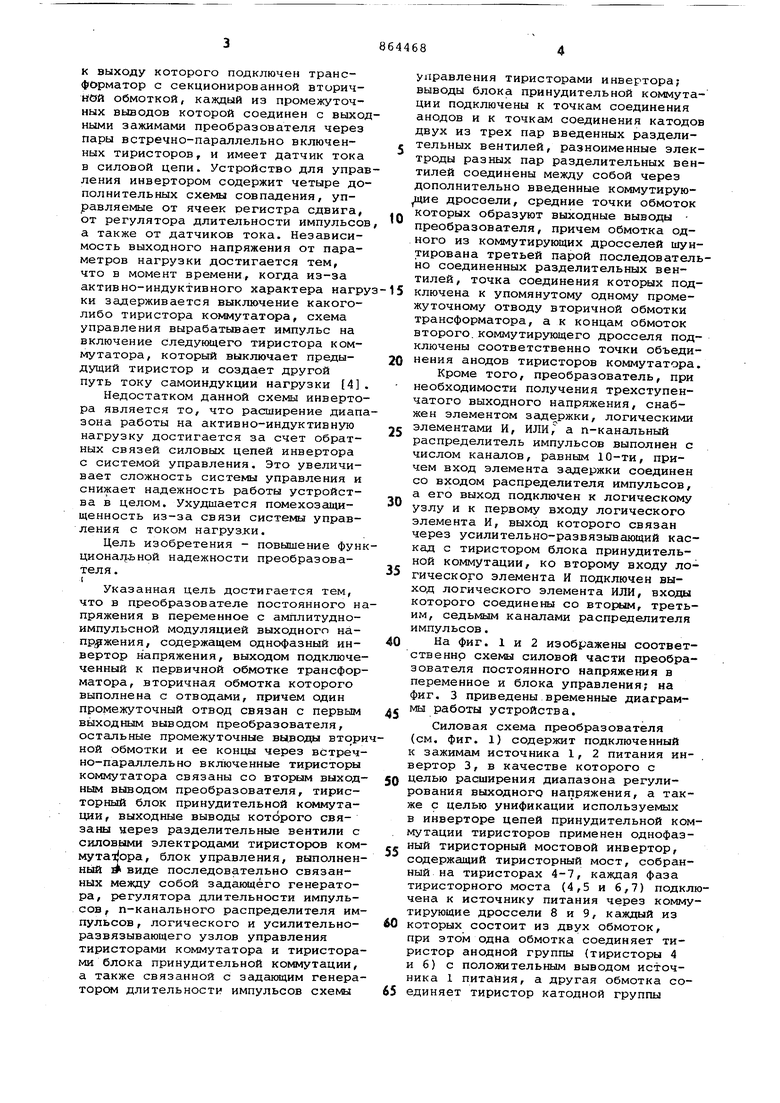

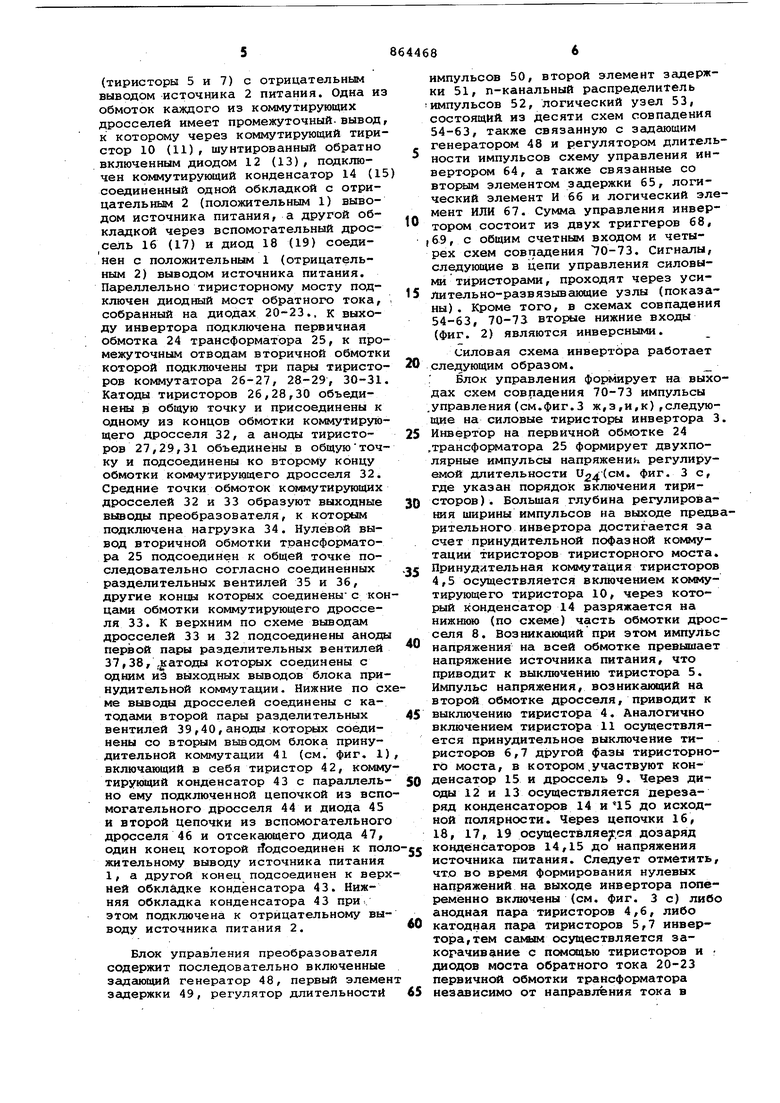

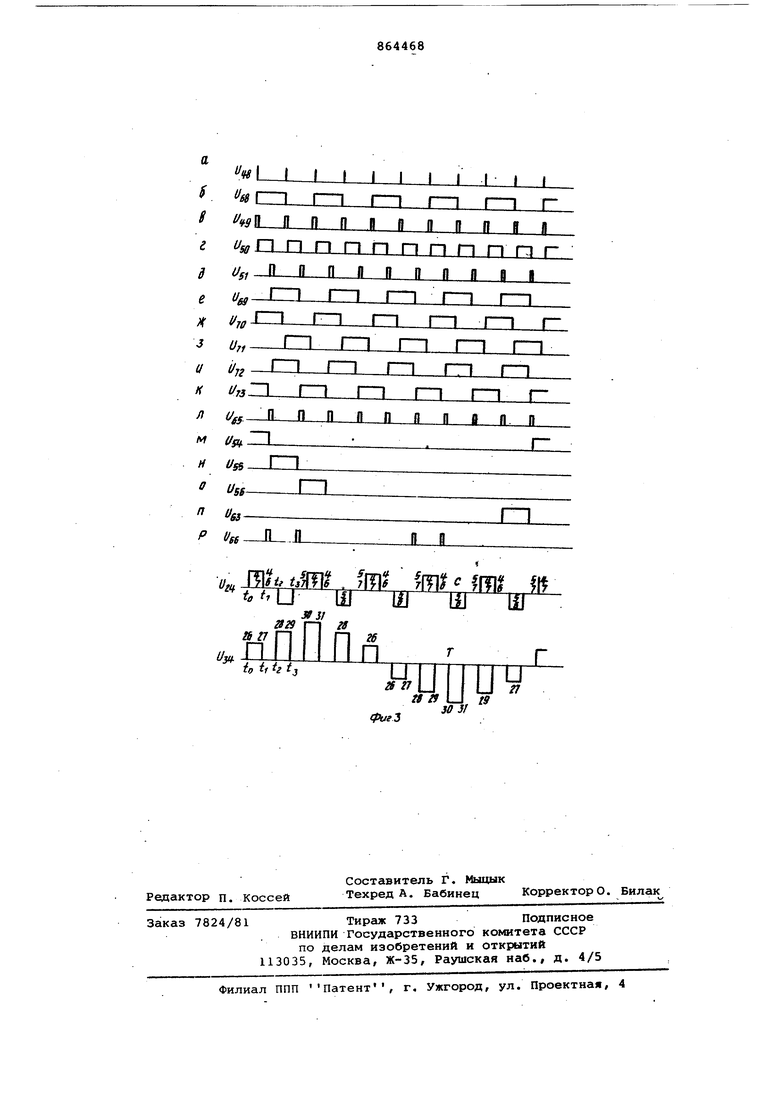

На фиг. 1 и 2 изображены соответственно схемы силовой части преобразователя постоянного напряжения в переменное и блока управления; на фиг. 3 приведены временные диаграммы работы устройства.

Силовая схема преобразователя (см. фиг. 1) содержит подключенный к зажимам источника 1, 2 питания инвертор 3, в качестве которого с целью расширения диапазона регулирования выходного напряжения, а также с целью унификации используемых в инверторе цепей принудительной коммутации тиристоров применен однофазный тиристорный мостовой инвертор, содержащий тиристорный мост, собранный на тиристорах 4-7, каждая фаза тиристорного моста (4,5 и 6,7) подклчена к источнику питания через коммутирующие дроссели 8 и 9, каждый из которых состоит из двух обмоток, при этом одна обмотка соединяет тиристор анодной группы (тиристоры 4 и 6) с положительным выводом источника 1 питания, а другая обмотка соединяет тиристор катодной группы (тиристоры 5 и 7) с отрицательньм выводом источника 2 питания. Одна и обмоток каждого из коммутирующих дросселей имеет промежуточный-вывод к которому через коммутирующий тири стор 10 (11) , шунтированный обратно включенным диодом 12 (13), подключен коммутирующий конденсатор 14 (1 соединенный одной обкладкой с отрицательным 2 (положительным 1) выводом источника питания, а другой обкладкой через вспомогательный дроссель 16 (17) и диод 18 (19) соединен с положительным 1 (отрицательным 2) выводом источника питания. Пареллельно тиристорному мосту подключен диодный мост обратного тока, собранный на диодах 20-23.. к выходу инвертора подключена первичная обмотка 24 трансформатора 25, к про межуточным отводам вторичной обмотки которой подключены три пары тиристоров коммутатора 26-27, 28-29, 30-31 Катоды тиристоров 26,28,30 объединены в общую точку и присоединены к одному из концов обмотки коммутирующего дросселя 32, а аноды тиристоров 27,29,31 объединены в общуюточку и подсоединены ко второму концу обмотки коммутирующего дросселя 32. Средние точки обмоток коммутирукидих дросселей 32 и 33 образуют выходные выводы преобразователя, к которым подключена нагрузка 34. Нулевой вывод вторичной обмотки трансформатора 25 подсоединен к общей точке последовательно согласно соединенных разделительных вентилей 35 и 36, другие концы которых соединены с кон цами обмотки коммутирующего дросселя 33. К верхним по схеме выводам дросселей 33 и 32 подсоединены аноды первой пары разделительных вентилей 37,38, ,катоды которых соединены с одним из выходных выводов блока принудительной коммутации. Нижние по сх ме выводы дросселей соединены с катодами второй пары разделительных вентилей 39,40,аноды которых соединены со вторым выводом блока принудительной коммутации 41 (см. фиг. 1) включающий в себя тиристор 42, комму тирующий конденсатор 43 с параллельно ему подключенной цепочкой из вспо могательного дросселя 44 и диода 45 и второй цепочки из вспомогательного дросселя 46 и отсекающего диода 47, один конец которой одсоединен к пол жительному выводу источника питания 1, а другой конец подсоединен к верх ней обкладке конденсатора 43. Нижняя обкладка конденсатора 43 при этом подключена к отрицательному выводу источника питания 2. Блок управления преобразователя содержит последовательно включенные задёиощий генератор 48, первый элемен задержки 49, регулятор длительности импульсов 50, второй элемент задержки 51, п-канальный распределитель импульсов 52, логический узел 53, СОСТОЯЩИЙ из десяти схем совпадения 54-63, также связанную с задающим генератором 48 и регулятором длительности импульсов схему управления инвертором 64, а также связанные со вторым элементом задержки 65, логический элемент И 66 и логический элемент ИЛИ 67. Сумма управления инвертором состоит из двух триггеров 68, (69, с общим счетным входом и четырех схем совпадения 0-73. Сигналы, следующие в цепи управления силовыми тиристорами , проходят через усилительно-развязывающие узлы (показаны) . Кроме того, в схемах совпадения 54-63, 70-73 вторые нижние входы (фиг. 2) являются инверсными. силовая схема инвертора работает следующим образом. . Блок управления формирует на выходах схем сов падения 70-73 импульсы .управления(см.фиг.3 ж,з,и,к),следующие на силовые тиристоры инвертора 3. Инвертор на первичной обмотке 24 .трансформатора 25 формирует двухполярные импульсы напряжении регулируемой длительности 424(см. с, где указан порядок включения тиристоров). Большая глубина регулироваакя ширины импульсов на выходе предварительного инвертора достигается за счет принудительной пофазной коммутации тиристоров тиристорного моста. Принудительная коммутация тиристоров 4,5 осуществляется включением коммутирующего тиристора 10, через который конденсатор 14 разряжается на нижнюю (по схеме) часть обмотки дросселя 8. Возникающий при этом импульс напряжения на всей обмотке превьоаает напряжение источника питания, что приводит к выключению тиристора 5. Импульс напряжения, возникающий на второй обмотке дросселя, приводит к выключению тиристора 4. Аналогично включением тиристора 11 осуществляется принудительное выключение тиристоров 6,7 другой фазы тиристорного моста, в котором.участвуют конденсатор 15 и дроссель 9. Через диоды 12 и 13 осуществляется дерезаряд конденсаторов 14 до исходной полярности. Через цепочки 16, 18, 17, 19 осуществляе.ся дозаряд конденсаторов 14,15 до напряжения источника питания. Следует отметить, что во время формирования нулевых напряжений на выходе инвертора попеременно включены (см. фиг. 3 с) либо анодная пара тиристоров 4,6, либо катодная пара тиристоров 5,7 инвертора, тем caivBaiM осуществляется закорачивание с помощью тиристоров и диодов моста обратного тока 20-23 первичной обмотки трансформатора независимо от направления тока в

цепи нагрузки. Энергия, запасенная в нагрузке, рассеивается в самой нагрузке.

Непосредственное формирование ступенчатого напряжения на нагрузке (см. фиг. 3 т) осуществляется с помощью тиристорного коммутатора, собранного на тиристорах 26-31. При этом для достижения независимого от параметров нагрузки амплитудно-импульсного регулирования напряжения применена принудительная коммутация тиристоров 26-31 в первой половине каждого полупериода выходного напряжения, когда возможно искажение выходного напряжения и срыв работы тиристорного коммутатора. Принудительное выключение тиристоров 26-31 происходит в момент формирования предварительным инвертором нулевого напряжения (см. фиг. 3 р, где приведены импульсы управления, формируемые элементом 66, следующие на тиристор 42 коммутационной схемы), тем самым исключается противо-ЭДС источника питания в процессе принудительного восстановления управляющих свойств тиристоров коммутатора.В MOмент коммутации (фиг. 1) напряжение конденсатора 43 через коммутирующий тиристор 42 и разделительные вентили -37-40 подается на коммутирующие дроссели в такой полярности, что уменьшает ток нагрузки, При этом все тиристоры коммутатора последовательными парами 26-27, 28-29, 3031 оказываются подключенными к напряжению на конденсаторе 43 в полярности, обеспечивающей их выключение. После выключения тиристоров 26-31 ток самоиндукции нагрузки замыкается на конденсатор блока принудительHc l коммутации. В этом случае разделительные вентили 37-40 выполняют роль выпрямительного моста, т.е. принудительная коммутация тиристоров коммутатора может производиться при любом направлении тока нагрузки и всегда будет путь для замыкания тока нагрузки на конденсатор 43. Через время восстановления тиристоров коммутатора, что определяется длительностью импульса, формируемого третьим элементом 51 задержки блока управления, импульсы управления поступают на следующую пару тиристоров, через KOTOE je и замыкается ток нагрузки по мере того, как осуществляется перезаряд коммутирующего конденсатора 43 коммз тационной схемы до противоположной полярности. После чего тиристор 42 восстанавливает свои управляющие свойства, а конденсатор 43 перезаряжается до исходной полярности через вспомогательный дроссель 44 и диод 45. Во время формирования второй половины каждой полуволны ступенчатого напряжения на нагрузке (см. фиг.З т) происходит естеств.енная 1 оммутация

тиристоров коммутатора, поэтому импульсы управления на тиристор коммутационной схемы не подаются.

Блок управления (см. фиг. 2) работает следующим образом.

Задающий генератор 48, регулируемый по частоте, формирует последовательность импульсов (см. фиг. 3 а) которая поступает на управление коммутирующим тиристором 10, на триггер 68 и на первый элемент задержки 49. Сигналы с прямого и инверсного выходов триггера 68 поступают соответственно на прямые входы схем совпадения 70 и 71, на инверсные входы которых поступает сигнал с первого элемента задержки. При этом задние фронты импульсов на выходе схем совпадения 70 и 71 формируются соответственно по заднему и по переднему фронту импульсов триггера 68, а передние фронты импульсов на выходах схем 70 и 71 совпадения сдвинуты по времени соответственно от переднего и заднего фронтов импульсов триггера 68 на. время импульса элемента задержки 49(фиг. 2). Таким образом, тиристоры 4 и 5, цепи управления которых связаны с выходами 70 и 71, в любой момент времени не могут одновременно находиться в проводящем состоянии. Длительность задержки элемента 49 должна равняться времени восстановления управляющих свойств тиристоров. Сигнал с выхода элемента задержки 49 через регулятор длительности импульсов 50 поступает на цепь, управления коммутирующим тиристором 11 и схему управления тиристорами 6 и 7. Управление тиристорами 6, 7 осуществляется аналогично управлению тиристорами 4,5. С помощью регулятор длитбльности импульсов 50 осуществляется регулировка длительности импульсов напряжения V на первичной обмотке трансформатора (сигналы на выходе элементов 68, 49, 50,51,69 приведены соответственно на фиг. 2 б,в,г,д,е).

Управление тиристорным коммутатором происходит следующим образом.

Импульсы со второго элемента 51 задержки поступают на третий элемент 65 задержки и на распределитель импул сов, выходы которого связаны с прАмыми входами схем 54-63 совпадения, на инйерсные входы которых поступают импульсы с выхода элемента 65. Схема 54-63 совпадения обеспечивает, согласно программ.е распределения, выработку импульсов включения на тиристоры Коммутатора 26-31. С выхода второго, третьего, седьмого и восьмого каналов распределителя поступают импульсы на прямые входы логического элемента ИЛИ 67, выход которого соединен с прямым йходом логического элемента И 66 второй прямой вход которого соединен с выходом элемента 65. В моменты, когда из-за активно-индуктивного характера нагрузки может произойти вырождение нулевой полки выходного-напря жения, т.е. в конце первого, второг шестого и седьмого тактовых интерва лов , по переднему фронту импульса элемента задержки 65 на выходе логи ческого элемента И формируется импульс управления коммутирующим тиристором 42, включение которого при водит к принудительному выключению всех тиристоров коммутатора. Такое построение силовой схемы и блока управления преобразователя применительно к трехступенчатому на пряжению можно распространить на Т1Ю бое число формируеьйлх ступеней напр жения на нагрузке. Формула изобретения 1. Преобразователь постоянного напряжения в переменное с амплитудно-импульсной модуляцией выходного напряжения, содержащий однофазный и вертор напряжения, выходом подключе ный к первичной обмотке трансфоЕНиатора, вторичная обмотка которого выполнена с отводами, причем один промежуточный отвод связан с первым выходным вьшодом преобразователя, остальные промежуточные отводы вторичной обмотки и ее концы через встречно-параллельно включенные тиристоры коммутатора связаны со вторы выходным выводом преобразователя, тиристорный блок принудительной коммутадии, выходные выводы которого связаны через разделительные вентили с силовыми электродами тиристоров коммутатора, блок управления, выполненный в виде последовательно связан ных собой задающего генератор регулятора длительности импульсов, логического и усилительно-развязывающего узлов управления тиристорами коммутатора и тиристорами блока принудительной коммутации, а также связанной с задающим генератором и регулятором длительности импульсов схемы управления тиристорами инвертора, отличающийся тем, что, с целью повышения функциональной надежности преобразователя, выводы блока принудительной коммутации подключены к точкам соединения анодов и к точкам соединения катодов двух из трех пар, введенных разделительных вентилей, разноименные электроды разных пар разделительных вентилей соединены между собой через дополнительно введенные коммутирующие дроссели, средние точки обмоток которых образуют выходные выводы преобразователя, причем обмотка одного из коммутирующих дросселей шунтирована парой последовательно соединенных разделительных вентилей, точка соединения которых подключена к упомянутому одному промежуточному отводу вторичной обмотки трансформатора, а к концс№ обмотки второго коммутирующего дросселя подключены, соответственно/ точки объединения катодов и точки объединения .анодов тиристоров коммутатора. 2. Преобразователь по п. 1, отличающийся тем, что при необходимости получения трехступенчатого выходного напряжения, он снабжен элементом згщержки, логическими элементами И, ИЛИ, а п-канальный распределитель импульсов выполнен с числом каналов, равным десяти, причем вход элемента задержки соединен со входом распределителя импульсов, а его выход подключен к логическому узлу и к первому входу логического элемента И, выход которого связан через {/силительно-развяэывающий каскад с тиристором блока принудитель- |Ной коммутации, ко второму входу ло1гического элемента И подключен выход логического элемента ИЛИ, входы которого соединены со в-юрым, третьим, седьмым и восьмым каналами распределителя импульсов. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 276234, кл. Н 02.М 7/48, 1969. 2.Авторское свидетельство СССР 285509, кл. Н 02 М 7/52, 1969. 3.Патент франции № 1281153, кл. Н 02 М 7/52, 1970. 4.Авторское свидетельство СССР 517133, кл. Н 02 Р 13/18, 1977.

0

52

ШТШ

У

ft 30 SI фиеЗ

Авторы

Даты

1981-09-15—Публикация

1978-06-05—Подача