(54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ДИСПЕРСИИ СЛУЧАЙНЫХ ПР ОЦЕССОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Статистический анализатор | 1981 |

|

SU1003096A1 |

| Устройство для измерения среднего значения и дисперсии циклической случайной величины типа фазы | 1975 |

|

SU767662A1 |

| Комплексное устройство контроля параметров | 1988 |

|

SU1520482A1 |

| Тензометрическое устройство | 1991 |

|

SU1796890A1 |

| Устройство для определения дисперсии | 1979 |

|

SU960844A1 |

| ПРИЕМНИК ДЛЯ РЕЛЬСОВОЙ ЦЕПИ | 1996 |

|

RU2104199C1 |

| Устройство для определения дис-пЕРСии НЕСТАциОНАРНОгО СлучАй-НОгО пРОцЕССА | 1979 |

|

SU798869A1 |

| УСТРОЙСТВО ДЛЯ РЕШЕНИЯ ЗАДАЧ НЕЛИНЕЙНОГО СТОХАСТИЧЕСКОГО ПРОГРАММИРОВАНИЯ | 1991 |

|

RU2006933C1 |

| Устройство для вычисления оценок математического ожидания и дисперсии | 1983 |

|

SU1280392A1 |

| УСТРОЙСТВО ОБРАБОТКИ ЦВЕТНЫХ ИЗОБРАЖЕНИЙ | 1999 |

|

RU2159958C1 |

1

Изобретение относится к статистическому анализу случайных процессов и может быть использовано для разработки специализированных вычислительных блоков, предназначенных для работы со случайными сигналами, в измерительных системах статистического анализа.

По основному авт. св. № 377704 известно устройство для вычисления дисперсии случайных процессов, содержащее первый блок вычитания, выход которого через квадратор подключен ко входу первого интегратора, первый выход первого блока задержки соединен с первым входом первого блока вычитания, вторые входы первого блока/ вычитания и первого блока задержки. объединены и являются входом устройства 1 .

Известное устройство определяет дисперсию случайных процессов (второй момент).

Цель изобретения г- расширение функ циональных возможностей устройства за счет вычисления моментов выше второго порядка.

Поставленная цель достигается тем/ что в устройство для вычисления дисперсии случайных процессов введены четыре блока задержки, четыре блока

вычитания, сумматор, два блока умножения и два интегратора, при зтом второй выход первого блока задержки через второй блок задержки подключен к первому входу второго блока вычитания и ко входу третьего блока задержки, выход третьего блока задержки соединен с первым входом третьего блока вычитания, второй вход которо10го объединен со вторым входом второго блока вычитания и является входом устройства, выход квадратора непосредственно и через четвертый блок задержки подключен соответственно к

15 первому и второму входам четвертого, блока вычитания, выход которого соединен с первым входом блока умножения, второй вход которого подключен к выходу второго блока вычитания, выход

20 первого блока умножения соединен со входом второго интегратора, с первым входом пятого блока вычитания И через пятый блок задержки со вторым входом пятого блока вычитания,

25 которого соединен с первым входом второго блока умножения, выход которого подключен ко входу третьего интегратора, второй вход второго блока умножения соединен с выходом сумматора, первый и второй входы которого

30

подключены соответственно к выходам первого и третьего блоков вычитания.

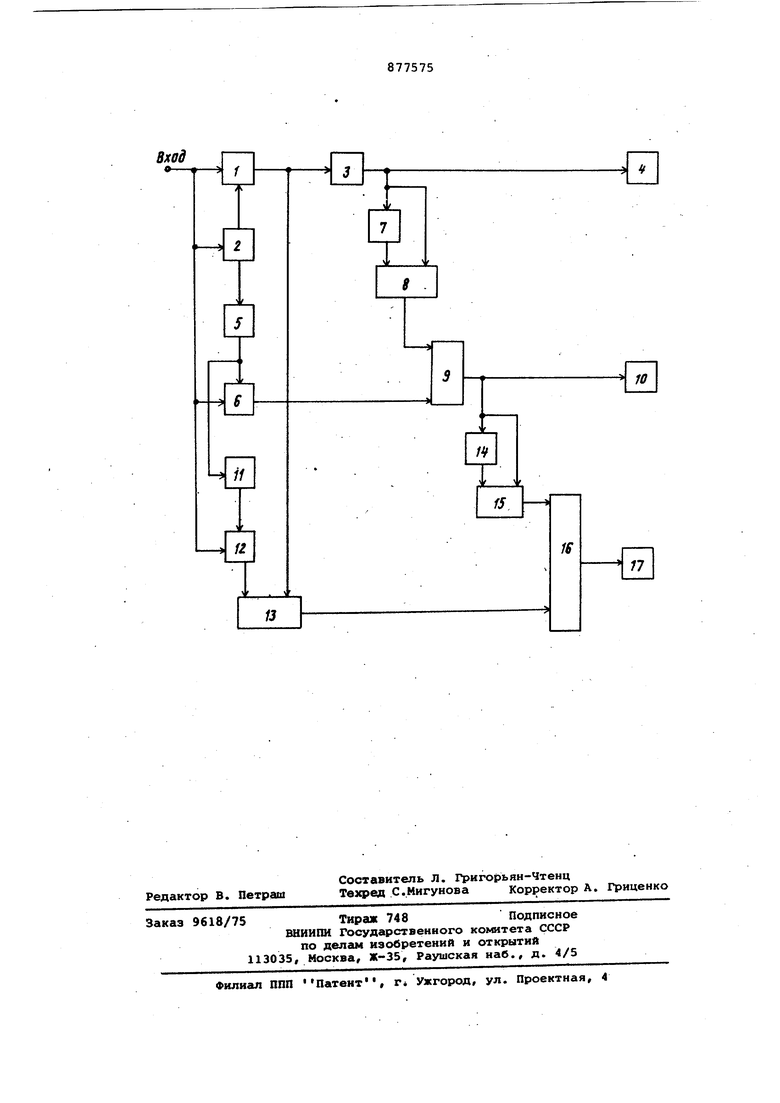

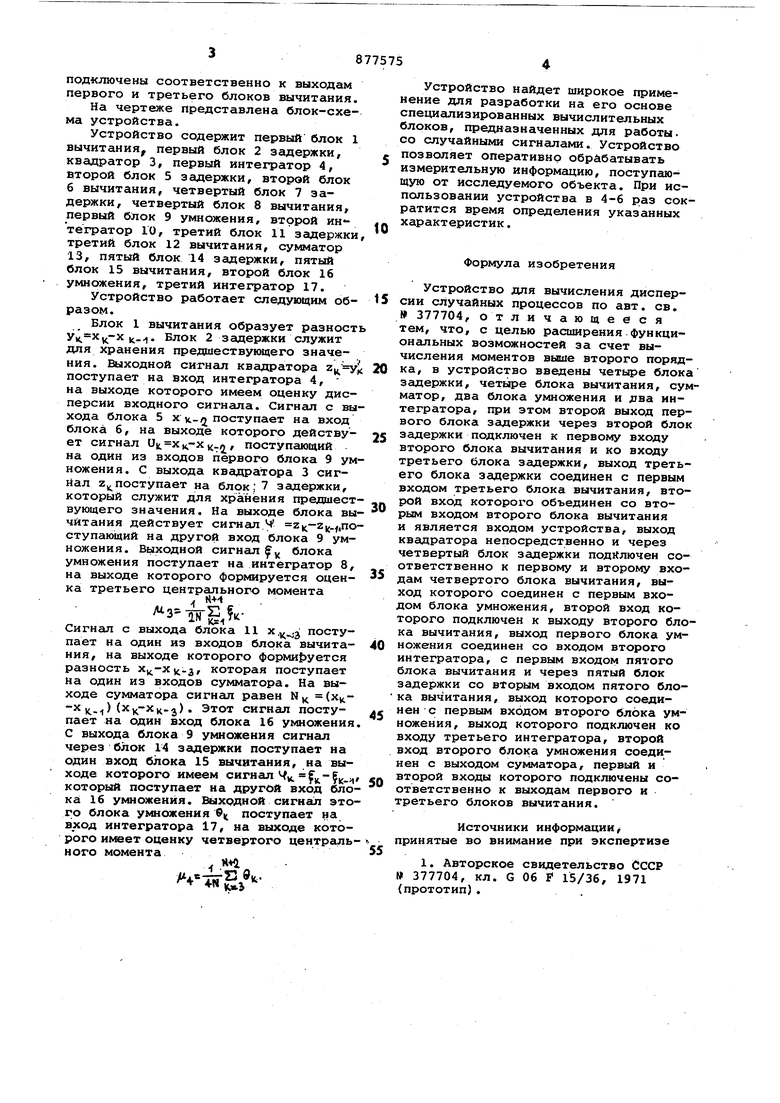

На чертеже представлена блок-схема устройства.

Устройство содержит первый блок 1 вычитания, первый блок 2 задержки, квадратор 3, первый интегратор 4, второй блок 5 задержки, второй блок б вычитания, четвертый блок 1 задержки, четвертый блок 8 вычитания, первый блок 9 умножения, второй интегратор 10, третий блок II задержки, третий блок 12 вычитания, сумматор 13, пятый блок 14 задержки, пятый блок 15 вычитания, второй блок 16 умножения, третий интегратор 17.

Устройство работает следующим образом.

Блок 1 вычитания образует разность у Хц-Хц.. Блок 2 задержки служит для хранения предшествующего значения. Выходной сигнал квадратора поступает на вход интегратора 4, на выходе которого имеем оценку дисперсии входного сигнала. Сигнал с выхода блока 5 х к-( поступает на вход блока б, на выходе которого действует сигнал UK. х ,-х к-/ / поступающий на один из входов первого блока 9 умножения. С выхода квадратора 3 сигнал Zjj поступает на блок; 7 задержки, который служит для хранения предшествующего значения. На выходе блока вычитания действует сигнал М (.,пoступающий на другой вход блока 9 умножения. Выходной сигнал блока умножения поступает на интегратор 8, на выходе которого формируется оценка третьего центрального момента . K+-t

-W,Сигнал с выхода блока 11 x.j поступает на один из входов блока вычитания, на выходе которого форми{ уется разность )4-з/ которая поступает на один из входов сумматора. На выходе сумматора сигнал равен N (xц-x .) (.j). Этот сигнал поступает на один вход блока 16 умножения С выхода блока 9 умножения сигнал через блок 14 задержки поступает на один вход блока 15 вычитания, на выходе которого имеем сигнал Ч который поступает на другой вход блока 16 умножения. Выходной сигнал этого блока умножения 9 поступает на вход интегратора 17, на выходе которого имеет оценку четвертого центрального момента

.

,«Устройство найдет широкое применение для разработки на его основе специализированных вычислительных блоков, предназначенных для работы, со случайными сигналами. Устройство позволяет оперативно обрабатывать измерительную информацию, поступающую от исследуемого объекта. При использовании устройства в 4-6 раз сократится время определения указанных характеристик.

Формула изобретения

Устройство для вычисления дисперсии случайных процессов по авт. св. 377704, от л и чающееся тем, что, с целью расширения функциональных возможностей за счет вычисления моментов выше второго порядка, в устройство введены четыре блока задержки, четыре блока вычитания, сумматор, два блока умножения и два интегратора, при этом второй выход первого блока задержки через второй блок задержки подключен к первому входу второго блока вычитания и ко входу третьего блока згцхержки, выход третьего блока задержки соединен с первым входом третьего блока вычитания, второй вход которого объединен со вторым входом второго блока вычитания и является входом устройства, выход квадратора непосредственно и через четвертый блок задержки подключен соответственно к первому и второму входам четвертого блока вычитания, выход которого соединен с первым входом блока умножения, второй вход которого подключен к выходу второго блока вычитания, выход первого блока умножения соединен со входом второго интегратора, с первым входом пятого блока вычитания и через пятый блок задержки со вторым входом пятого блока вычитания, выход которого соединен с первым входом второго блока умножения, выход которого подключен ко входу третьего интегратора, второй вход второго блока умножения соединен с выходом сумматора, первый и второй входы которого подключены соответственно к выходам первого и третьего блоков вычитания.

Источники информации принятые во внимание при экспертизе

Авторы

Даты

1981-10-30—Публикация

1980-02-18—Подача