(54) СЕЛЕКТОР ИМПУЛЬСОВ ПО ПЕРИОДУ СЛЕДОВАНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| ИЗБИРАТЕЛЬНОЕ УСТРОЙСТВО ИДЕНТИФИКАЦИИ ВЫЗОВА ОТ АБОНЕНТА | 1998 |

|

RU2136050C1 |

| Устройство магнитной записи и воспроизведения двухчастотных сигналов | 1983 |

|

SU1129648A1 |

| Селектор импульсов по периоду следования | 1980 |

|

SU911717A1 |

| Селектор импульсов по длительности | 1983 |

|

SU1150746A1 |

| Селектор импульсов | 1976 |

|

SU699665A2 |

| Селектор импульсов | 1984 |

|

SU1226638A1 |

| Устройство для управления автономным инвертором | 1990 |

|

SU1810973A1 |

| Устройство для обнаружения ошибок при передаче данных по телефонному каналу | 1989 |

|

SU1755377A1 |

| СЕЛЕКТОР ИМПУЛЬСОВ | 2011 |

|

RU2474043C1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО ПОИСКА СИГНАЛОВ РАДИОСТАНЦИЙ | 1998 |

|

RU2132111C1 |

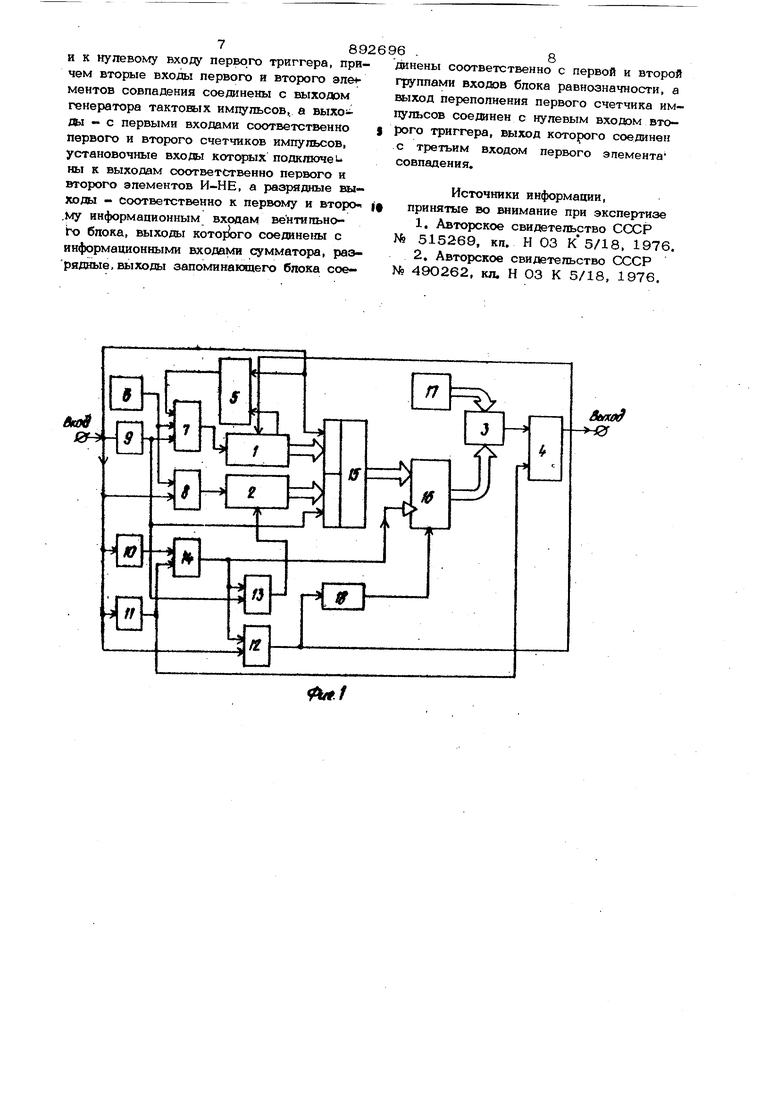

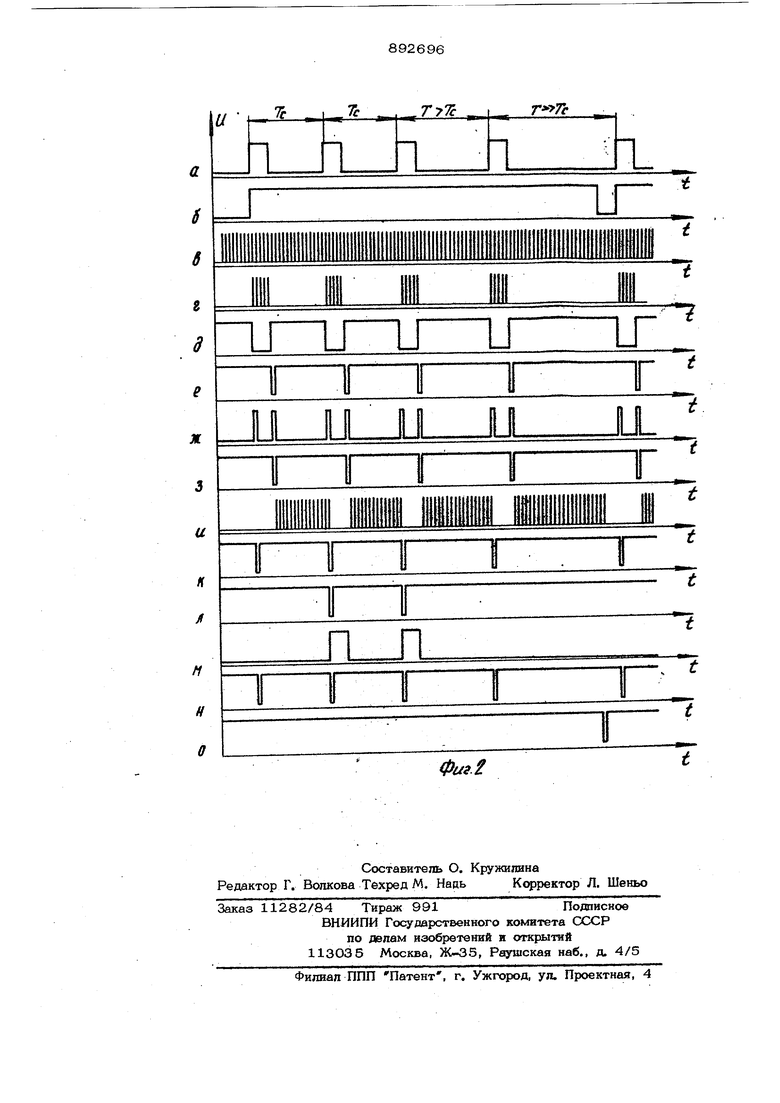

Изобретение относится к цмпупьсной технике, в частности к селекторам импупь сов по период спедования, и может быть использовано в радиотехнических устройствах дпя разделения совокупности серий импугаьсов. Известен селектор импульсов по периору спедования, содержащий два сдвиговых регистра, элемент запрета, элемент ИЛИ, клапан, генератор тактовых импульсов, три формирователя импульсов и элемент совпадения Г. Недостатком данного селектора является недостаточно высокая точность селектирования. Наиболее близким по технической сущности к предлагаемому является селектор импульсов по периоду следования, содержащий два счетчика импульсов, блок равнозначности, выход которого соединен.с единичным входом первого триггера, генератор тактовых импульсов, второй триггер и два элемента совпадения, причем, вход первого элемента совпадения под ключен к выходу инвертора, а первый вход второго элемента совпадения подключен к входной шине 21. Недостатком известного селектора является низкая точность селекции, так как в нем не исключен(а возможность выделения импульсов, временной интервал меж fjy которыми больше заданного. Цель изобретения - повьшение точности селекции. Поставленная цель достигается тем, что в селектор импульсов по периоду спедования, содержащий два счетчика импуль- сов, блок равнозначности, выход которого соединен с единичным входом первого триггера, генератор тактовых импульсов, второй триггер и первый и второй элемен- ты совпадения, первые входы которых подк тючеНы соответственно к №1ходу инвертора и к входной шине, введены сумматор, вентильный блок, элемент задержки,, запо-, минающий блок, элементы И-НЕ и формирователи переднего и заднего фронтов входных импульсов, входы которых средаг 38 йены с входаой шиной, с первым входом элемента И-НЕ, с входом инвертора, единичным входом второго триггера и с первым потенциальным входом вентильного блока, второй потенциальный вход которого соединен с выходом инвертора и с первым входом второго элемента И-НЕ, второй вход которого соединен с вторым вхо дом первого элемента-И-НЕ, выход которого через элемент задержки подключен к установочному входу сумматора, с тактовым входом сумматора и выходом третьего элемента И-НЕ, первых вход которого подключен к выходу формирователя переднего фронта входных импульсов, а второй вход - К выходу формирователя . заднего фронта входных импульсов и к нулевому входу первого триггера, пртчем вторые входы первого и второго элементов совпадения соединены с выходом гене ратора тактовых импульсов, а выходы - с первыми входами соответственно первого и второго счетчиков импульсов. Установочные входы которых подключены к выходам соответственно первого и второ- го элементов И-НЕ, а разрядные выходысоответственно к первому и второму информационным входам вентильного блока, Шз1Ходы которого соединены с информационными входами сумматора, разрядные выходы которого и разрядные аыходы запоминающего блока соединены соответственно с первой и второй группами входов блока равнозначности, а выход переполнения первого счетчика импульсов соединен с нулевым входом второго триггера, выход которого соединен с третьим входом первого элемента совпадения . На фиг. 1 представлена структурная схема предлагаемого устройства; на фиг. временные диаграммы, поясняюище его работу. Устройство содержит счетчики 1 и 2 импульсов, блок 3 равнозначности, триггеры 4 и S, генератор 6 тактовых импул сов, элементы 7 и 8 совпадения, инвертор 9, формирователи 10 и 11 соответст венно переднего и задаёго фронтов входных импульсов, элементы И-НЕ 12-14, вентияьшь:й блок 15, сумматор 16 нако пительный, запоминающий блок 17, элемент 18 задержки. Селектор импульсов по периоду следования работает следующим образом. В исходаом положении триггеры 4 и 5 находятся в нулевом состоянии (низкий уровень напряжения на прямом выходе триггера). Импульсы на входе селектора отсутствуют. При этом, элементы 7 и. 6 8 закрыты низким уровнем напряжения соответственно но третьему и первому ахода м, блокируя тем самым поступление тактовых импупьсов на входы счетчиков 1 и 2. При поступлении входной последовательности импульсов (фиг. 2а) на вход селектора первым импульсом триггер 5 переводится в единичное состояние (фиг.2б) открывая тем самым элемент 7 по третьему входу, а элемент 8 Входным импульсом открывается по первому входу и тактовые импульсы (фиг. 2в) с выхода генератора 6 через него (фиг. 2 г) поступают на вход счетчика 2. В счетчике 2 длительность входных импульсов преобразуется в цифровой код, представляющий собой число тактовых импульсов, поступивших на вход счетчика за время действия входного импульса. В это время на вход счетчика 1 тактовые импульсы не поступают, так как элемент 7 закрыт по первому входу низким уровнем напряжения (фиг. 2д),поступающим с выхода инвертора 9, По заднему фронту входного импульса срабатывает формирователь 11 и на его выходе формируется короткий отрицательный импульс (фиг. 2е), который поступает на второй вход элемента 14, закрывая его на время, соответст: ющее длительности этого импульса. На выходе элемента 14 устанавливается аысокий уровень напряжения (фиг. 2ж), который поступает на тактовый вход сумматора 16. После окончания входного импульса на втором потенциальном входе блока 15 устанавливается высокий уровень напряжения, поступающий с выхода инвертора 9, и информация из счетчика 2 через блок 15 поступает на информационные входы сумматора 16, Эта информация перепадам от низкого потенциала к высокому на тактовом входе последнего запоминается в данном сумматоре. После запоминания данной информации в сумматоре 16 на выходе элемента 13 устанавливается низкий уровень напряжения (фиг. 2з), так как он в это время откроется по обоим входам. Низкий уровень напряжения с выхода элемента 13 поступает на установочный вход счетчика 2, обнуляя его с целью подготовки и иэмерению очередного входного импульса. В промежутке между входными импульсами элемент 7 отк|м 1Бается и по первому Rxopy. Тактовые импульсы с выхода генератора 6 через элемент 7 (фиг. 2и) поступают на вход счетчика 1. В последнем интервал входными импульсами преобразвуется в цифровой код, представляющий собой число тактовых импульсов, поступивших на счетчика на прютяже- НИИ интервала межру импульсами, В момент прихода очередного входного имщп са блокируется дальнейшее поступление тактовых импульсов на вход счетчика . 1, а также запускается формирователь Ю. На выходе последнего формируется короткий отрицательный импульс (фиг. 2к), который закрывает элемент 14 по первому входу и на выходе постюднего устанавливается высокий уровень напряжения (фиг. 2ж), который поступает на тактовый вход сумматора 16. Так как в это время на первом потенциальном входе блока 15 присутствует входной импульс (высокий уровень напряжения), то информация с выхода счетчика 1 через блок 15 поступает на информацгюнные входы сумматора 16, где по перепаду потенциала от низкого уровня к высокому на его тактовом входе суммируется с предыдущей информацией, поступившей ранее с выхода счет чика 2 импульсов. После суммирования указанных информации на выходе элемента 12 устанавливается низкий уровень напряжения (фиг. 2и), так как он в это время открыт по обоим входам. Низкий уровень напряжения с выхода элемента 12 поступает на установочный вход счетчика 1 в нупевое состояние, обнупяя его с цепью подготовки к измерению очередного интервала меж.ру импульсами, а через элемент 18 - на установочный вход сумматора 16 При этом время задержки элемента 18 должно удовлетворять условию tr(i, . где t ц { - время задержки сигнала в сумматоре; fviH минимальная длительность импульса входной последовательности.

В дальнейшем процессе работы сепек-. тора может быть три случая,

В случае равенства заданного периода - Tjv селектируемых импульсов и периода Т следования импульсов входной последовательности на выходе блока 3 равнозначности устанавливается низкий уровень напряжения (фиг. 2л), так как заданный код который записан и хранится в запоминающем блоке 17 равен суммарному коду сумматора 16. Низкий уровень напряжения с выхода блока 3 поступает на единичный вход триггера 4 и последний устанавливается в единичное состояние (фиг. 2м). В дальнейшем процесс работы устройства повторяется, а триггер 4 импульсом с выхода формирователя 11 возвращается в нулевое состояние. Следовательно, на выходе селектора выделяются импульсы, период следования которых равен заданному периоду и длительностью, соответствукацей входным импульсам.

Если T(v Т или TC Т, то код, хранящийся в блоке 17 и суммарный код сумматора 16 не равны и триггер 4 не может установиться в едатачное состояние, т.е. импульсы на шлхода устройства

будут отсутствовать.

Если Т 7Tj., то на сигнальном выходе счетчика 1 появляется отртдательный импульс (фиг. 2е), которым триггер 5 переводится в ну;юБое состояние (фиг. 26) и

низкий уровень напряжения с прямого выхода последнего поступает на третий вход элемента 7, блокируя тем самым дальнейшее поступление тактовых импульсов на вход счетшка 1. При поступлении очередного входного импульса триггер 5 устанавливается обратно в еданичное состояние, а также происходат обнуление счетчика 1.

Выделение новых элементов и связей

между ними повышает точность селекции. Формула изобретения

Селектор импульсов по периоду следования, содержащий два счетчнка импульсов, блок равнозначности, выход которого соединен с единичным входом первого триггера, генератор тактовых импульсов,, второй триггер и перкьгй и второй элементы совпадения, первые входы кото-

рых подключены соответственно к выходу инвертора и к входной шине,отличают и и с я тем, что, с целью повышения ТОЧНОСТИ селекции, введень сумматор, вентильный блок, элемент задержки, запоминающий блок, элементы И-НЕ н формирователи переднего и заднего фронтов входных импульсов, входа которых соединены с входной шиной, с первым входом первого элемента И-НЕ, с входом инвертора, единичным входом второго триггера и с первым потенциальнь м входом вентильного блока, второй потенциальный вход которого соединен с выходом инвертора и с первым входом второго элемен-

та И-НЕ, второй вход которого соединен с вторым входом первого элемента И-НЕ, выход которого через элемент задерж--ки подапючен к установочному входу сумматора, с тактовым входом сумматора и выходом третьего элемента И-НЕ, первый вход которого подключен к выходу формирователя пере;5него фронта входных импульсов, а второй вход - к выходу формирователя заднего фронта входных импупьсоь и к нулевому входу первого триггера, причем вторые входы первого и второго эленментов совпадения соединены с выходом генератора тактовых импульсов,, а выхо ям - с первыми входами соответственно первого и второго счетчиков импульсов, установочные входы подключен ны к выходам соответственно первого и второго элементов И-НЕ, а разрядные выходы - соответственно к первому и второ .My информапионным входам вентипьноtx) блока, выходы которого соедине а1 с информационными входами сумматора, раэ рядные, вы ходы запоминающего блока сое896 . динены соответственно с первой и второй группами входов блока равнозначности, а вь1ход переполнения первого счетчика импульсов соединен с нулевым входом второго триггера, выход которого соединен с третьим входом первого элементасовпадения. Источники информации, принятые во внимание при экспертизе 1,Авторское свидетельство СССР № 515269, кп. Н 03 К 5/18, 1976. 2,Авторское свидетельство СССР No 49О262, кл. Н 03 К 5/18, 1976.

и I I I 11 fLR

Фиа ги LT IL t

Авторы

Даты

1981-12-23—Публикация

1980-04-17—Подача