(54) даФРОВОЙ АНАЛИЗАТОР СПЕКТРА

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления и стабилизации параметров выходного напряжения преобразователя | 1984 |

|

SU1274094A1 |

| Цифровой анализатор спектра | 1986 |

|

SU1404968A1 |

| Анализатор спектра | 1977 |

|

SU732759A1 |

| Анализатор квазипериодических сигналов | 1983 |

|

SU1166007A1 |

| Анализатор спектра по функциям Уолша | 1985 |

|

SU1282157A1 |

| Цифровой анализатор спектра | 1979 |

|

SU798615A1 |

| Устройство для анализа периодических сигналов | 1981 |

|

SU978066A1 |

| Цифровой анализатор спектра по функциям Хаара | 1980 |

|

SU953586A1 |

| Цифровой анализатор спектра | 1984 |

|

SU1190283A1 |

| Анализатор спектра Уолша | 1990 |

|

SU1809447A1 |

t

Изобретение относится к радиоиз мерительной технике и может быть не пользовано в радиотехимсе при прове дении спектрального анализа электрических сигналов.

Известен анализатор спектра, содержащий последовательно соединенные генератор тактовых импульсов генератор базисных функций блок умножителей и блок интеграторов СП.

Однако данное устройство имеет ограниченный диапазон . анагшзируемых частот.

Наиболее близким к предлагаемому по технической суврюсти и достигаемому результату является анализатор спектра по функциям Уолша, содержащий последовательно соединен-ные аналого-цифровой преобразователь, умножитель, нерекурсивные блоки, состоящие из линий задержки, сумматора и аычитателя, нерекурсивные бло;ча объединены парами 2.

Недостаткст известного анализатора является низкое быстродействие. Это связано с тем, что увеличение точности вычисления коэффициентов ведет к згвеличению разрядности обрабатываемых двоичных кодов и, следовательно, увеличивается время их суммирования и вычитания о Увеличение точности аппроксимации ведет к росту числа нерекурсивных блоков. Все это ограничивает диапазон анализируемых частот, быстродействие. Кроме того, конструкция данного анализатора сложна.

Цель изобретения - повышение быстродействия.

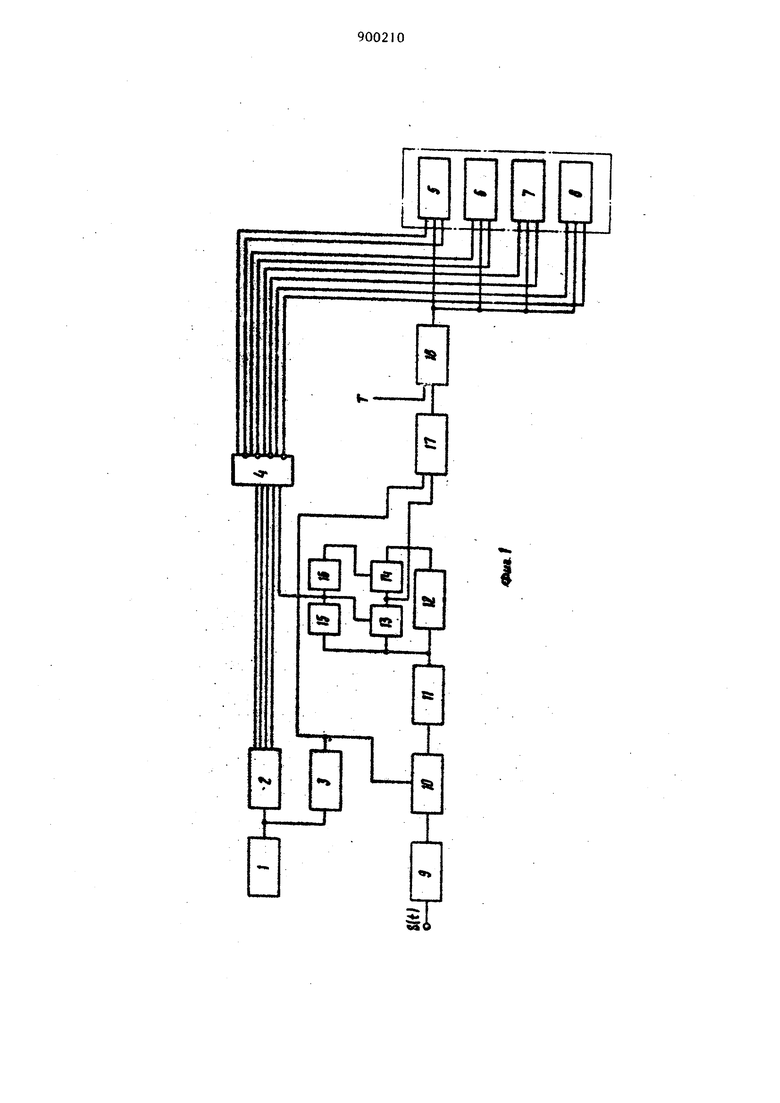

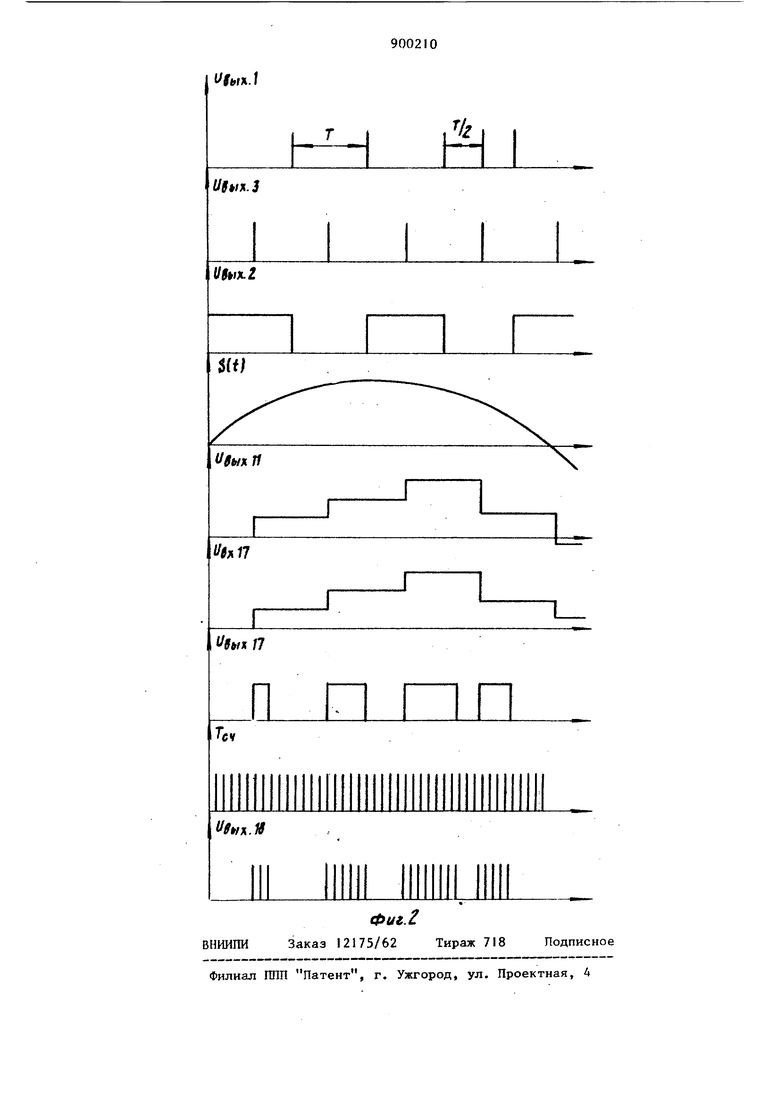

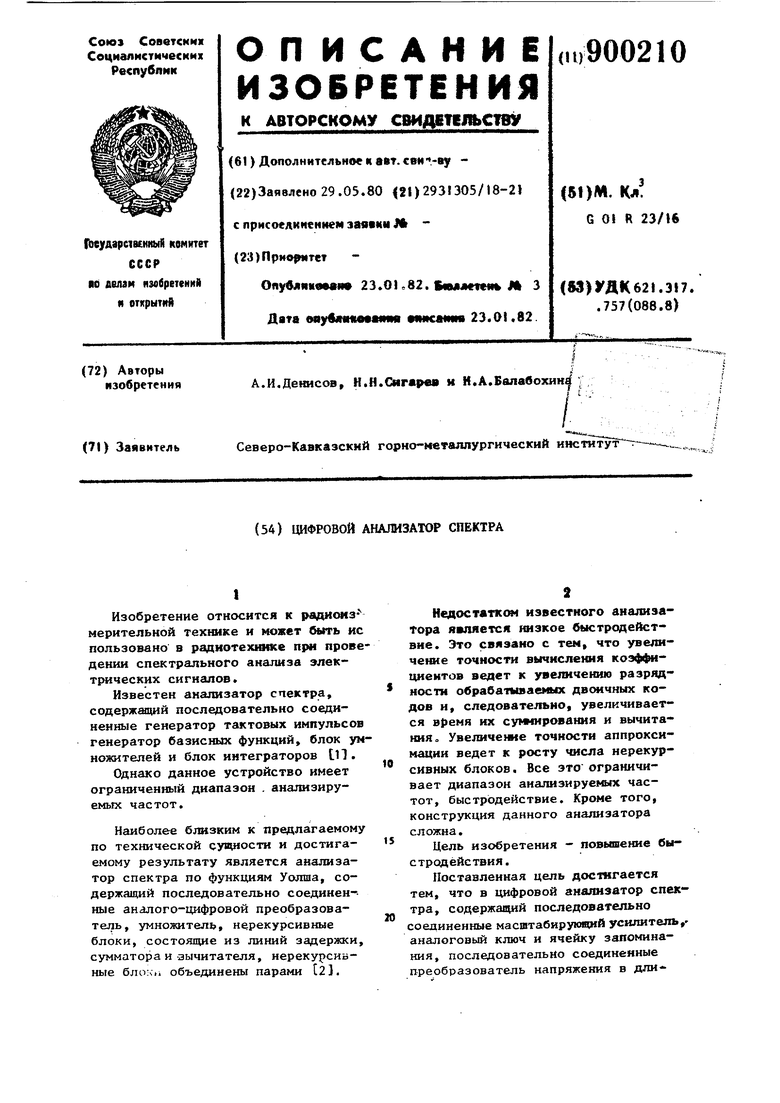

Поставленная цель достигается тем, что в цифровой анализатор спектра, содержащий последовательно соединенные масштабирующий усилитель,аналоговый ключ и ячейку запоминания, последовательно соединенные преобразователь напряжения в длительность и элемент И, регистрирующий прибор введены блок равнозначность , элемент задержки, после довательно соединенные генератор тактовых импульсов и генератор функ ций Уолша, а также подключенный к ячейке запоминания усилитель и параллельно соединенные с ним последовательно связанные два ключа и два усилителя, выходы которых связаны с управляющими входами ключей, а регистрирующий прибор выполнен на основе реверсивных счетчиков, информационные входы которых соединены с выходами блока равнозначность, средняя точка усилителей соединена с первыми входами блока равнозначность, вторые входы которых соединеньис соответствующими в ходами генератора функций Уолша, вход элемента задержки соединен с выходом источника тактовых импульсов, а выход т со вторым входом ана логового ключа и с первым входом преобразователя напряжения в длительность, .второй вход которого сое динен со средней точкой двух ключей а выход элемента И - со счетными входами реверсивных счетчиков. На фиг. 1 приведена структурная схема цифрового анализатора спектра; на фиг. 2 - временные диаграммы процесса его работы. /Цифровой анализатор спектра (фиг. 1) содержит генератор 1 тактовых импульсов, генератор 2 функци Уолша, элемент задержки 3, логический блок разнозначность 4, реверсивные счетчики 5-8 регистрирующего прибора, а также масштабирующий уси литель 9, ключ 10, ячейку 11 запоминания, усилитель 12 и параллельно соединенные с ним два последовател но связанных ключа 13 и 14 и два ус лителя 15 и 16, преобразователь 17 напряжения в длительность и логичес кий элемент И 18, включенные в состав аналого-цифрового преобразователя. Анализатор спектра работает в сл чае определения первых четырех коэф фициентов Уолша следующим образом. Тактовые импульсы с выхода генер тора 1 тактовых импульсов поступают на вход генератора 2 функций Уол ша и на вход элемента задержки 3, который осуществляет сдвиг тактовой последовательности на половину пери ода, этими импульсами управляется 04 ключ 10, на который через масштабирующий усилитель 9 подается исследуемый сигн.ял. В ячейке 11 запоминания запоминается соответствующая выборка входного сигнала. Этот сигнал поступает на вход блока преобразования положительных и отрицательных входных сигналов в уровень положительного напряжения, причем, если сигнал положительный, то со средней точки усилителей 15 и 1Ь снимается уровень потенциала, равный 1, если сигнал отрицательный, то снимается О , а со средней точки ключей 13 и 14 подается уровень положительного напряжения, поступающий в преобразователь 17 напряжения в длительность, на второй вход которого поступают импульсы с элемента задержки 3, запускающие развертку, и происходит преобразование напряжения в пропорциональный временной интервал. С выхода логического элемента И 18 на счетные входы реверсивных счетчиков 5-8 поступают импульсы, число которых пропорционально выборке исследуемого сигнала. Сигнал, соответствующий высокому или 1шзкому уровню потенциала, снимаемый со средней точки усилителей 15 и 16 поступает на вход логического блока разнозначность 4, на другие входы которого поступают импульсы от генератора 2 функций Уолша. Если значения выборки и функции Уолша отрицательны, соответствующие логическому О или положительные значения, соответствукицие 1, то в реверсивных счетчиках. 5-8 происходит суммирование счетных импульсов. При несовпадении значений выборки и функций Уолша происходит вычитание импульсов. С выхода реверсивных счетчиков 5-8 по окончанию периода разложения снимаются значения спектральных коэффициентов. Время задержки, ограничивающее быстродействие известного, состоит из времени задержки параллельного сумматора или вычитателя со сквозным переносом. / ts te(N-1) t t t задержка в элементе И-ИЛИ задержка счетного триггера; посточпная линия задержки; число ра.рядов.

IIoci

ояиная jmnHH из yr:иония: рается

t

де ty - длительность разрядного

импульса, поступающего на вход сумматора.

Минимальная длительность разрядых импульсов

ty (N-l)t.

При обработку четырех |(азрядных

исел

J

tu 3.50 НС 150 НС

гдэ 150 НС + 50 НС 200 не

t 3.50 НС + 50 НС + 200 не

400 НС. Общее время задержки

t,xj(H-1)tj

де п - порядок системы функций Уолша,

При и 4, т.е. при вычислении 16-ти коэффициентов Уолша.

tic«j 3.400 НС,

При увеличении разрядности обраатываемых чисел и повышении числа определяемьгх коэффициентов общее время .д.-Р ;ки будет увеличиваться В предлагаемом устройстве общее время задержки

3a,, ,

где t, - время задержки триггера, формирующего соответствующую функцию Уйлша-;

t - время задержки ячейки равнозначность J

tj - время задержки реверсивного счетчика.

50 нс+50 нс+50 не.

Причем при повышении точности и количества определяемых коэффициентов разложения в ряд Уолша время задержки остается постоянш 1М и зависит только от типа применяеьшх микросхем. Точность коэф(})ициента разложения в ряд Уолша определяется частотой счетных импульсов и разрядностью реверсивного счетчика, а точность аппроксимации входного сигнала определяется количеством используемых функций Уолша, каждой из которых соответствует своя ячейка равнозначность и реверсивный счетчик в регистрирующем приборе. В данном устройстве отсутствуют рабочие ячейки памяти, а оперативной памятью служат реверсивные счетчики.

Цифровой анализатор спектра отличается от известных тем, что в нем происходит параллельная обработка информации. Текущие значения выборок анализируемого сигнала суммируются и вычитаются в реверсивных счетчиках согласно знакам соответствующей функции Уолша и выборки сигнала, что позволяет увеличить быстродействие анализатора

Формула изобретения Цифровой анаашзатор спектра, содержащий последовательно соединенные масштабирующий усилитель, аналого,вый ключ и ячейку запоминания, последовательно соединенные преобразователь напряжения в длительность и элемент И, регистрирующий прибор, отличающийся тем, что, ,с целью повышения быстродействия, в него введены блок равнозначность элемент задержки, последов а т ельно соединенные генератор тактовых импульсов и генератор функций Уолша, а также подключенный к ячейке запоминания усилитель и параллельно соединенные с ним последовательно связанные два ключа и два усилителя, выходы которых связаны с управляющими входами ключей, а регистрирующий прибор выполнен на основе реверсивных счетчиков, информационные входы которых соединены с выходами блока равнозначность, средняя точка усилителей соединена с первь1ми. входами блока равнозначность, вторые входы которых соединены с соответствующими выходами генератора функций Уолша, вход элемента задержки соединен с выходом источника тактовых импульсов, а выход - со вторым входом аналогового ключа и с первым входом преобразователя напряжения и д:штельность, второй вход которого соединен со средней точкой двух ключей, а выход элемента И - со счетными входами реверсивных счетчиков.

Источники информации, принятые во внимание при экспертизе 1.зарубежная радиоэлектроника, М., Советское радио, 1 972,N 5,с, 18.

UetiK.3

t guxll

V

Авторы

Даты

1982-01-23—Публикация

1980-05-29—Подача