(5) УСТРОЙСТВО для ДИФФЕРЕНЦИАЛЬНОЙ ЗАЩИТЫ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для дифференциальной защиты | 1976 |

|

SU573835A2 |

| Устройство для дифференциальной защиты с блокировкой от внешних коротких замыканий | 1971 |

|

SU562033A1 |

| Устройство для дифференциально-фазной защиты электроустановки | 1987 |

|

SU1677762A1 |

| УСТРОЙСТВО ДИФФЕРЕНЦИАЛЬНОЙ ЗАЩИТЫ СИЛОВОГО ТРАНСФОРМАТОРА | 2012 |

|

RU2497256C1 |

| Устройство для защиты установки с параллельно включенными выпрямителями | 1983 |

|

SU1101962A1 |

| Устройство для дифференциально-фазной защиты | 1982 |

|

SU1113866A1 |

| Устройство для защиты фильтров высших гармоник | 1980 |

|

SU892571A1 |

| Устройство для дифференциальной защиты | 1988 |

|

SU1610533A2 |

| Устройство для дифференциальной защиты силового трансформатора | 1979 |

|

SU792462A1 |

| Устройство для контроля исправностиСОЕдиНиТЕльНыХ пРОВОдОВ пРОдОльНОйдиффЕРЕНциАльНОй ТОКОВОй зАщиТылиНии элЕКТРОпЕРЕдАчи | 1979 |

|

SU811387A1 |

I

Изобретение относится к электротехнике, а именно к устройствам для релейной защиты электрических систем, может использоваться,например, для осуществления защит генераторов, шин и линий электропередачи.

По основному авт.св. 573835 известно устройство, выполненное с блокировкой от внешних коротких замыканий, содержащее трансформаторы тока всех присоединений, на выход которых подключены, трансреакторы,вторичные обмотки которых объединены в две группы через вентили, датчики дифференциального тока, первичная обмотка которых включена последовательно с реле защиты, а вторичная - на выпрямительный мост, и логические элементы, в котором логические элементы соединены в две последовательные цепочки ЗАПРЕТ НЕ - В - НЕ, вход одной из которых через схемы И и элементы времени В

подключен к выходу каждой из двух групп вторичных обмоток трансреакторов, вход другой - на выпрямительный мост датчика дифференциального тока, причем выход каждой цепочки подключен к запрещающему входу элемента ЗАПРЕТ другой цепочки, два логических элемента ИЛИ и второй элемент И, входы первого логического элемента ИЛИ подключены к выходам

10 первой логической цепочки ЗАПРЕТ , НЕ - В - НЕ всех трех фаз, входы которого - к выходам второй логической цепочки ЗАПРЕТ - НЕ - В - НЕ, причем выходы ббоих логических эле15ментов ИЛИ через упомянутый логический элемент И подключены к запре щающим входам элемента ЗАПРЕТ первой логической цепочки трех фаз, а выход первого логического элемента ИЛИ

30 подключен к исполнительному органуtQ.

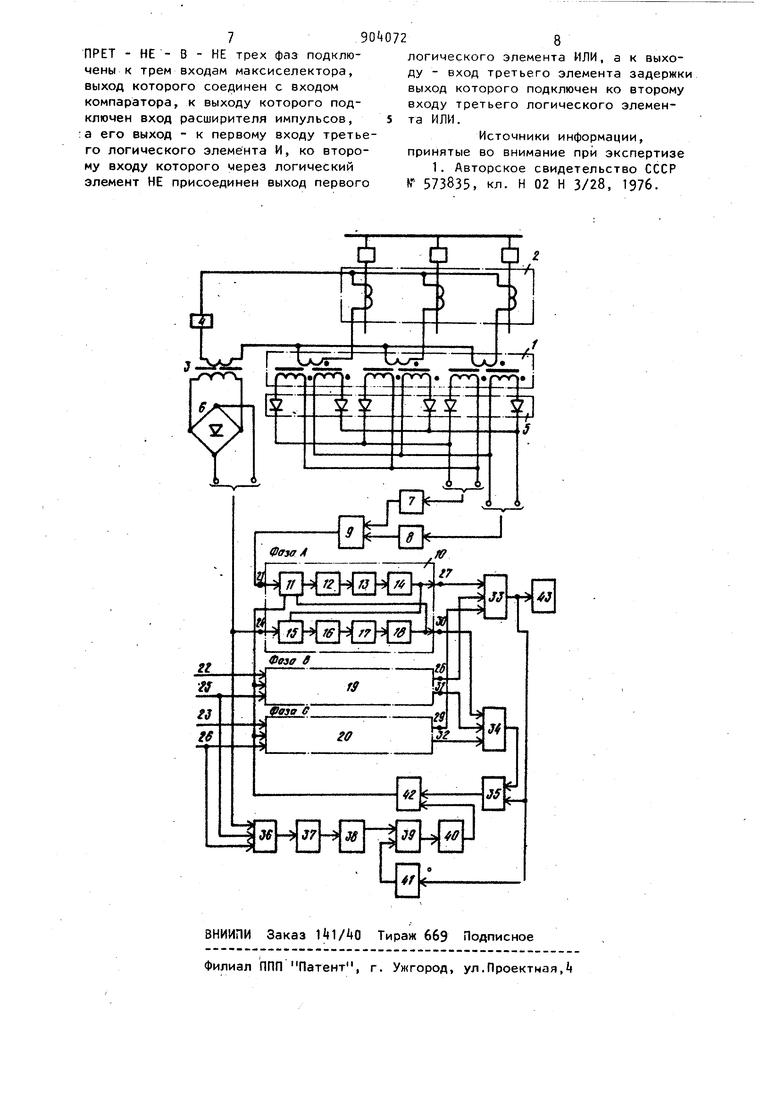

Недостатком данного устройства является ограниченность области его применения в сетях с включением защит линии на сумму токов двух и doлее присоединений, когда токи подпитки по защищаемой линий при внешнем коротком замыкании близки к токам короткого замыкания на этой лиНИИ. В этом случае необходимо отстраивать от этого тока подпитки, вторую логическую цепочку ЗАПРЕТ НЕ - В - НЕ, а первая логическая цепочка должна быть чувствительна в этом режиме. Поэтому при коротком замыкании а защищаемой зоне с током ниже порога срабатывания второй логической цепочки ЗАПРЕТ - НЕ - В - Н возможно срабатывание первой логичес кой цепочки, осуществляющей функцию блокирования защиты, Б случаях,если имеет место расхождение векторов электродвижущих сил генераторов, питающих место короткого замыкания, или из-за насыщения магнитопровода трансформатора тока одного из плеч защиты. Цель изобретения - повышение чув ствитеЛьности и эффективности функционирования при коротких замыкания в защищаемой зоне. Эта цель достигается тем,что устройство для дифференциальной защиты дополнительно снабжено максисе лектором, компаратором, расширителем импульсов, третьим логическим элементом И, третьим элементом задержки, логическим элементом НЕ и третьим логическим элементом ИЛИ, первый вход которого соединен с выходом второго логического элемента И, а выход - с запрещающими сходами элементов ЗАПРЕТ первых логических цепочек ЗАПРЕТ -НЕ - В - НЕ, причем входы вторых логических цепочек ЗАПРЕТ - НЕ - В - НЕ трех фаз подключен к трем входам максиселектора выход которого соединен с входом ко паратора,-к выходу которого подключен вход расширителя импульсов, а его выход - к первому входу треть его логического элемента И,ко второ му, входу которого через логический Элемент НЕ присоединен выход первог логического элемента ИЛИ, а к выходу - вход третьего элемента задержки, выход которого подключен ко вто рому входу третьего логического Элемента ИЛИ. Сущность изобретения поясняется Чертежом. На чертеже приведена функциональная схема предлагаемого устройства. Устройство содержит трансреакторы 1, включенные в цепи трансформаторов 2 тока, трансреакторы 3, включенные в дифференциальные цепи последовательно с реле i защиты, вентили 5 для формирования сигналов от дэтчиков фазных токов, выпрямитель 6 для формирования сигналов от датчиков дифференциальных токов, первый 7 и второй 8 элементы задержки, первый логический элемент И 9 логическую схему 10 одной фазы,включающую две логические цепочки ЗАПРЕТ - НЕ - В - НЕ соответственно И-12-13-14и15-1б-17-18, аналогичные цепочки 19 и 20 двух других фаз, входы 21-23 от датчиков фазных токов соответственно фаз А, В. и С входы 2k - 26 от датчиков дифференциальных токов, выходы 27 - 29 первых логических цепочек фаз А, & и С выходы 30 - 32 вторых логических цепочек фаз А , В и С первый 33 и второй 3 логические элементы ИЛИ, второй логический элемент И 35, максиселектор 36, компаратор 37,расширитель 38 импульсов, третий логический элемент И 39 третий элемент 40 задержки, логический элемент НЕ 41, третий логический элемент ИЛИ i}2, и исполнительный орган 3 блокировки защиты. Предлагаемое устройство работает следующим образом. В нормальном режиме реле k защиты и блокирующий орган отстроены по уставке от рабочих токов и поэтому не возбуждаются. Если уставки срабатывания первых логических цепочек (11-14), блокирующих защиту, выбраны выше, чем вторых (15-18), запрещающих блокированные защиты, то при использовании в сетях, где ток подпитки внешнего короткого замыкания,по защищаемой линии по крайней мере вдвое меньше тока в плече с минимальным током, устройство блокирует защиту при внешних коротких замыканиях на время, определяемое уставкой элемента 13 времени в первых логических цепочках (11-14); разрешает срабатывать защите при коротких замыканиях 8 защищаемой зоне, так как срабатывает вторая логическая цепочка (), блокирующая первую и 5ЭО запрещающая срабатывание исполнител ного органа 3 блокировки; деблокирует защиту без задержки, если произошел переход внешнего короткого за мыкания в защищаемую зону, Во всех этих случаях вновь введе ная цепочка не оказывает влия ния на работу устройства, так как пр внешних ксзротких замыканиях срабатывает блокировка, логическая единица с выхода 33 проходит на вход логи.ческого элемента НЕ , с выхода ко торого логический нуль поступает на второй вход логического элемента И 39 запрещая прохождение сигнала по первому входу 39 через элемент задер ки 40 и логический элемент ИЛИ Ц2 на сброс блокировки. При коротком замыкании в защищаемой зоне указанная цепочка срабатыва ет и вместе со второй логической цепочкой () запрещает блокирова ние защиты, В тех случаях, когда ввиду указанных выше особенностей первичной сети уставку срабатывания первой логической цепочки (11-Н) выбирают ниже уставки срабатывания второй логической цепочки (15-18),устройство работает следующим образом, При внешнем коротком замыкании ;срабатывает первая логическая цепочк I запрещая срабатывание второй логической цепочки и дополнительной цепочки (), При коротком замыкании в защищаемой зоне с током ниже уставки срабатывания второй логической цепочки (15-18) и выше уставки срабатывёния первой логической цепочки (11-1) последняя не срабатывает в начале процесса короткого замыкания до возможного насыщения магнитопровода одного из трансформаторов 2 тока или расхождения по фазе - векторов электродвижущих сил генераторов,питающих место короткого замыкания,т,е :неменее 5 мс, 3 течение этого интервала времени срабатывает компаратор 37 с уставкой ниже, чем у первой логической цепочки (11-Т), Сигнал с выхода компаратора 37 расширяется в расширителе 38 на время мс для исключения сбросов в процессе работы, и подается на первый вход третьего логического элемента И 35Так как первая логическая цепочка (11-И) не сработала, то на выходе первого логического элемента ИЛИ 33 - логический нуль, а на выходе логического элемента НЕ 41 - логическая единица, которая поступает на второй вход элемента И 39- Совпадение логических единиц на входе третьего ло-. гического элемента И 39 обуславливает появление единицы на его выходе. В элементе задержки kO осуществляг ется задержка в появлении сигнала на втором входе третьей логической схемы ИЛИ 42 на +-5 мс. Сигнал с выхода схемы ИЛИ Ц2 поступает на запрещающие входы элементов ЗАПРЕТ первых логических цепочек . (11-14) всех трех фаз, предотвращаявозможность срабатывания блокировки защиты. Задержка на Ц-S мс введена для того, чтобы при внешних коротких замыканиях,когда оказываются чувствительными первая логическая цепочка, осуществлякнцая блокирование защиты,и комларатор 37 вновь введенной цепи, исключить возможность запрета в ера батывании блокировки, I Предлагаемое устройство может Использоваться для защиты генераторов шин и линий, включенных через два и более выключателя. Экономическая целесообразность предлагаемого изобретения заключается в том, что повышается избирательность защиты и исключаются неправильные отключения защищаемых объектов,приводящие к ущербу, связанному с недоотпуском электроэнергии потребителям. Формула изобретения Устройство для дифференциальной защиты по авт.св. If 573835, отличающееся тем, что, с целью ; повышения чувствительности и эффективности функционирования при коротких замыканиях в защищаемой зоне, оно дополнительно снабжено максиселектором, компаратором, расширителем импульсов, третьим логическим элементом И, третьим элементом задержки, логическим элементом НЕ и третьим логическим элементом ИЛИ, первый вход которого соединен с выходом второго логического элемента И, а выход с запрещающими входами элементов ЗАПРЕТ первых логических цепочек ЗАПРЕТ - НЕ - В - НЕ, причем входы вторых логических цепочек ЗАПРЕТ - НЕ - В - НЕ трех фаз подключены к трем входам максиселектора, выход которого соединен с входом компаратора, к выходу которого подключен вход расширителя импульсов, ;а его выход - к первому входу третьего логического элемента И, ко второму входу которого через логический элемент НЕ присоединен выход первого 90 8 логического элемента ИЛИ, а к выходу - вход третьего элемента задержки выход которого подключен ко второму входу третьего логического элемента ИЛИ. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР К 573835, кл. Н 02 Н 3/28, 1976.

Авторы

Даты

1982-02-07—Публикация

1980-06-26—Подача