(54) ЧАСТОТНО-ФАЗОВЫЙ ДЕТЕКТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| ТРАНЗИСТОРНЫЙ КЛЮЧ | 2005 |

|

RU2287219C1 |

| Стабилизированный конвертор | 1979 |

|

SU892425A1 |

| ЧАСТОТНО-РЕГУЛИРУЕМЫЙ ЭЛЕКТРОПРИВОД С НЕУПРАВЛЯЕМЫМ ЗВЕНОМ ПОСТОЯННОГО ТОКА | 1993 |

|

RU2067352C1 |

| Устройство для восстановления постоянной составляющей | 1990 |

|

SU1793558A1 |

| Приемно-излучающий тракт ультразвукового дефектоскопа | 1991 |

|

SU1805380A1 |

| Функциональный генератор | 1987 |

|

SU1469509A1 |

| УСТРОЙСТВО ТОКОВОЙ ЗАЩИТЫ ЭЛЕКТРОУСТАНОВКИ | 1993 |

|

RU2114496C1 |

| Автоматическое устройство для поэлементногоКОНТРОля АККуМуляТОРНОй бАТАРЕи | 1980 |

|

SU853717A1 |

| ИНДИКАТОР ЭЛЕКТРОМАГНИТНОГО ИЗЛУЧЕНИЯ | 1992 |

|

RU2060508C1 |

| ИСТОЧНИК ВТОРИЧНОГО ЭЛЕКТРОПИТАНИЯ | 1995 |

|

RU2074492C1 |

Изобретение .относится к импульсной технике.

Известен частотно-фазовый дискриминатор, содержащий фазовый триггер, два блокирующих т риггера, элемент И, четыре формирующих триггера, генерЗ тор единичного сигнала, генератор нулевого сигнала 1.

. Недостатком данного устройств.а является его сложность.

Наиболее близким к предлагаемому по технической сущности является частотно-фазовый детектор, содержащий цифровой частотно-фазовый различитель, токовый ключ и интегратор, выполненный на базе составного транзистора, где токовый ключ состоит из трехкаскадного инвертора, регулирующего транзистора, эмиттер которого соединен через диод с общим проводом, а коллектор - с выходом предоконечного каскада инвертора, выход оконёчногб каскада которого подключен к базе ключевосо транзистора и через резистивный делитель - к базе регулируницего, транзистора 2.

Однако этот дет.ектор характеризуется недостаточной точностью.

Целью-изобретения является повышение точности.

Поставленная цель достигается тем, чуо в частотно-фазовый детектор, содержащий цифровой частотно-фазовый различителЬ, входы которого соединены с входными шинами, а один выход подключен к входу токового ключа, состоящего и.з трехкаскадного инвертора, регулирующего транзисторного каскада и ключевого транзистора, эмиттер которого соединен с входом инт§гратоЕ а на составном транзисторе . и через первый диод с вторым выходом цифрового частотно-фазового различителя, причем коллектор транзистора

15 регулирующего каскада соединен с. коллектором транзистора второго каскада и с базрй транзистора третьего каскада трехкаскадного инвертора, эмиттер транзистора второго каскада

20 которого соединен с эмиттером транзистора регулирующего транзистора и через второй диод с общей шиной, введен дополните.пьный диод, включенный между эмиттером транзистора

25 третьего каскада трехкаскадного инвертора и базой транзистора регулирукицего каскада, причем база ключевого транзистора соединена с коллектором транзистора регулирующего

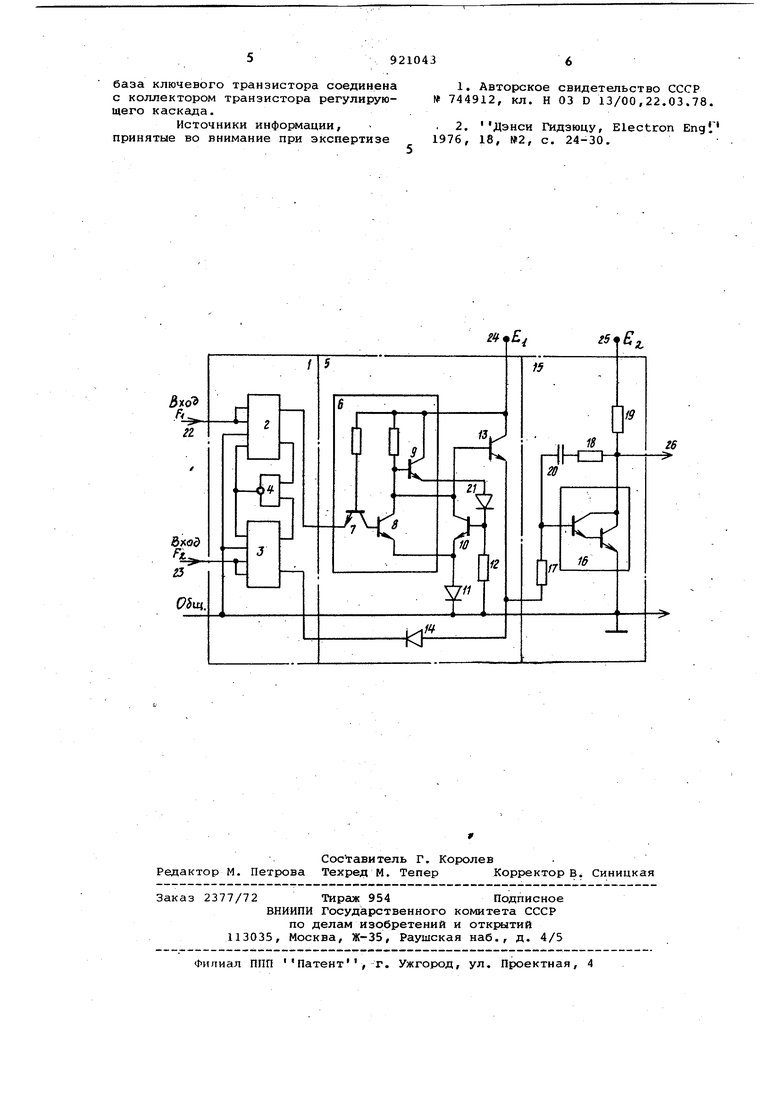

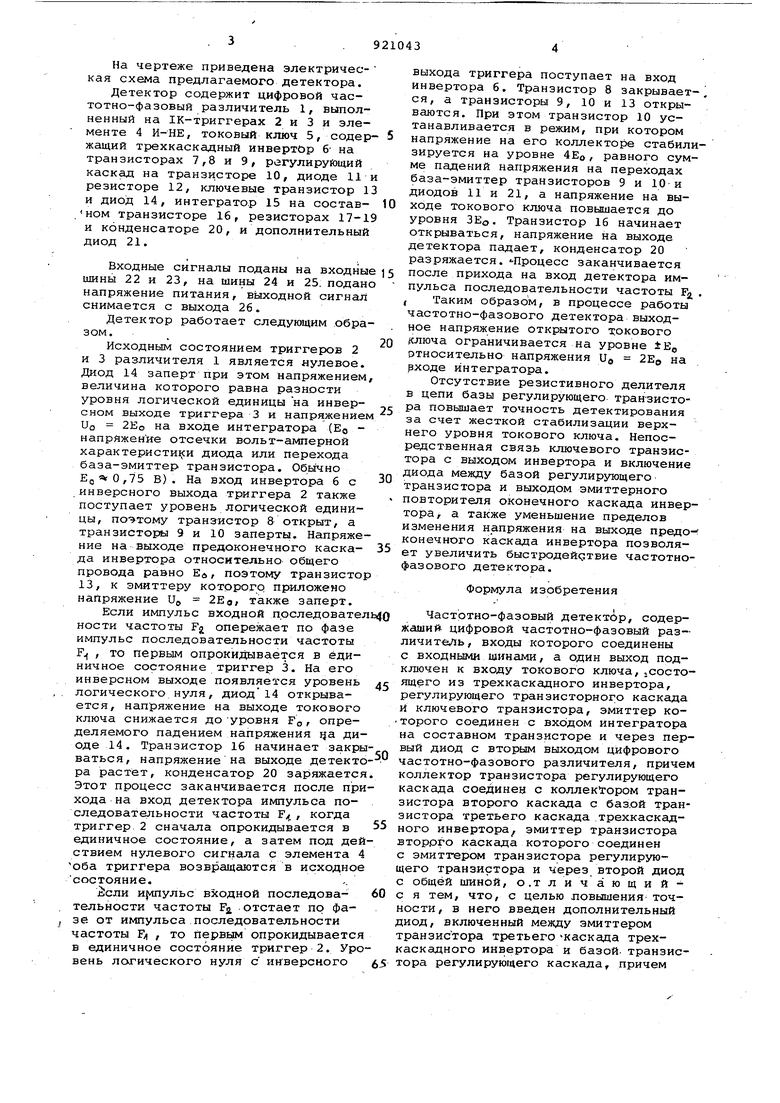

30 каскада. На чертеже приведена электрическая схема предлагаемого детектора. Детектор содержит цифровой частотно-фазовый различитель 1, выполненный на 1К-триггерах 2 и 3 и элементе 4 И-НЕ, токовый ключ 5, содер жащий трехкаскадный инвертор 6 на транзисторах 7,8 и 9, регулирующий каскад на транзисторе 10, диоде 11 резисторе 12, ключевые транзистор 1 и диод 14, интегратор 15 на составном транзисторе 16, резисторах 17-1 и конденсаторе 20, и дополнительный диод 21. Входные сигналы поданы на входны шины 22 и 23, на шины 24 и 25. подан напряжение питания, выходной сигнал снимается с выхода 26. Детектор работает следующим обра зом. Исходным состоянием триггеров 2 и 3 различителя 1 является нулевое. Диод 14 заперт при этом напряжением величина которого равна разности уровня логической единицы на инверсном выходе триггера 3 и напряжение UQ 2Ео на вхоДе интегратора (Ео напряжение отсечки вольт-амперной характеристи1 :и диода или перехода база-эмиттер транзистора. Обычно Eg «X 0,75 В). На вход инвертора 6с инверсного выхода триггера 2 также поступает уровень логической единицы, поэтому транзистор 8 открыт, а транзистоЕал 9 и 10 заперты. Напряже ние на выходе предоконечного каскада инвертора относительно общего провода равно ЕЙ, поэтому транзисто 13, к эмиттеру которого приложено напряжение Uj, 2Ео/ также заперт. Если импульс входной последовател ности частоты Fg опережает по фазе импульс последовательности частоты F , то первым опрокидывается в единичное состояние триггер 3. На его инверсном выходе появляется уровень . логического нуля, диод14 открывается, напряжение на выходе токового ключа снижается доуровня Fg, определяемого падением напряжения ца ди оде 14. Транзистор 16 начинает закры ваться, напряжение на выходе детекто ра растет, конденсатор 20 заряжаетс Этот процесс заканчивается после при хода на вход детектора импульСа последовательности частоты F. , когда триггер 2 сначала опрокидывается в единичное состояние, а затем под дей ствием нулевого сигнала с элемента 4 оба триггера возвращаются в исходное состояние. йсли и{лпульс входной последовательности частоты F отстает по фа, 36 от импульса последовательности частоты F/t , то первым опрокидывается в единичное состояние триггер 2. Уро вень логического нуля с инверсного выхода триггера поступает на вход инвертора 6. Транзистор 8 закрывает-, ся, а транзисторы 9, 10 и 13 открываются. При этом транзистор 10 устанавливается в режим, при котором напряжение на его коллекторе стабилизируется на уровне 4Ео, равного сумме падений напряжения на переходах база-эмиттер транзисторов 9 и 10 и диодов 11 и 21, а напряжение на выходе токового ключа повышается до уровня ЗЕо. Транзистор 16 начинает открываться, напряжение на выходе детектора падает, конденсатор 20 разряжается. -Процесс заканчивается после прихода на вход детектора импульса последовательности частоты F . , Таким образом, в процессе работы частотно-фазового детектора выходное напряжение открытого токового ключа ограничивается на уровне ±Ед относительно напряжения и 2Ео на рходе интегратора. Отсутствие резистивного делителя в цепи базы регулирующего транзистора повышает точность детектирования за счет жесткой стабилизации верхнего уровня токового ключа. Непосредственная связь ключевого транзистора с выходом инвертора и включение диода между базой регулирующего транзистора и выходом эмиттерного повторителя оконечного каскада инвертора/ а так:же уменьшение пределов изменения напряжения на выходе предо- конечного каскада инвертора позволяет увеличить быстродействие частотнофазового детектора. Формула изобретения Частотно-фазовый детектор, содерЖаши цифровой частотно-фазовый раз- личитель, входы которого соединены с входными шинами, а один выход подключен к входу токового ключа, .состоящего из трехкаскадного инвертора, регулирующего транзисторного каскада И ключевого транзистора, эмиттер которого соединен с входом интегратора на составном транзисторе и через первый диод с вторым выходом цифрового частотно-фазового различителя, причем коллектор транзистора регулирующего каскада соединен с коллектором транзистора второго каскада с баз.ой транзистора третьего каскада трехкаскадного инвертора, эмиттер транзистора вторрго каскада которого соединен с эмиттером транзистора регулирующего транзистора и через второй диод с общей шиной, о.тличающийс я тем, что, с целью ловышениЯ точности , в него введен дополнительный диод, включенный между эмиттером транзистора третьего каскада трехкаскадного инвертора и базой транзистора регулирующего каскада, причем

база ключевого транзистора соединена с коллектором транзистора регулирующего каскада.

Источники информации, принятые во внимание при экспертизе

. 2. Дэнси Гидзюцу, Electron ЕпдГ 1976, 18, 2, с. 24-30.

Авторы

Даты

1982-04-15—Публикация

1980-07-23—Подача