(54) УСТРОЙСТВО СИНХРОНИЗАЦИИ ШУМОПОДОБНЫХ

СИГНАЛОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство синхронизации шумоподобных сигналов | 1977 |

|

SU634472A2 |

| Устройство синхронизации шумоподобных сигналов | 1977 |

|

SU634473A2 |

| Устройство синхронизации шумоподобных сигналов | 1979 |

|

SU879802A2 |

| Устройство синхронизации шумоподобных сигналов | 1977 |

|

SU647878A2 |

| Устройство для синхронизации шумоподобных сигналов | 1976 |

|

SU613512A1 |

| Устройство для синхронизации шумоподобных сигналов | 1981 |

|

SU1003372A2 |

| Устройство для синхронизации шумоподобныхСигНАлОВ | 1979 |

|

SU809619A2 |

| Устройство для синхронизации шумоподобных сигналов | 1982 |

|

SU1022326A1 |

| Система связи с временным уплотнением шумоподобных сигналов | 1977 |

|

SU683029A1 |

| Устройство синхронизации шумоподобных сигналов | 1975 |

|

SU576669A1 |

1

Изобретение относится к радиотехнике и может быть использовано в системах связи с шумоподобными сигналами, требующих ускоренной синхронизации.

По основному авт. св. № 576669 известно устройство синхронизации шумоподобных сигналов, содержащее объединенные по первому входу перемножители, к вторым входам которых подключены выходы генератора несущей частоты, а выходы перемножителей через последовательно соединенные мoдyляtop сигналов и интеграторы подключены ко входам первого и второго сумматоров, выходы которых через квадраторы подключены ко входам третьего сумматора, выход которого через последовательно соединенные преобразователь и пороговый блок подключен ко входу блока управления, .выход которого подключен к одному.из входов модулятора сигналов и второму входу порогового блока 1.

Однако известное устройство обладает большим временем покска шумоподобных сигналов за счет того, что не обеспечивается оценка о состоянии канала связи.

Цель изобретения - сокращение времени поиска щумоподобных сигналов.

Цель достигается тем, что в устройство синхронизации щумоподобных сигналов, содержащее объединенные по первому входу перемножители, к вторым входам которых подключены выходы генератора несущей частоты, а выходы перемножителей через последовательно соединенные модулятор сигналов и интеграторы подключены ко вхо10дам первого и второго сумматоров, выходы которых через квадраторы подключены ко входам третьего сумматора, выход которого через последовательно соединенные преобразователь и пороговый блок подключен ко

15 входу блока управления, выход которого подключен к одному из входов модулятора сигналов и второму входу порогового блока, введены последовательно соединенные ключевой элемент, преобразователь аналог-код, регистр сдвига, блок сложения, элемент

20 памяти, делитель и дещифратор, при этом выходы третьего сумматора и порогового блока подключены ко входам ключевого элемента, а к второму и третьему входам блока сложения подключены соответственно

второй выход элемента памяти и выход преобразователя аналог-код.

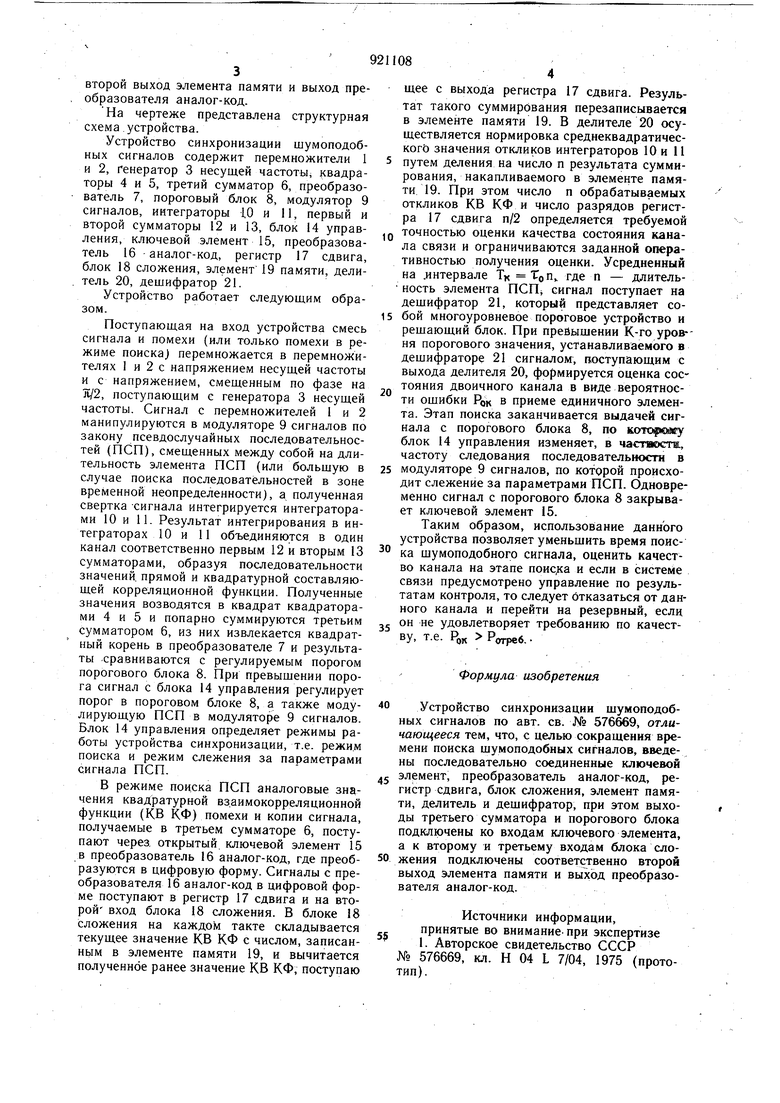

На чертеже представлена структурная схема устройства.

Устройство синхронизации шумоподобных сигналов содержит перемножители 1 и 2, Генератор 3 несущей частоты, квадраторы 4 и 5, третий сумматор 6, преобразователь 7, пороговый блок 8, модулятор 9 сигналов, интеграторы Ш и 11, первый и второй сумматоры 12 и 13, блок 14 управления, ключевой элемент 15, преобразователь 16 -аналог-код, регистр 17 сдвига, блок 18 сложения, элемент 19 памяти, делитель 20, дешифратор 21.

Устройство работает следующим образом.

Поступающая на вход устройства смесь сигнала и помехи (или только помехи в режиме поиска перемножается в перемножителях 1 и 2 с напряжением несущей частоты и с напряжением, смещенным по фазе на JI/2, поступающим с генератора 3 несущей частоты. Сигнал с перемножителей 1 и 2 манипулируются в модуляторе 9 сигналов по закону псевдослучайных последовательностей (ПСП), смещенных между собой на длительность элемента ПСП (или больщую в случае поиска последовательностей в зоне временной неопределенности), а полученная свертка -сигнала интегрируется интеграторами 10 и 11. Результат интегрирования в интеграторах 10 и 11 объединяются в один канал соответственно первым 12 и вторым 13 сумматорами, образуя последовательности значений, прямой и квадратурной составляющей корреляционной функции. Полученные значения возводятся в квадрат квадраторами 4 и 5 и попарно суммируются третьим сумматором 6, из них извлекается квадратный корень в преобразователе 7 и результаты сравниваются с регулируемым порогом порогового блока 8. При превыщении порога сигнал с блока 14 управления регулирует порог в пороговом блоке 8, а также модулирующую ПСП в модуляторе 9 сигналов. Блок 14 управления определяет режимы работы устройства синхронизации, т.е. режим поиска и режим слежения за параметрами сигнала ПСП.

В режиме поиска ПСП аналоговые значения квадратурной взаимокорреляционной функции (KB К.Ф) помехи и копии сигнала, получаемые в третьем сумматоре 6, поступают через, открытый ключевой элемент 15 в преобразователь 16 аналог-код, где преобразуются в цифровую форму. Сигналы с преобразователя 16 аналог-код в цифровой форме поступают в регистр 17 сдвига и на второй вход блока 18 сложения. В блоке 18 сложения на каждом такте складывается текущее значение KB КФ с числом, записаниьш в элементе памяти 19, и вычитается полученное ранее значение KB КФ, поступаю

щее с выхода регистра 17 сдвига. Результат такого суммирования перезаписывается в элементе памяти 19. В делителе 20 осуществляется нормировка среднеквадратическогЬ значения откликов интеграторов 10 и 11 путем деления на число п результата суммирования, накапливаемого в элементе памяти 19. При этом число п обрабатываемых откликов KB КФ и число разрядов регистра 17 сдвига п/2 определяется требуемой точностью оценки качества состояния канала связи и ограничиваются заданной оперативностью получения оценки. Усредненный на .интервале Тк ТоП где п - длительность элемента ПСП сигнал поступает на дещифратор 21, который представляет собой многоуровневое пороговое устройство и рещающий блок. При превышении К-го уров-ня порогового значения, устанавливаемого в дешифраторе 21 сигналом, поступающим с выхода делителя 20, формируется оценка состояния двоичного канала в виде вероятности ощибки РОК в приеме единичного элемента. Этап поиска заканчивается выдачей сигнала с порогового блока 8, по KorofWiMy блок 14 управления изменяет, в частмости., частоту следования последовательности в

5 модуляторе 9 сигналов, по которой происходит слежение за параметрами ПСП. Одновременно сигнал с порогового блока 8 закрывает ключевой элемент 15.

Таким образом, использование данного устройства позволяет уменьшить время поис° ка шумоподобного сигнала, оценить качество канала на этапе покера к если в системе связи предусмотрено управление по результатам контроля, то следует отказаться от данного канала и перейти на резервный, если он не удовлетворяет требованию по качеству, т.е. РОК Ротре6.Формула изобретения

0 Устройство синхронизации щумоподобных сигналов по авт. св. № 576669, отличающееся тем, что, с целью сокращения времени поиска шумоподобных сигналов, введены последовательно соединенные ключевой

5 элемент, преобразователь аналог-код, регистр сдвига, блок сложения, элемент памяти, делитель и дешифратор, при этом выходы третьего сумматора и порогового блока подключены ко входам ключевого элемента, а к второму и третьему входам блока сложения подключены соответственно второй выход элемента памяти и выход преобразователя аналог-код.

Источники информацин, принятые во внимание- при экспертизе 1. Авторское свидетельство СССР № 576669, кл. Н 04 L 7/04, 1975 (прототип).

jz :зц

fS - f5

Е

2Д

Т

7

1/ 8

1/. /

f5 J

/

2/

Авторы

Даты

1982-04-15—Публикация

1980-05-05—Подача