(5) СИНХРОННЫЙ ДЕМОДУЛЯТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Демодулятор | 1978 |

|

SU744962A1 |

| Синхронный демодулятор | 1977 |

|

SU656164A1 |

| Тензометрическое устройство | 1986 |

|

SU1396716A1 |

| Дискретный заградительный фильтр | 1983 |

|

SU1145461A1 |

| Способ уменьшения помех в измерительных устройствах уравновешивания и устройство для его осуществления | 1977 |

|

SU682830A1 |

| УСТРОЙСТВО ПРЕОБРАЗОВАНИЯ СИГНАЛОВ МИКРОМЕХАНИЧЕСКОГО ГИРОСКОПА ВИБРАЦИОННОГО ТИПА | 2005 |

|

RU2282152C1 |

| Устройство для передачи сигналов | 1982 |

|

SU1067608A1 |

| СИСТЕМА СВЯЗИ | 1992 |

|

RU2049372C1 |

| Устройство для дифференцированияэлЕКТРичЕСКиХ СигНАлОВ | 1979 |

|

SU851419A1 |

| Устройство приема сигналов с амплитудно-фазовой манипуляцией | 1985 |

|

SU1356247A1 |

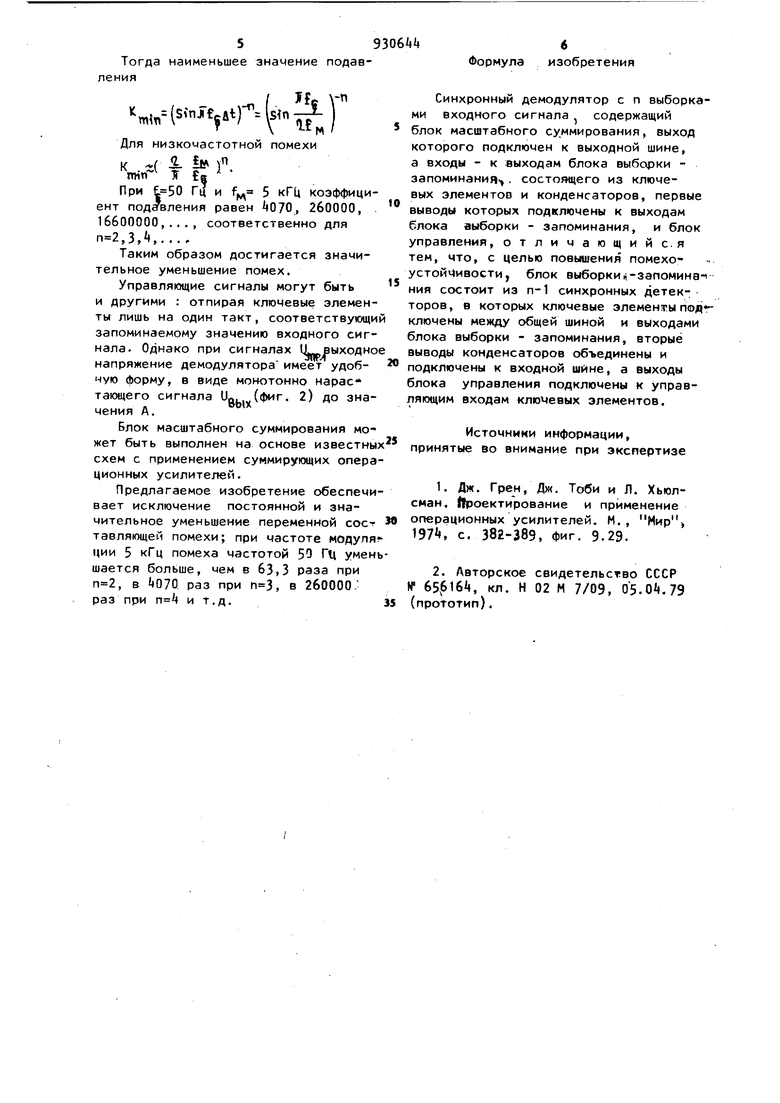

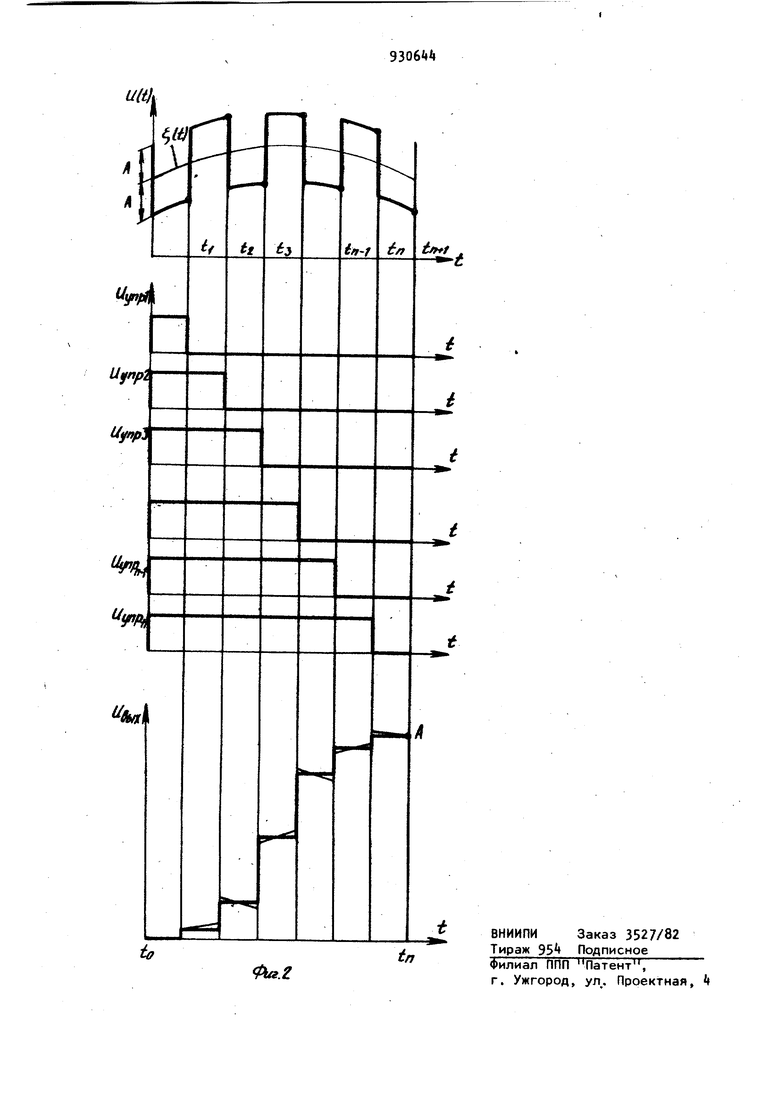

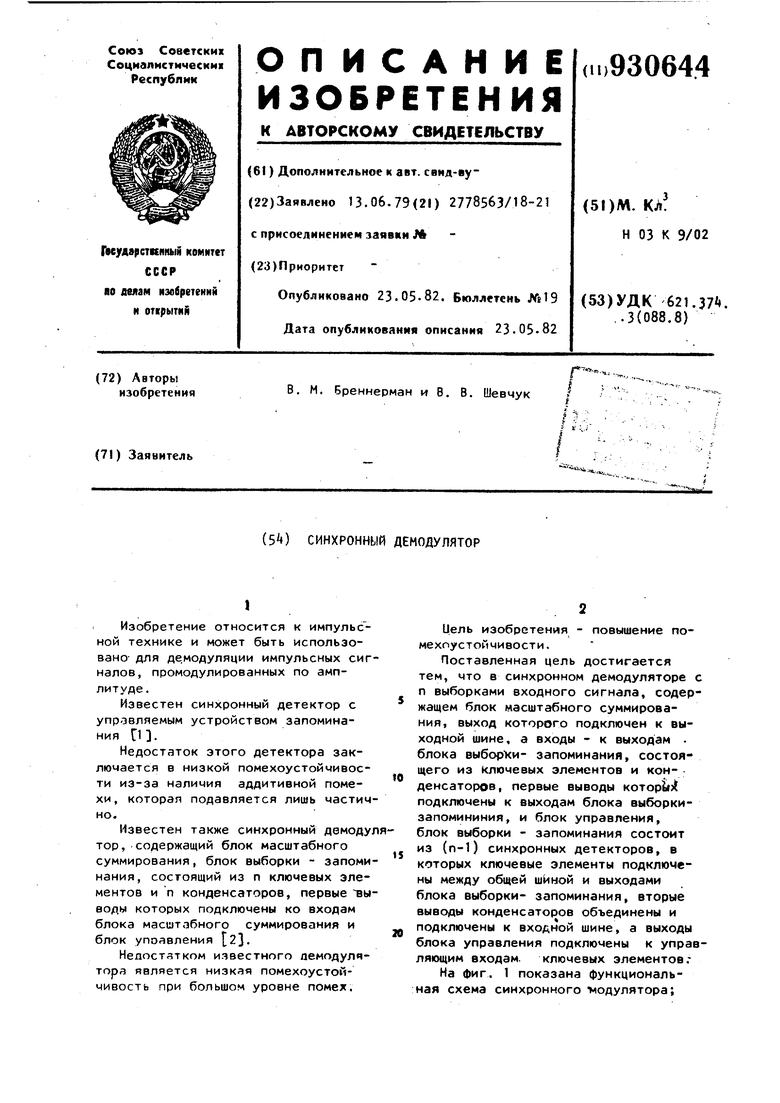

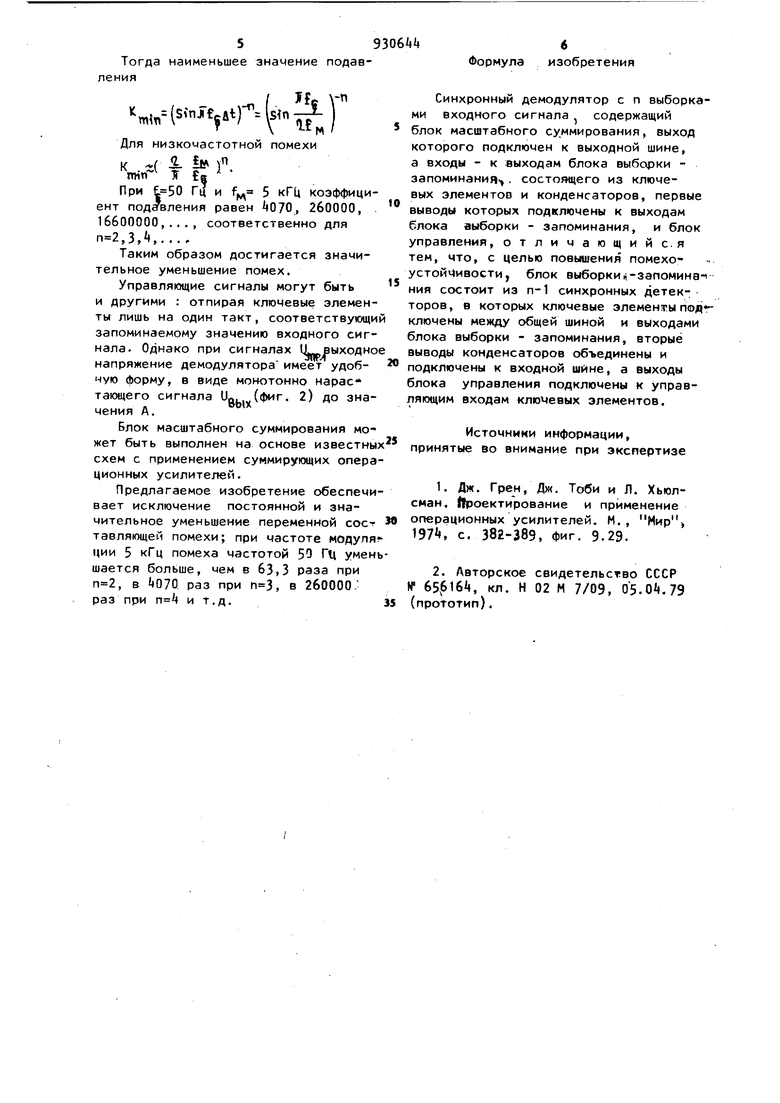

Изобретение относится к импульсной технике и может быть использовано для де.модуляции импульсных сиг налов, промодулированных по амплитуде. Известен синхронный детектор с упрЭвляемым устройством запоминания П. Недостаток этого детектора заключается в низкой помехоустойчивости из-за наличия аддитивной помехи, которая подавляется лишь частич но. Известен также синхронный демоду тор, содержащий блок масштабного суммирования, блок выборки - запоми нания, состоящий из п ключевых элементов и п конденсаторов, первые вы 80ДЫ которых подключены ко входам блока масштабного суммирования и блок упоавления 2. Недостатком известного демодулятора является низкая помехоустойчивость при большом уровне помех. Цель изобретения - повышение помехоустойчивости. Поставленная цель достигается тем, что в синхронном демодуляторе с п выборками входного сигнала, содержащем блок масштабного суммирования, выход которого подключен к выходной шине, а входы - к выходам блока выборки- запоминания, состоящего из Ключевых элементов и конденсаторов, первые выводы которЫ подключены к выходам блока выборкизапомининия, и блок управления, блок выборки - запоминания состоит из (п-1) синхронных детекторов, в которых ключевые элементы подключены между общей шиной и выходами блока выборки- запоминания, вторые выводы конденсаторов объединены и подключены к входной шине, а выходы блока управления подключены к управляющим входам. ключевых элементов .На фиг. 1 показана функциональная схема синхронного одулятора; 393 на фиг. 2 - диаграммы входного, выходного и управляющих сигналов. Синхронный демодулятор с. п выборками входного сигнала содержит блок 1 выборки - запоминания , блок 2 масш табного суммирования и блок 3 управления. Блок 1 выборки - запоминания выполнен в виде (п-1) синхронных детекторов, каждый из которых состоит из конденсатора k и ключевого элемента 5. Первые выводы конденсаторов подключены к соответствующим входам блока 2 масштабного суммирования , а вторые выводы объединены и подключены к входной-шине. Ключевые элементы 5 включены между первыми вы водами конденсаторов 4 и общей шиной, а управлякздие входы ключевых эле ментов соединены с соответствующими выходами блока 3 управления, Синхронный демодулятор работает следующим образом. На вход синхронного демодулятора поступают сигналы знакочередукхцихся прямоугольных импульсов с аддаптианой помехой (на фиг. 2) U(t -(-if-A +f (t.) ,. где i - номера положительных и отри- цательтйх импульсов; А - полезный сигнал; |(О - значения помехи, соответствующие моментам t; . t. - моменты выборок сигнала в синхронных детекторах 1. Если синхронный демодулятор содержит п синхронных детекторов, то для получения одного значения полезного сигнала используется последовательность из (п+1) импульсов. Положительная полярность управляющих сигналов .,(Фиг. 2) соответствует открытому состоянию ключевых элементов 5- Когда ключевой элемент 5 открыт, конденсатор k включен между общей шиной и входом устройства и происходит заряд конденсатора йо величины входного сигнала. По отрицательным фронтам управляющих сигналов происходит запоминание на конденсаторах , соответствующих это му моменту времени значений входного сигнала. Входное сопротивление блока 2 масштабного суммирования должно быть достаточно велико, чтобы исключить погрешности разряда конденсаторов 4. На конденсаторе i-ro синхронного детектора оказывается запомненым значение U(t), причем на вход лока 2 масштабного суммирования осле размыкания ключевого элейена 5 оно включается с обратным знаом. В момент времени t на внходах инхронных детекторов появляется напяжение величиной U(t )- U(t,-), Выходные сигналы синхронных детекоров суммируются а блоке 2 масштабого суммирования, с весовыми коэфициентамиПоэтому в момент времени t .на ыходе устройства имеем .Н(пи)-(4 1 SHr-; UiV-Uit,,) С(,).§(,4 .И) 141 1 1 4--1 и-„. п-и -С +-( . с;: -нГАснг- -(,)а1-1) i-« Г 1 «-п аЧ- - иГ-4--о-, |V)c|;f{i),,...,tnH)i де - конечная разность п-го поядка. Следовательно ц,,- А .,illcr.-W.. оэффициент подавления помехи 1/ jm оП .. fUl f SinllE П+1 . . К.)., г iSfcAt-JI l tsinnf ulf-sin|a5 t+n- -j Наибольшая величина .n)1.fm5i-nJT 6ui Тогда наименьшее значение подавления I V K(s((sin-;j-) Для низкочастотной помехи К -v( S. Ifi ) min Л if При 50 Гц и f 5 кГц коэффициент подавления равен 070, 260000, 16600000,..., соответственно для ,3, Таким образом достигается значительное уменьшение помех. Управляющие сигналы могут быть и другими : отпирая ключевые элементы лишь на один такт, соответствующи запоминаемому значению входного сигнала. Однако при сигналах 11ьрВыходно напряжение демодулятора имеет удобную форму, в виде монотонно нарас тающего сигнала Un, (фиг. 2) до значения А. Блок масштабного суммирования может быть выполнен на основе известны схем с применением суммирующих опера ционных усилителей. Предлагаемое изобретение обеспечи вает исключение постоянной и значительное уменьшение переменной сосг тавляющей помехи; при частоте мoяyпя НИИ 5 кГц помеха частотой 50 Гц умен шается больше, чем в 63,3 раза при , в 4070. раз при , в 260000.раз при п и т.д. Формула изобретения Синхронный демодулятор с п выборками входного сигнала содержащий блок масштабного суммирования, выход которого подключен к выходной шине, а входы - к выходам блока выборки запоминания. состоящего из ключевых элементов и конденсаторов, первые выводы которых подключены к выходам блока выборки - запоминания, и блок управления, отличающийс.я тем, что, с целью повышения помехо устойчивости, блок выборкип-запоминав ния состоит из п-1 синхронных детекторов, в которых ключевые элементы подг ключены между общей шиной и выходами блока выборки - запоминания, вторые выводы конденсаторов об1 единены и подключены к входной шине, а выходы блока управления подключены к управляющим входам ключевых элементов. Источники информации, принятые во внимание при экспертизе 1.Дж. Грен, Дж. Тоби и Л. Хьюлснан, 1 роектирование и применение операционных усилителей. М., Мир 197, с. 382-389, фиг. 9.29. 2.Авторское свидетельство СССР N- 65,6l6it, кл. Н 02 М 7/09, 05.0«,79 (прототип).

t

flftf

бход

I

Btffnoff

Фиг.1

Авторы

Даты

1982-05-23—Публикация

1979-06-13—Подача