(54) ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство синхронизациии и нормирования импульсных последовательностей | 1981 |

|

SU957423A2 |

| Пересчетное устройство | 1984 |

|

SU1226655A1 |

| Формирователь импульсов | 1979 |

|

SU855975A1 |

| Формирователь импульсов | 1978 |

|

SU725209A1 |

| Формирователь импульсов | 1982 |

|

SU1056442A1 |

| Устройство синхронизации и нормирования импульсных последовательностей | 1979 |

|

SU855981A1 |

| Генератор серий импульсов | 1977 |

|

SU714630A1 |

| Формирователь длительности им-пульСОВ | 1979 |

|

SU839038A1 |

| Логический анализатор | 1987 |

|

SU1476474A1 |

| Устройство для выделения первого и последнего импульсов в пачке | 1984 |

|

SU1167716A1 |

1

Формирсеатепь икшульсов относятся к импульсной технике, может быть использован в устройствах обработки информашт.

По основному авт. св. Mb 729832 известен формирователь импульсов, содержащий элемент совпадения, два триггера, линию задержки с отводом, кото рый подключен к единичному входу второго триггера, вход линии задержки соединен с единичным выходом первого триггера, единичный вход которого подсоединен к выходу элемента совпадения, пфвый вход которого нодютючея к входной шине, а второй вход - к нулевс лу вьтходу второго триггера, инвертор, вход ксяорого соединен с входной шиной, а выход нулевым входом второго триггера, при этом третий вход элемента совпадения соединен с нулевым выходом первого триггера, нулевой вход котсрого подалючен к выходу линии задерноси.

Недостатками этсго формирователя нмпупЬсов являются значительное время

восстановления, равное длительности формируемого на выходе импульса, при запуске формирователя входными иипульсами, длительность которых меньше nrotтельноста выходного импульра, и возможность пребывания второго Tforrepa в запрешеннотл состоянии, которое В1фажается в одновремшном налиязш запуокающих сигналов на единичном и нуяевом входах второго триггера и имеет место при запуске известного формяро вателя входными импульсами, дпитеяыность которых мовьше отрезка времеш между передним фронтом входного голпульса и задним фронтом импульса фо| мируемого на отводе линии задержки.

Цель изобретения - уменьшение времени восстановления формирователя импульсов.,

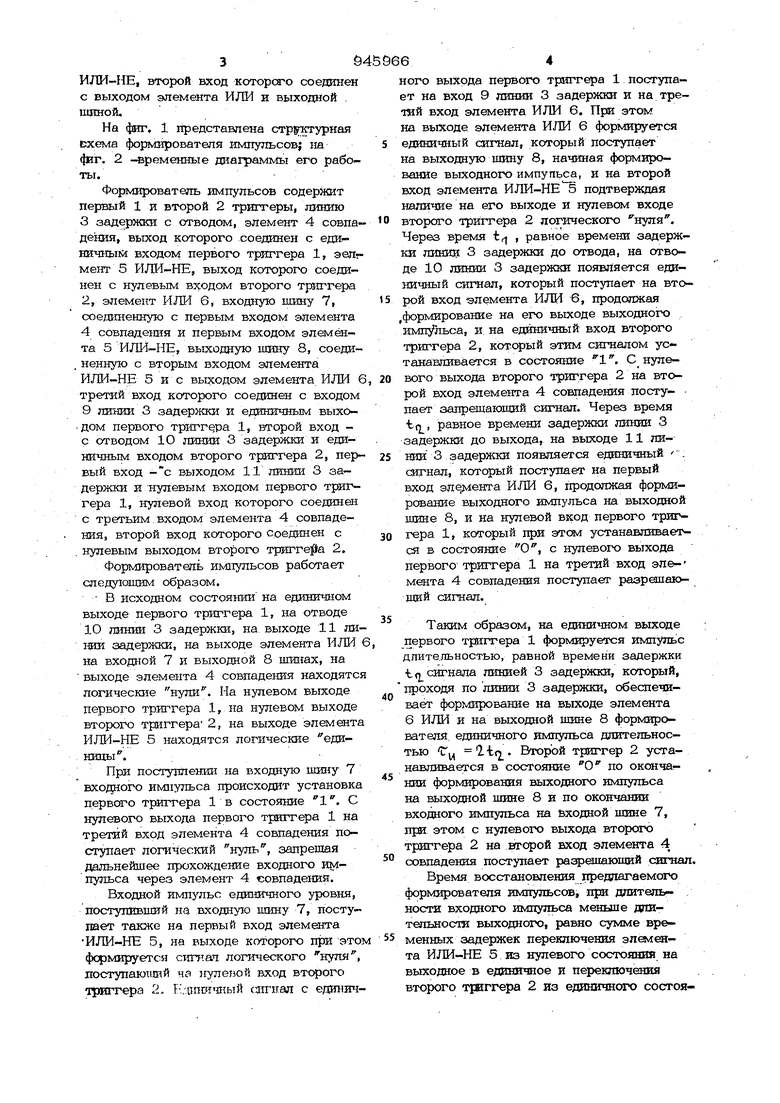

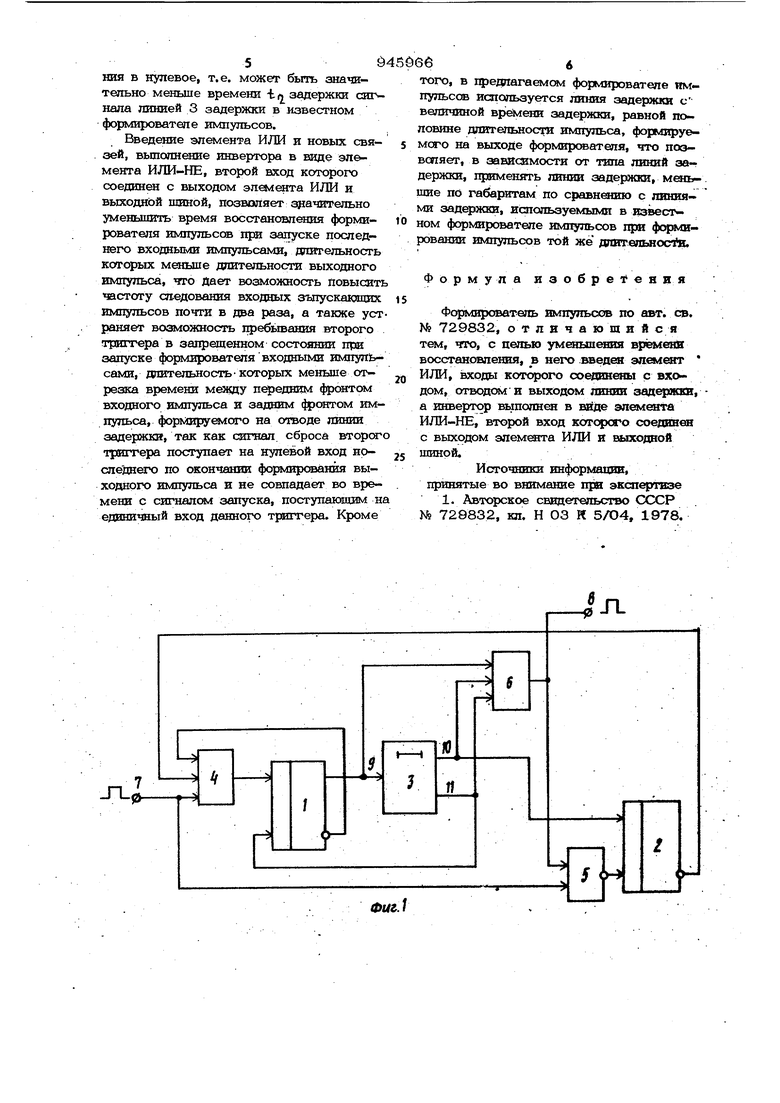

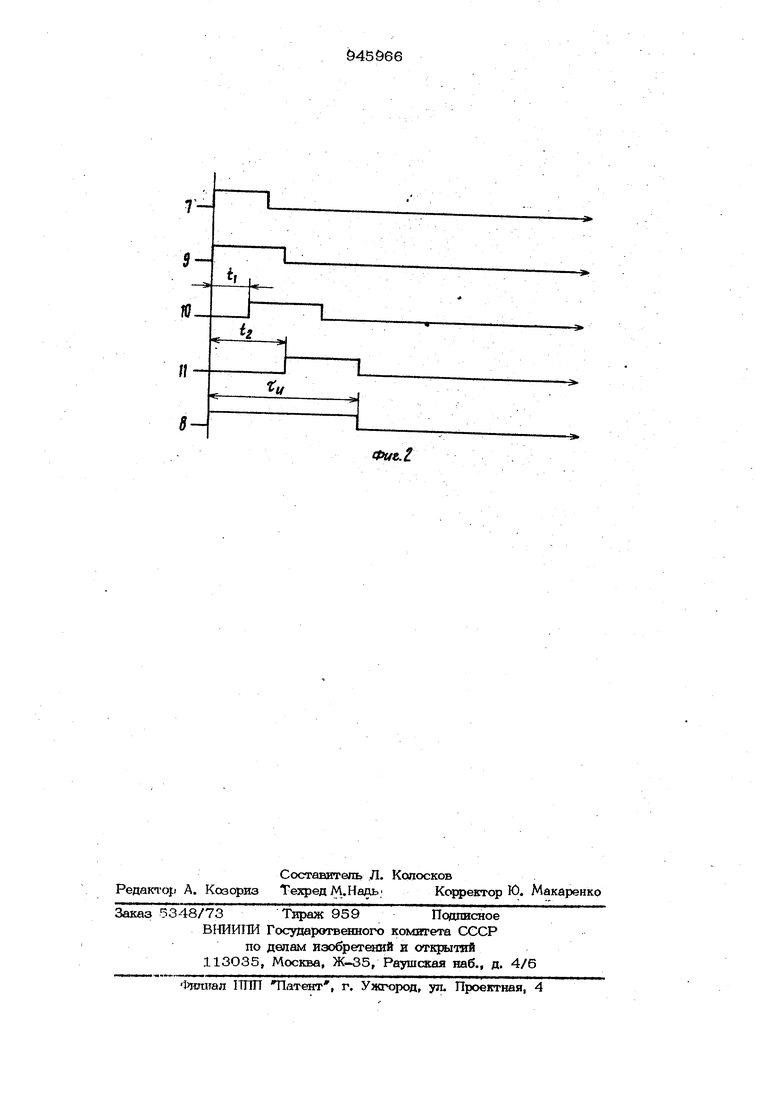

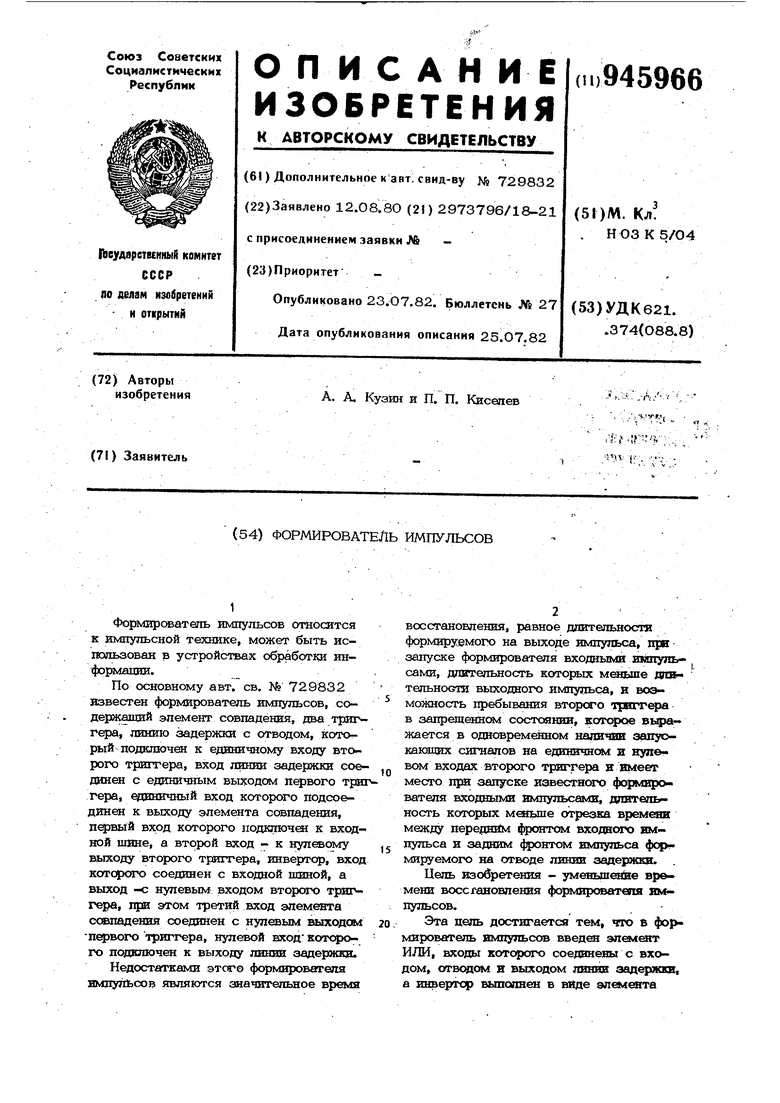

Эта цель достигается тем, что в формирователь импутшсов введен элемигт ИШ, входы которого соединены с входом, отводом н выходом линии задержки, а инвертор выполнен в виде элемента ИЛИ-НЕ, второй вход которого сюеданен с выходом элемента ИЛИ и выходной лшной, На фиг, 1 представлена структурная схема форм15рователя импульсов; на фиг. 2 -временные ш аграммы его работы. Формирователь импульсов содержит первый 1 и второй 2 триггеры, линию 3задержки с отводом, элемент 4 совпа де1ния, выход которого соединен с единичным входом первого триггера 1, эеп MeiiT 5 ИЛИ-НЕ, выход которого соединен с нулевым входом второго триггера 2, элемент ИЛИ б, входную шину 7, соещшенную с первым входом элемента 4совпадезшя и первым входом элемента 5 , выходную шину 8, соеди. ненную с вторым входом элемента ИЛИ-НЕ 5 и с выходом элемента ИЛИ третий вход которого соединен с входом 9линии 3 задержки и единичным выхо дом первого триггера 1, второй вход с отводом 10 линии 3 задержки и единичным входом второго триггера 2, пер вый вход выходом 11 лшпш 3 задержки и нулевым входом первого триггера 1, нулевой вход которого соединен с третьим входом элемента 4 совпадения, второй вход которого Соединен с . нулевым выходом второго триггера 2. Формирователь импульсов работает следующим образом. В исходном состоянии на единичком выходе первого триггера 1, на отводе 10линии 3 задержки, на выходе 11 ли нии задержки, на выходе элемента ИЛИ на входной 7 и выходной 8 шинах, на выходе элемента 4 совпаде1Шя находятс логические нули. На нулевом выходе первого триггера 1, на нулевом выходе второго Tpirrepa 2, на выходе элемента ИЛИ-НЕ 5 находятся логические единицы. При постутшении на входную шину 7 входного имиутхьса происходит установка первого триггера 1 в состояние 1. С нулевого выхода первого триггера 1 на третий вход элемента 4 совпадения поступает логический нуль, запрещая дальнейшее прохождение входного импульса через элемент 4 совпадения. Входной импульс единичного уровня, поступивший на входную шину 7, поступает также на первый вход элемента ИЛИ-НЕ 5, на выходе которого при это фсрмируется стстттач логического нутхя, лоступаюгций на нулевой вход второго триггера 2, 1-:.апгой1ый аггпал с едини ного выхода первого триггера 1 поступает на вход 9 пинки 3 задержки и на третий вход элемента ИЛИ 6. При этом на выходе элемента ИЛИ 6 формируется едашичный сигнал, который поступает на выходную шину 8, начиная формирование выходного импупьса, и на второй вход элемента ИЛИ-НЕ 5 подтверждая наличие на его выходе и нулевом входе второго триггера 2 логического нуля. Через время t , равное времени задержки ЛИНК0 3 задержки до отвода, на отводе 10 яинии 3 задержки появляется единичный сигаал, который поступает на второй вход элемента ИЛИ 6, хфодолжая .формирование на его выходе выходного импульса, и на единичный вход второго триггера 2, который этим сигналом устанавливается в состояние 1. С нулевого выхода второго триггера 2 на второй вход элемента 4 совпадения поступает запрещаюший сигнал. Через время to , равное времени задержки линии 3 задержки до выхода, на выходе 11 линии 3 задержки появляется единичный . сигнал, который поступает на первый вход эле;у1ента ИЛИ 6, продолжая формирование выходного импульса на выходной шине 8, и на нулевой вкод первого триггера 1, который при этслл устанавливает ся Б состояние О, с нулевого выхода первого триггера 1 на третий вход элемента 4 совпадения поступает разрешающий сигнал. Таким образом, на единичном выходе первого триггера 1 формируется импульс длительностью, равной времени задержки t( сигнала линией 3 задержки, который, проходя по линии 3 задержки, обеспечивает формирование на выходе элемента 6 ИЛИ и на выходной шине 8 формирователя, единичного импульса длительностью fy 1if. Второй триггер 2 устанавливается в состояние О по окончании формирования выходного импульса на выходной шине 8 и по окончании входного импульса на бходной швне 7, при этом с нулевого выхода второго триггера 2 на нггорой вход элемента 4 совпадения поступает разрешающий сигнал. Время восстановления предлагаемого формирователя имхгульсов, при длительности входного импульса меньше дпятельностас выходного, равно сумме временных задержек переключения элемента ИЛИ-НЕ 5 из нулевого СОСТОЯНИЯ на выходное в единичное и переключения второго триггера 2 из еданичного состоя5Йния в нулевое, т.е. может быть значительно меньше времени i rj задержки сигнала линией 3 задержки в известном формирователе имнульсов. . Введетше элемента ИЛИ и новых связей, вьшолнение инвертора в Еазде элемента ИЛИ-НЕ, второй вход которого соединен с выходом элемента ИЛИ и выходной шиной, позволяет значительно уменьшить время восстановления формирователя импульсов при запуске последнего входными импульсами, дгшгельность которых меньше длительности выходного импульса, что дает возможность повысить частоту следования входных зъпускакяцих импульсов почти в два раза, а также уст раняет возможность пребьшания второго триггера в запрещенном состоянии при запуске формирователя входными импульсами, длительность-которых меньше отрезка времени между п еднвм фронтом входного импульса и задним фронтом импульса, формиру0 ого на отводе линии задержки, так как сигнал сброса вторсяг триггера посггупает на нулевой вход нрсле его по окончании формирования выходного импульса и не совпадает во времени с сигналсм запуска, поступающим на единичный вход данного триггера. Кроме бе того, в гчредлагаемом формирователе nvtпульсов используется линия задержки с величиной задержки, равной половине длительное импульса, формируемсго на выходе фqpмиpoвaтeгtя, что пехзвепяет, в зависимости от типа линий задержки, применять линии задержки, меньшие по габаритам по сравнению с линиями задержки, используемыми в известном формирователе имг ульсов при фо1 шровании импульсов той же дпйтельнос я. Формула изобретен и Формирователь импулызов по авт. св. № 729832, отличающий с я тем, что, с пенью уменьш шя времени восстановления, в него .введен элемент ИЛИ, входы которого соединены с входом, отводами и выходом линии , а инвертор вьгаопнен в вЕще элемента ИЛИ-НЕ, второй вход которого соедЕнен с выходом элемента ИЛИ и выходной пшнрй. Источники информации, принятые во внимание при 1. Авторское свидетельство СССР № 728832, кл. Н ОЗ К 5/04, 1978.

7 q

да.

«г

П 5

tf

Фие.

Авторы

Даты

1982-07-23—Публикация

1980-08-12—Подача