(54) ТЕЛЕВИЗИОННЫЙ ИМИТАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Спектроанализатор | 1979 |

|

SU866494A1 |

| Устройство обнаружения и определения координат объекта на изображении | 1990 |

|

SU1737755A1 |

| Устройство интерполирования сигналов телевизионного изображения | 1989 |

|

SU1690213A1 |

| ТЕЛЕВИЗИОННАЯ СИСТЕМА ВЫСОКОГО РАЗРЕШЕНИЯ | 1996 |

|

RU2127961C1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1986 |

|

SU1381584A1 |

| Устройство для вывода информации на экран электронно-лучевой трубки | 1988 |

|

SU1578738A1 |

| Многоканальное устройство для регистрации | 1985 |

|

SU1322156A1 |

| Устройство выравнивания гистограмм яркостей телевизионного сигнала | 1989 |

|

SU1658176A1 |

| Устройство для вывода информации с экрана электронно-лучевой трубки | 1983 |

|

SU1265756A1 |

| Устройство для отображения графической информации | 1980 |

|

SU955186A1 |

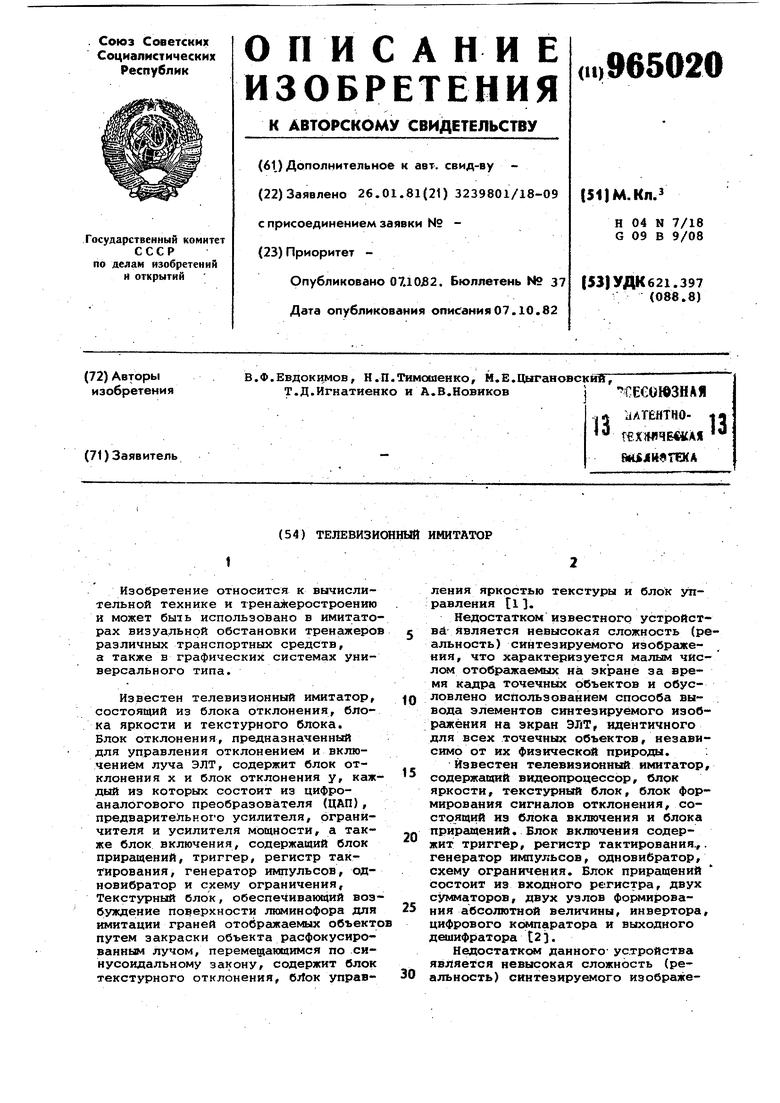

Изобретение относится к вычислительной технике и тренажеростроению и может быть использовано в имитаторах визуальной обстановки тренажеров различных транспортных средств, а также в графических системах универсального типа.

Известен телевизиоииый имитатор, состоящий из блока отклонения, блока яркости и текстурного блока. Блок отклонения, предназначенньй для управления отклонением и включением луча ЭЛТ, содержит блок отклонения X и блок отклонения у, каждый из которых состоит из цифроаналогового преобразователя (ЦАП), предварительного усилителя, ограничителя и усилителя мощности, а также блок включения, содержащий блок приращений, триггер, регистр такгирования, генератор импульсов, олновибратор и схему ограничения. Текстурный блок, обеспечивающий возбуждение поверхности люминофора для имитации граней отображаемых объектов путем закраскн объекта расфокусированным лучом, перемещающимся по синусоидальному закону, содержит блок текстурного отклонения, бЛок управления яркостью текстуры и блок Управления tl 3.

Недостатком известного устройстве, является невысокая сложность (реальность) синтезируемого изобргикения, что характеризуется малым числом отображаемых на экране за время кадра точечных объектов и обусловлено использованием способа вы10вода элементов синтезируемого изображения на экран ЭЛТ, идентичного для всех точечных объектов, независимо от их физической природы.

Известен телевизионный имитатор,

15 содержащий видеопроцессор, блок яркости, текстурный блок, блок формирования сигналов отклонения, состоящий из блока включения и блока приращений. Блок включения содер20жит триггер, регистр тактирования, генератор импульсов, одновибратор, схему ограничения. Блок приращений состоит из входного регистра, двух сумматоров, двух узлов формирова25ния абсолютной величины, инвертора, цифрового компаратора и выходного даиифратора t2.

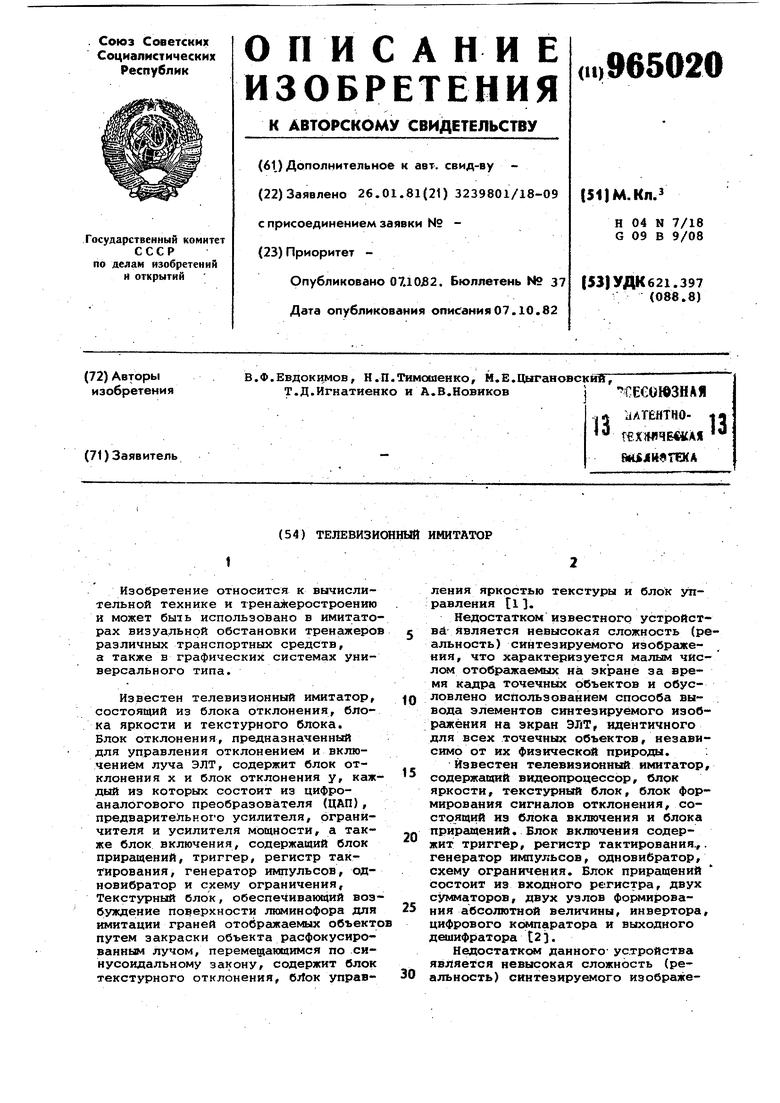

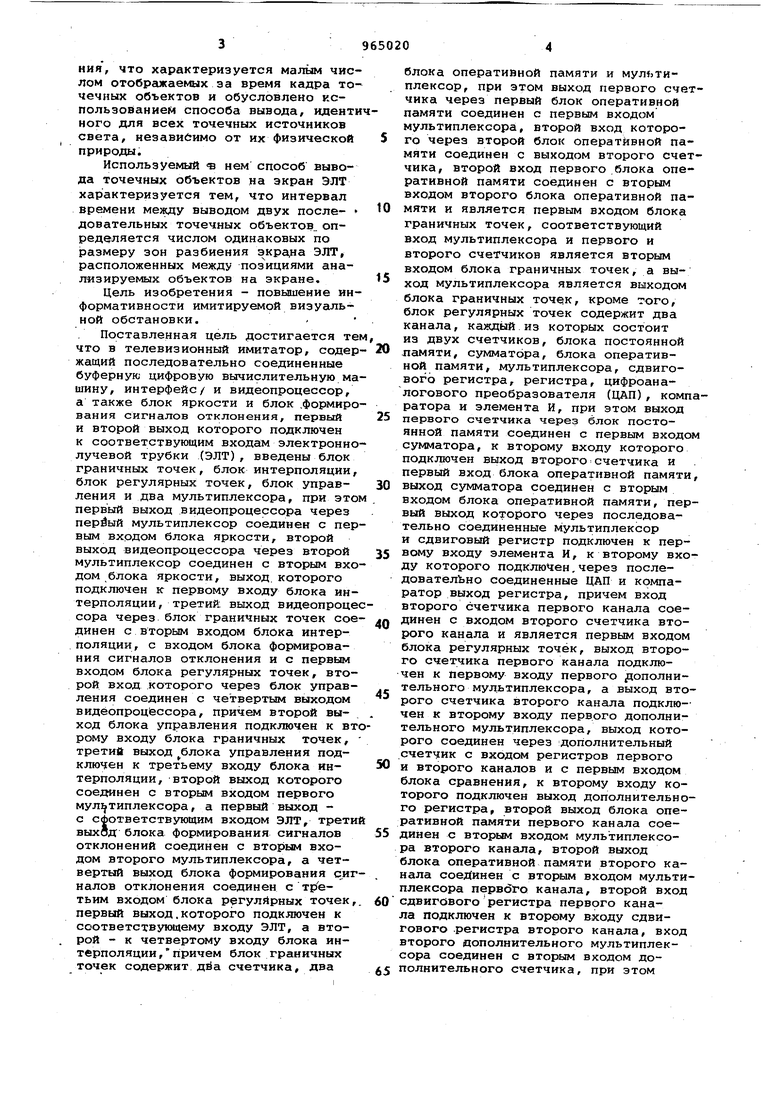

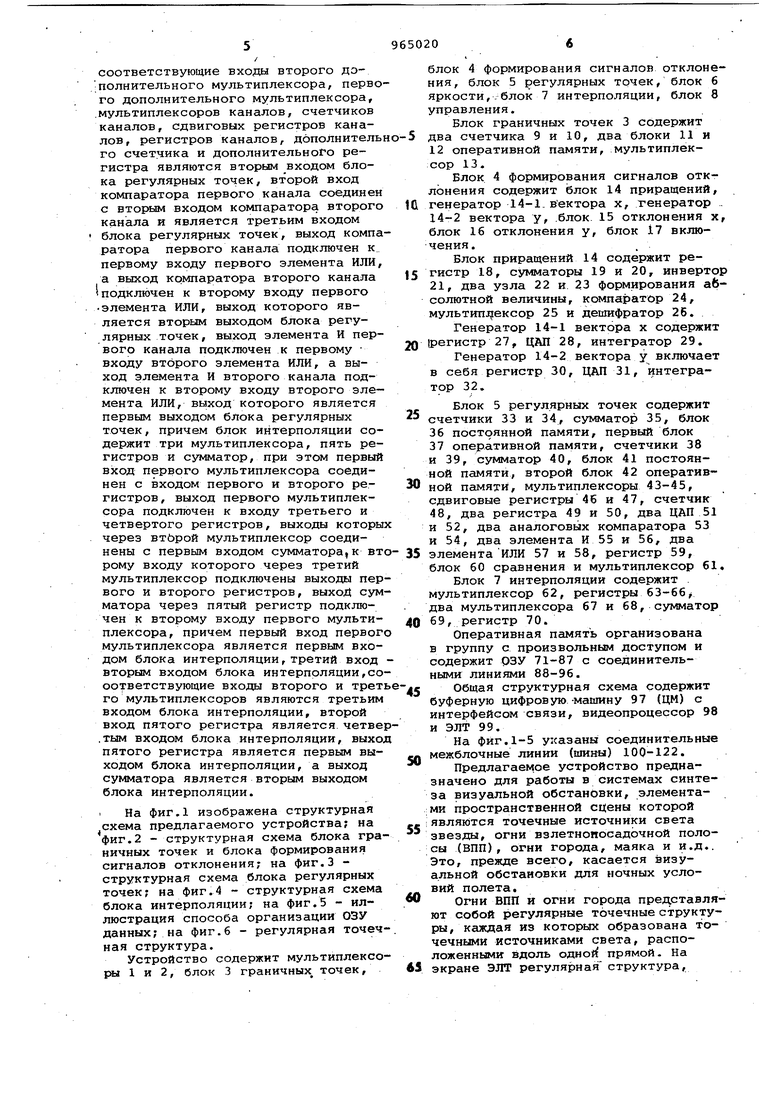

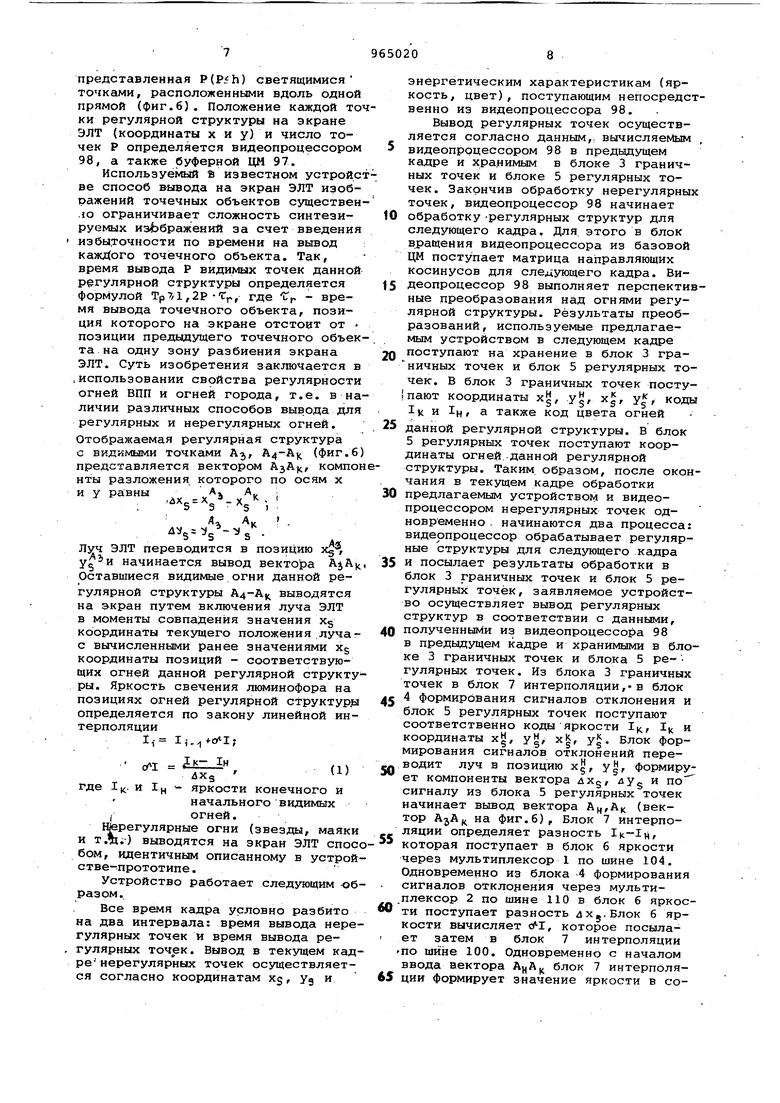

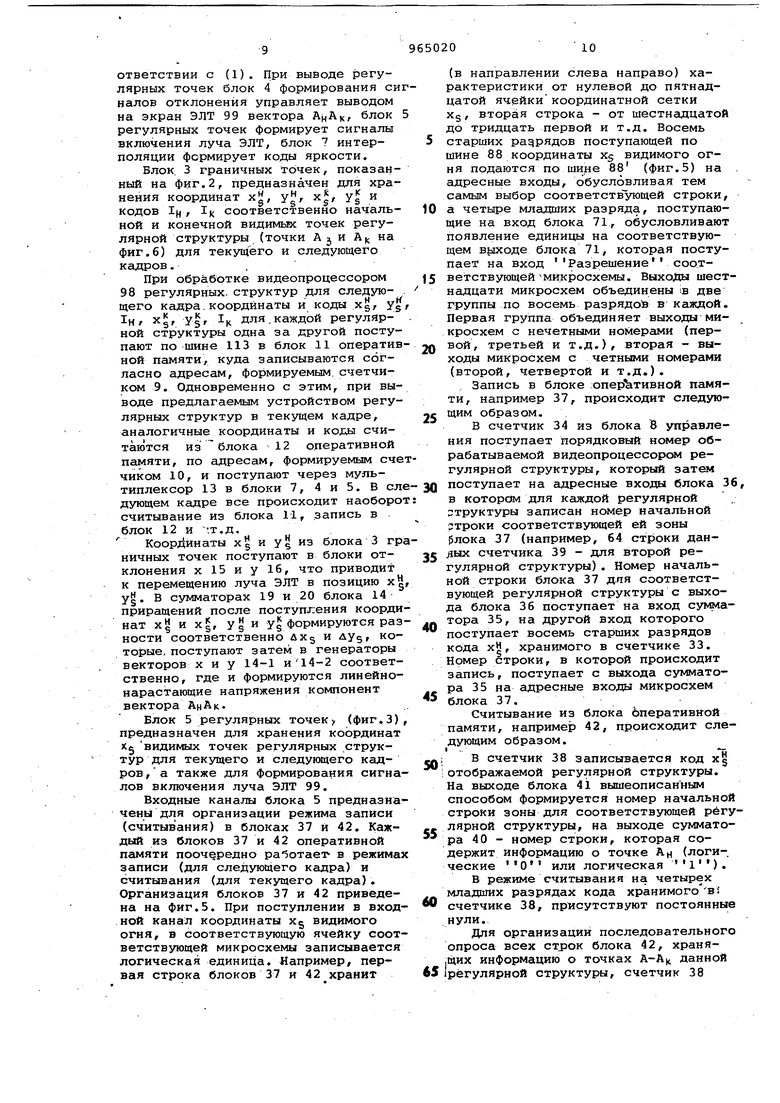

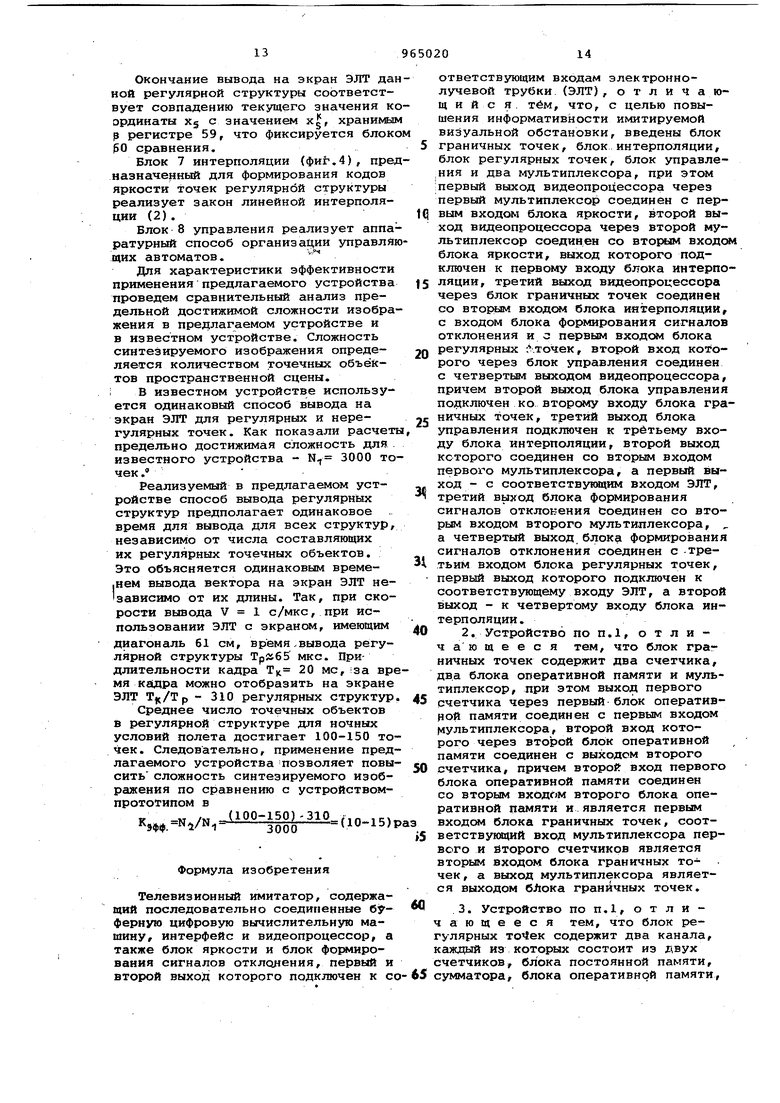

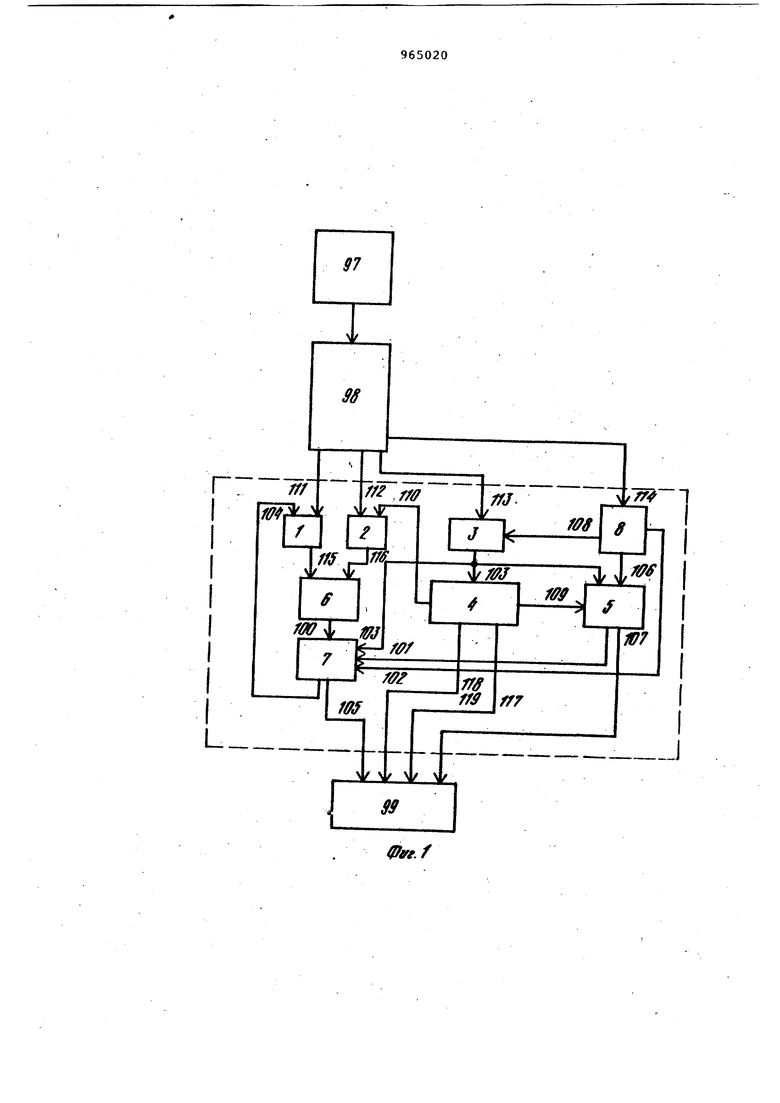

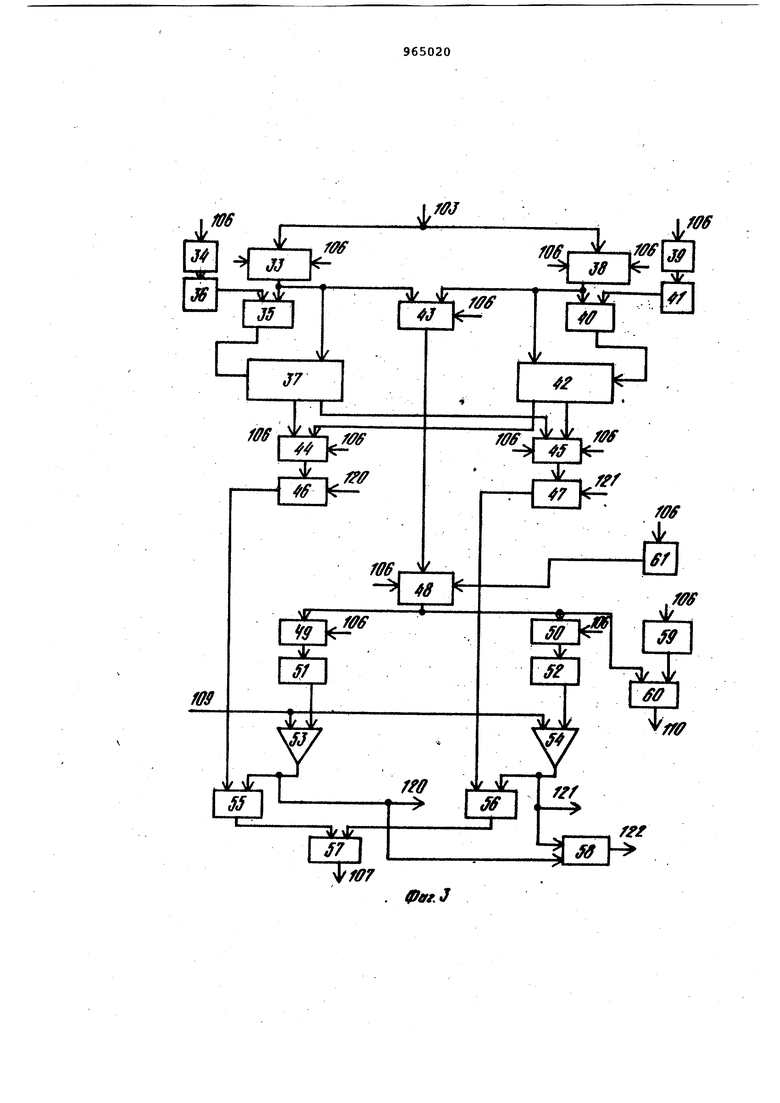

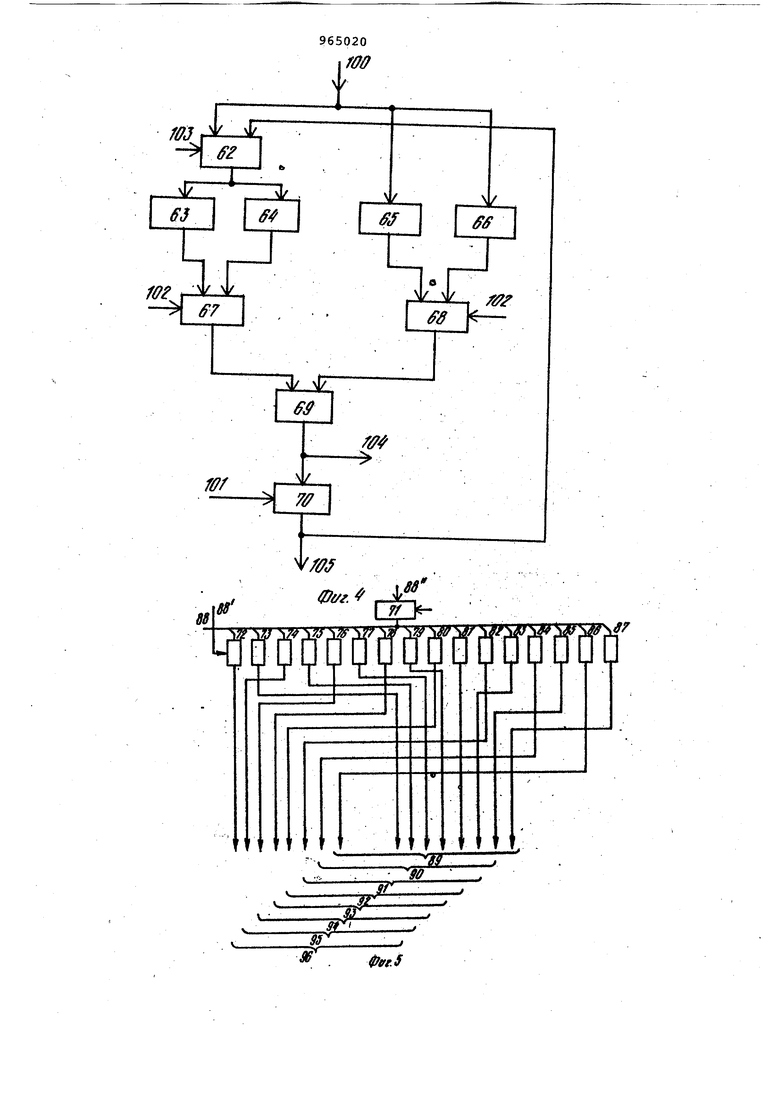

Недостатке данного- устройства является невысокая сложность (ре30альность) синтезируемого изображения, что характеризуется малым числом отобргикаемых за время кадра точечных объектов и обусловлено кспользованием способа вывода, иденти ного для всех точечных источников света, независимо от их физической природы. Используемый в нем способ вывода точечных объектов на экран ЭЛТ характеризуется тем, что интервал времени между выводом двух последовательных точечных объектов, определяется числом одинаковых по размеру зон разбиения экра,на ЭЛТ, расположенных между позициями анализируемых объектов на экране. Цель изобретения - повышение ин формативности имитируемой визуальной обстановки. . Поставленная цель достигается те что в телевизионный имитатор, содер жащий последовательно соединенные буферную цифровую вычислительную ма шину, интерфейс/ и видеопроцессор, а также блок яркости и блок .формиро вания сигналов отклонения, первый и второй выход которого подключен к соответствующим входам электронно лучевой трубки (ЭЛТ), введены блок граничных точек, блок интерполяции блок регулярных точек, блок управления и два мультиплексора, при это первый выход видеопроцессора через перйый мультиплексор соединен с пер вым входом блока яркости, второй выход видеопроцессора через второй мультиплексор соединен с вторым вхо дом блока яркости, выход, которого подключен к первому входу блока ин терполяции , третий: выход видеопроце сора через блок граничных точек сое динен с вторым входом блока интерполяции, с входом блока формирования сигналов отклонения и с первым входом блока регулярных точек, вто рой вход .которого через блок управ ления соединен с четвертым выходом видеопроцессора, причем второй выход блока управления подключен к в рому входу блока граничных точек, третий выход блока управления подключен к третьему входу блока интерполяции, второй выход которого соединен с вторым входом первого мультиплексора, а первый выход с соответствующим входом ЭЛТ, трет выход блока формирования сигналов отклонений соединен с вторым входом второго мультиплексора, а четвертый выход блока формирования с,и налов отклонения соединен с третьим входом блока регулярных точек первый выход.которого подключен к соответствующему входу ЭЛТ, а второй - к четвертому входу блока интерполяции ,° причем блок граничных точек содержит дйа счетчика, два блока оперативной памяти и мул 5Типлексор, при этом выход первого счетчика через первый блок оперативной памяти соединен с первым входом мультиплексора, второй вход которого через второй блок оперативной памяти соединен с выходом второго счетчика, второй вход первого блока оперативной памяти соединен с вторым входом второго блока оперативной памяти и является первым входом блока граничных точек, соответствующий вход мультиплексора и первого и второго счетчиков является вторым входом блока граничных точек, а выход мультиплексора является выходом блока граничных точек, кроме того, блок регулярных точек содержит два канала, каждый из которых состоит из двух счетчиков, блока постоянной ламяти, сумматора, блока оперативной памяти, мультиплексора, сдвигового регистра, регистра, цифроаналогового преобразователя (ЦАП), компаратора и элемента И, при этом выход первого счетчика через блок постоянной памяти соединен с первым входом сумматора, к второму входу которого подключен выход второго счетчика и первый вход блока оперативной памяти, выход сумматора соединен с вторым входом блока оперативной памяти, первый выход которого через последовательно соединенные мультиплексор и сдвиговый регистр подключен к первому входу элемента И, к второму входу которого подключен,через последовательно соединенные ЦАП и компаратор выход регистра, причем вход второго счетчика первого канала соединен с входом второго счетчика второго канала и является первым входом блока регулярных точек, выход второго счетчика первого канала подключен к первому входу первого дополнительного мультиплексора, а выход второго счетчика второго канала подключен к второму входу первого дополнительного мультиплексора, выход которого соединен через дополнительный счетчик с входом регистров первого и второго каналов и с первым входом блока сравнения, к второму входу которого подключен выход дополнительного регистра, второй выход блока оперативной Пс1мяти первого канала соединен с вторым входом мультиплексора второго канала, второй выход блока оперативной памяти второго канала с вторым входом мультиплексора первбго канала, второй вход сдвигового регистра первого канала подключен к второму входу сдвигового .регистра второго канала, вход второго дополнительного мультиплексора соединен с вторым входом дополнительного счетчика, при этом соответствующие входы второго дополнительного мультиплексора, перво го дополнительного мультиплексора, .мультиплексоров каналов, счетчиков каналов, сдвиговых регистров каналов, регистров каналов, дополнитель го счетчика и дополнительного регистра являются вторьлм входом блока регулярных точек, второй вход компаратора первого канала соединен с вторым входом компаратора второго канала и является третьим входом блока регулярных точек, выход компа ратора первого канала подключен к. первому входу первого элемента ИЛИ а выход компаратора второго канала подключен к второму входу первого -элемента ИЛИ, выход которого является вторым выходом блока регулярных точек, выход элемента И первого канала подключен к первому входу второго элемента ИЛИ, а выход элемента И второго канала подключен к второму входу второго элемента ИЛИ, выход которого является первым выходом блока регулярных точек, причем блок интерполяции содержит три мультиплексора, пять регистров и сумматор, при этом первый вход первого мультиплексора соединен с входом первого и второго регистров , выход первого мультиплексора подключен к входу третьего и четвертого регистров, выходы которы через второй мультиплексор соедииены с первым входом сумматора,к вт рому входу которого череэ третий мультиплексор подключены выходы пер вого и второго регистров, выхоД сум матора через пятый регистр подключен к второму входу первого мультиплексора, причем первый вход первог мультиплексора является первым входом блока интерполяции,третий вход вторым входом блока интерпрляции,со оответствующие входы второго и трет го мультиплексоров являются третьим входом блока интерполяции, второй вход пятого регистра является, четве .тым входом блока интерполяции, выхо пятого регистра является первым выходом блока интерполяции, а выход сумматора является вторым выходом блока интерполяции. На фиг.1 изображена структурная схема предлагаемого устройства на фиг.2 - структурная схема блока гра ничных точек и блока формирования сигналов отклонения; на фиг.З структурная схема блока регулярных точек; на фиг.4 - структурная схема блока интерполяции; на фиг.5 - иллюстрация способа организации ОЗУ данных; на фиг.6 - регулярная точеч ная структура. Устройство содержит мультиплексо ры 1 и 2, блок 3 граничных точек. блок 4 формирования сигналов отклонения, блок 5 регулярных точек, блок 6 яркости,;блок 7 интерполяции, блок 8 управления. Блок граничных точек 3 содержит два счетчика 9 и 10, два блоки 11 12 оперативной памяти, мультиплексор 13. Блок 4 формирования сигналов отклонения содержит блок 14 приращений, генератор 14-1. вектора х, генератор . 14-2 вектора у, блок 15 отклонения х, блок 16 отклонения у, блок 17 включения. Блок приращений 14 содержит регистр 18, сумматоры 19 и 20, инвертор 21, два узла 22 и 23 формирования абсолютной величины, компаратор 24, мультиплексор 25 и дешифратор 26. Генератор 14-1 вектора х содержит 1Регистр 27, ЦАП 28, интегратор 29. Генератор 14-2 вектора у включает в себя регистр 30, ЦАП 31, интегратор 32. Блок 5 регулярных точек содержит счетчики 33 и 34, сумматор 35, блок 36постоянной памяти, первый блок 37оперативной памяти, счетчики 38 и 39, сумматор 40, блок 41 постоянной памяти, второй блок 42 оперативной памяти, мультиплексоры 43-45, сдвиговые регистры 46 и 47, счетчик 48, два регистра 49 и 50, два ЦАП 51 и 52, два аналоговых компаратора 53 и 54, два элемента И 55 и 56, два элементаИЛИ 57 и 58, регистр 59, блок 60 сравнения и мультиплексор 61, БЛОК 7 интерполяции содержит . мультиплексор 62, регистры 63-66 два мультиплексора 67 и 68, сумматор 69, регистр 70. Оперативная память организована в группу с произвольным доступом и содержит ОЗУ 71-87 с соединительными линиями 88-96. Общая структурная схема содержит буферную цифровую-машину 97 (ЦМ) с интерфейсом связи, видеопроцессор 98 и ЭЛТ 99. На фиг.1-5 указаны соединительные межблочные линии (шины) 100-122. Предлагаемое устройство предназначено для работы в системах синтеза визуальной обстановки, элементами пространственной сцены которой являкэтся точечные источники света звезды, огни взлетнопосадочной полосы (ВПП), огни города, маяка и и.д.. Это, прежде всего, касается визуальной обстановки для ночных условий полета. Огни ВПП и огни города представляют собой регулярные точечные структуры, каждая из которых образована точечными источниками света, расположенными вдоль одной прямой. На экране ЭЛТ регулярная структура.

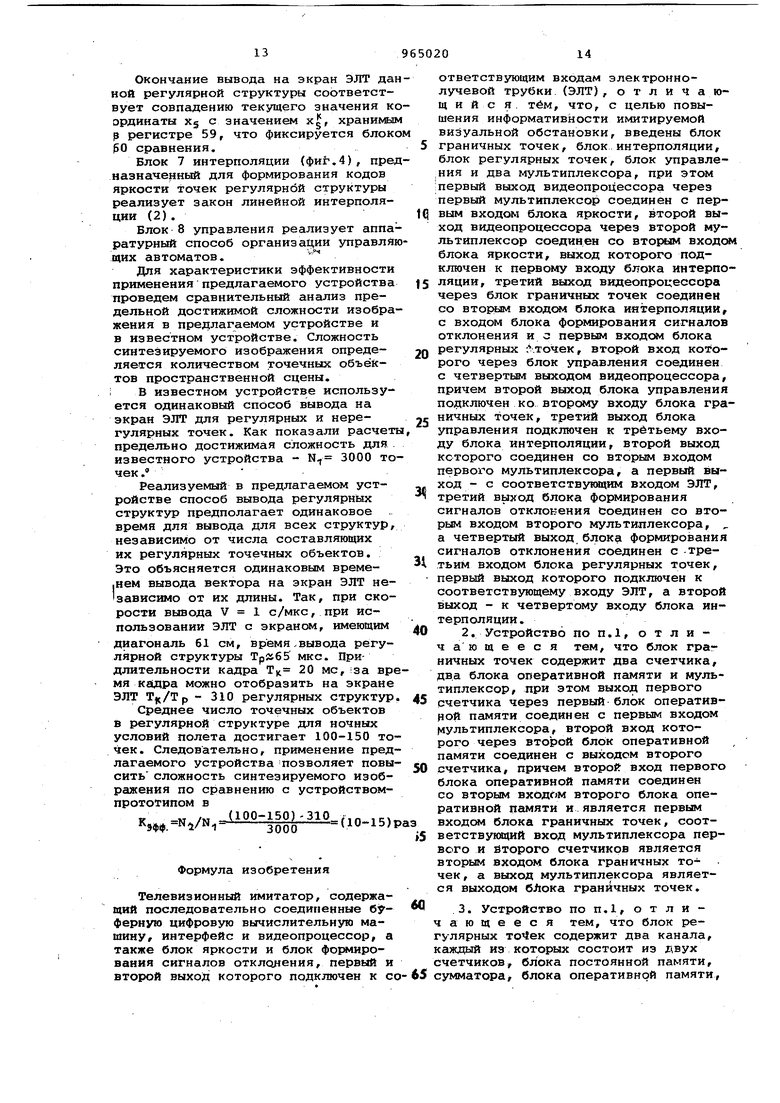

представленная P(P.h) сзветящимися точками, расположенными вдоль одной прямой (фиг.6). Положение каждой точки регулярной структуры на экране ЭЛТ (координаты х и у) и число точек Р определяется видеопроцессором 98, а также буферной ЦМ 97.

Используемый и известном устройстве способ вывода на экран ЭЛТ изображений точечных объектов существен.JO ограничивает сложность синтезируемых изЬбражений за счет введения избыточности по времени на вывод точечного объекта. Так, время вывода Р видимых точек данной регулярной структуры определяется формулой Тр7/1,2Р-Т, где ITp - время вывода точечного объекта, позиция которого на экране отстоит от позиции предыдущего точечного объек-, та на одну зону разбиения экрана ЭЛТ. Суть изобретения заключается в ,использовании сврйства регулярности огней ВПП и огней города, т.е. в наличии различных способов выв.ода для регулярных и нерегулярных огней. Отображаемая регулярная структура с видимыми точками Aj, (Фиг.6) представляется вектором компоненты разложения которого по осям х и у равны AJ А ; ; .

А К

из

Луч ЭЛТ переводится в позицию Хд, начинается вывод вектора AjAj, Оставшиеся видимые огни данной регулярной структуры А4-Ац выводятся на экран путем включения луча ЭЛТ в моменты совпадения значения хд координаты текущего положения лучас вычисленными ранее значениями Xg координаты позиций - соответствующих огней данной регулярной структуры. Яркость свечения люминофора на позициях огней регулярной структуру определяется по закону линейной интерполяции

1,- 1.сУЧ;

1

(1)

4x3 где IK и IH яркости конечного и

начального видимых ( огней.

Юерегулярные огни (звезды, маяки и т.ц;-) выводятся на экран ЭЛТ способом, идентичным описанному в устройстве-прототипе.

Устройство работает следующим образом.

Все время кадра условно разбито на два интервала: время вывода нерегулярных точек и время вывода регулярных точек. Вывод в текущем кадре нерегулярных точек осуществляется согласно координатам xg, уд и

энергетическим характеристикам (яркость, цвет), поступающим непосредственно из видеопроцессора 98.

Вывод регулярных точек осуществляется согласно данным,, вычисляемым ,

видеопроцессором 98 в предыдущем кадре и хранимым в блоке 3 граничных точек и блоке 5 регулярных точек. Закончив обработку нерегулярных точек, видеопроцессор 98 начинает

обработку Регулярных структур для следующего кадра. Для, этого в блок вращения видеопроцессора из базовой ЦМ поступает матрица направляющих косинусов для сле лующего кадра. Видеопроцессор 98 выполняет перспективные преобразования над огнями регулярной структуры. Результаты преобразований, используемые предлагаемым устройством в следующем кадре

поступают на хранение в блок 3 граничных точек и блок 5 регулярных точек. В блок 3 граничных точек поступают координаты х, .у, х, у, коды I к и IH а также код цвета огней

данной регулярной структуры. В блок 5 регулярных точек поступают координаты огней, данной регулярной структуры. Таким образом, после окончания в текущем кадре обработки

предлагаемым устройством и видеопроцессором нерегулярных точек одновременно . начинаются два процесса: видеопроцессор обрабатывает регулярные структуры для следующего кадра

и посылает результаты обработки в блок 3 граничных точек и блок 5 регулярных точек, заявляемое устройство осуществляет вывод регулярных структур в соответствии с данными,

полученными из видеопроцессора 98

в предыдущем кадре и хранимыми в блоке 3 граничных точек и блока 5 регулярных точек. Из блока 3 граничных точек в блок 7 интерполяции,-в блок

4 формирования сигналов отклонения и блок 5 регулярных точек поступают соответственно кодыяркости 1, I и координаты х, у, х|, у. Блок формирования сигналов отклонений переводит луч в позицию х, у, формирует компоненты вектора дхд, лу и по сигналу из блока 5 регулярных точек начинает вывод вектора Ац,Ак (вектор AjA на фиг.6), Блок 7 интерполяции определяет разность IK-IH

которая поступает в блок б яркости через мультиплексор 1 по шине 104. Одновременно из блока 4 формирования сигналов откло{1ения через мульти.плексор 2 по шине 110 в блок б яркости поступает разность лх.Блок 6 яркости вычисляет , которое посылает затем в блок 7 интерполяции ПО шине 100. Одновременно с началом ввода вектора А)А| блок 7 интерполяции формирует значение яркости в соответствии с (1). При выводе регулярных точек блок 4 формирования си налов отклонения управляет выводом на экран ЭЛТ 99 вектора , блок регулярных точек формирует сигналы включения луча ЭЛТ, блок 7 интерполяции формирует коды яркости. Блок. 3 граничных точек, показанный на фиг,2, предназначен для храs s s нения координат X кодов 1(, 1) соответственно начальной и конечной видимых точек регулярной структуры (точки А J и А| на фиг,б) для текущего и следующего кадров. , При обработке видеопроцессором 98 регулярных, структур для следующего кадра.координаты и коды Xg, у IH/ Xg, Удг IK для,каждой регулярной структуры одна за другой поступают по шине 113 в блок 11 оператив ной памяти, куда записываются согласно адресам, формируемым, счетчиком 9. Одновременно с этим, при выводе предлагаемым устройством регулярных структур в текущем кадре, аналогичные координаты и коды считаются из блока 12 оперативной памяти, по адресам, формируемым сче чиком 10, и поступают через мультиплексор 13 в блоки 7, 4 и 5, В ел дующем кадре все происходит наоборо считывание из блока 11, запись в блок 12 и -т.д. Координаты х и у из блока 3 гр ничных точек поступают в блоки отклонения X 15 и у 16, что приводит к перемещению луча ЭЛТ в позицию х у. В сумматорах 19 и 20 блока 14 приращений после поступа:ения коорди нат х и х|, УдИ у формируются раз ности соответственно лхд и дудг которые, поступают затем в генераторы векторов X и у 14-1 и14-2 соответственно, где и формируются линейнонарастающие напряжения компонент вектора АнАкБлок 5 регулярных точек (фиг.З) предназначен для хранения координат Xg видимых точек регулярных структур для текущего и следующего кадров, а также для формирования сигналов включения луча ЭЛТ 99, Входные каналы блока 5 предназначены для организации режима записи (считывания) в блоках 37 и 42. Каждый из блоков 37 и 42 оперативной памяти поочередно работает в режимах записи (для следующего кадра) и считывания (для текущего кадра). Организация блоков 37 и 42 приведена на фиг.5, При поступлении в входной канал координаты Xg видимого огня, в соответствующую ячейку соответствующей микросхемы записывается логическая единица. Например, первая строка блоков 37 и 42 хранит (в направлении слева направо) характеристики от нулевой до пятнадцатой ячейкикоординатной сетки Хд, вторая строка - от шестнадцатой до тридцать первой и т.д. Восемь старших разрядов поступающей по шине 88 координаты xg видимого огня подаются по шине 88 (фиг,5) на адресные входы, обусловливая тем самым выбор соответствующей строки, а четыре младших разряда, поступающие на вход блока 71, обусловливают появление единицы на соответствующем врходе блока 71, которая поступает на вход Разрешение соответствующей Микросхемы. шестнадцати микросхем объединены IB две группы по восемь разрядой в каждой. Первая группа объединяет выходы микросхем с нечетными номерами (первой, третьей и т.д.), вторая - выходы микросхем с четными номерами (второй, четвертой и т.д.). Запись в блоке .оперативной памяти, например 37, происходит следующим образом. В счетчик 34 из блока В управления поступает порядковый номер обрабатываемой видеопроцессором регулярной структуры, который затем поступает на адресные входы блока 36, в котором для каждой регулярной структуры записан номер начальной ртроки соответствующей ей зоны 5лока 37 (например, 64 строки данлых счетчика 39 - для второй регулярной структуры). Номер начальной строки блока 37 для соответствующей регулярной структуры с выхода блока 36 поступает на вход cyNwaтора 35, на другой вход которого поступает восемь старших разрядов кода хМ, хранимого в счетчике 33. Номер строки, в которой происходит запись, поступает с выхода сумматора 35 на адресные входы микросхем блока 37, Считывание из блока бперативной памяти, например 42, происходит следующим образом. в счетчик 38 записывается код х§ отображаемой регулярной структуры. На выходе блока 41 вышеописанным способом формируется номер начальной строки зоны для соответствующей регулярной структуры, на выходе сумматора 40 - номер строки, которая содержит информацию о точке АН (логи-. ческие О или логическая ). В режиме считывания на четырех младших разрядах кода хранимогоBi счетчике 38, присутствуют постоянные нули. Для организации последовательного опроса всех строк блока 42, хранящих информацию о точках А-Ац данной ёгулярной структуры, счетчик 38

включается в режим суммирования (вычитания) , что приводит к формирован ю на выходе qyMMaTopa 40 номеров последовательно опрашиваемых строк блока 42. В режиме суммирования (вычитания) участвуют только восемь старших разрядов счетчика 38. Операция суммирования в сумматоре 40 соответствует условию ()0, операция вычитания - условию (Хд-х|)0.

В сдвиговые регистры 46 и 47 через мультиплексоры 44 и 45 поступают соответственно восемь нечетных разрядов и восемь четных разрядов очередной, считываемой строки того из„блоков оперативной памяти, который работает в режиме считывания.

Сдвиг влево в регистрах 46 и 47 соответствует (хд-х|);0, сдвиг впра-г во - (Xg- Xg)0. На выходах регистров 46 и 47 одновременно появляется информация о двух точках координатной оси xg экрана ЭЛТ (логическая 1 означает Включить луч ЭЛТ). Перед началом вывода данной регулярной структуры, содержимое счетчиков 33 (38) через мультиплексор 43 записывается в реверсивный счетчик 48. Режим суммирования (вычитания) счетчика 48 соответствует случаям (xg- х|)0 и (xg - х|)0. Коды с выхода счетчика 48 порчередно записываются в регистры 49 и sot В этом режиме на счетный вход счетчика 48 через мультиплексор 61 поступают Импульсы из блока 8 управления. Содержимое регистров 49 и 50 пройдя через ЦАП 51 и 52, поступает в виде аналогового напряжения на входы компараторов 53 и 54, на другие входы которых поступает напряжение, соответствующее Хд, из генератора вектора х 14-1., Момент достижения содержимого счетчика 48, зн чения, равного Хд, фиксируется элементом ИЛИ 58, что приводит к прекращению рабрты счетчика 48 и к прег кращению сдвига в регистрах 48 и 47 который происходил одновременно со счетом в счетчике 48. К этому моменту на выходах одного из регистров 46 и 47 присутствует информация о точке АИ, в другом- - о рядом расположенной точке оси xg (слева или справа от точки АН), ана выходах регистЬов 49 и 50 - код х и код () ( плюс - для случая ( х§)0; минус - для случая (х§- х)0. Далее, блок 8 управления формирует одиночный импульс, кото-;, рый поступает через мультиплексор 61 на счетный вход счетчика 48 и увеличивает (уменьшает) содержимое счетчика 48 на единицу. Код с выхода счетчика 48 записывается в тот из регистров 49и 50, который не хранит ко х. Следует отметить, что частота импульсов сдвига регистров 46 и 47 вдвое меньше частоты импульсов счета счетчика 48.

На этом этап предварительной подготовки к выводу на экран данной регулярной структуры закончен. На этапе непосредственного вывода данной регулярной структуры включаются генераторы векторов X 14-1 и у 14-2, на входы компараторов 53 и 54 поступает линейно-нарастающее напряжение из генератора х 14-1, в регистрах 46 и 47 происходит сдвиг, счетчики 38 (39) и 48 работают в режиме суммирования (-вычитания). При этом на выходах регистров 46 и 47 появляется информация, о включении луча в со-. ответствующем положении по оси Хд на выходе счетчика 48 - координата Xg последовательных точек оси Хд, расположенных в интервале , на выходах компараторов 53 и 54 - сигналы,, фиксирующие во времени моменты достижения лучом ЭЛТ соответствующих положений на оси Хд. На Входы элементов И 55 и 56 поступают одноразрядные коды с выходов регистров 46 и 47 и сигналы с выходов компараторов 53 и 54. При наличии единиц на входах каждого из элементов И на его выходе появляется сигнал включения луча ЭЛТ, который поступает Через элемент ИЛИ 57 по шине 107 |на вход ЭЛТ.

На этапе вывода счет в счетчиках 38 и 33 сдвиг в регистрах 46 и 47, запись в регистры 49 и 50 происходит по сигналам с выходов компараторов 53 и 54, которые поступают в блок 8 управления (по шинам112 и 113), а из него по шине 106 на вход мультиплексора 61. Сигналы с выходов компараторов 53 и 54 поступают через элемент ИЛИ 58 в блок 8 управления по шине 122, а по соответствующей шине на вход мультиплексора 61, что приводит к увеличению (уменьшению) содержимого счетчика 48 на единицу, а затем к записи содержимого счетчика 48 в соответствующий регистр (49 либо 50). Например, появление сигнала на выходе компаратора 53 приводит к изменению содержимого счетчика 48 на единицу и к записи в регистр 49.

При (х|- х|)0 сдвиг влево в регистрах 46 и 47 происходит по сигналу с выхода компаратора-53, при (xg- х|)0 - по сигналу с выхода компаратора $4. В режиме вывода блок 8 управления формирует счетные импульсы для счетчиков 38 (33) путем выборки из импульсов, появляющихся на выходе элемента ИЖ 58, каждого восьмого импульса, что приводит к обработке содержимого очередной строки

5 блока 42 (37). Окончание вывода на экран ЭЛТ да ной регулярной структуры соответствует совпадению текущего значения к ординаты Хд с значением Xg, хранимд р регистре 59, что фиксируется блок рО сравнения. Блок 7 интерполяции (фиг ,4) , пре назначеннЕлй для формирования кодов яркости точек регулярной структуры реализует закон линейной интерполяции (2). Блок 8 управления реализует аппа ратурный способ организа1;ии управля щих автоматов. Для характеристики эффективности применения предлагаемого устройства проведем сравнительный анализ предельной достижимой сложности изобра жения в предлагаемом устройстве и в известном устройстве. Сложность синтезируемого изображения опреде- ляется количеством точечных объектов пространственной сцены. ; В известном устройстве используется одинаковый способ вывода на экран ЭЛТ для регулярных и нерегулярных точек. Как показали расчет предельно достижимая сложность для известного устройства - К 3000 то чек. Реализуемый в предлагаемом устройстве способ вывода регулярных структур предполагает одинаковое время для вывода для всех структур, независимо от числа составляющих их регулярных точечных объектов. Это объясняется одинаковым време.нем вывода вектора на экран ЭЛТ независимо от их длины. Так, при скорости вывода V 1 с/МКС, при использовании ЭЛТ с экраном, имеющим диагональ 61 см, время,вывода регулярной структуры МКС. Придлительности кадра Тц 20 мс,:за вре мя кадра можно отобразить на экране ЭЛТ - 310 регулярных структур Среднее число точечных объектов в регулярной структуре для ночных условий полета достигает 100-150 точек. Следовательно, применение предлагаемого устройства позволяет повысить сложность синтезируемого изображения по сравнению с устройствомпрототипом в (100-150)-310 {10-15)р 3000 Формула изобретения Телевизионный имитатор, содержащий последовательно соединенные б ферную цифровую вычислительную машину, интерфейс и видеопроцессор, а также блок яркости и блок форялирования сигналов отклонения, первый и второй выход которого подключен к со ответствующим входам электроннолучевой трубки (ЭЛТ), отличающ и и с я. тем, что, с целью повышения информативности имитируемой визуальной обстановки, введены блок граничных точек, блок интерполяции, блок регулярных точек, блок управления и два мультиплексора, при этом ; первый выход видеопроцессора через первый мультиплексор соединен с первым входом блока яркости, второй выход видеопроцессора через второй мультиплексор соединен со вторым входом блока яркости, выход которого подключен к первому входу блока интерполяции, третий выход видеопроцессора через блок граничных точек соединен со вторым ВХОДО1 блока интерполяции, с входом блока формирования сигналов отклонения и о первым входсм блока регулярных .точек, второй вход которого через блок управления соединен с четвертым выходом видеопроцессора, причем второй выход блока управления подключен ко вторс 1у входу блока граничных точек, третий выход блока управления подключен к третьему входу блока интерполяции, второй выход которого соединен со вторым входом первох о мультиплексора, а первый выход - с соответствукнцим входом ЭЛТ, третий выход блока формирования сигналов отклонения Соединен со вторым входом второго мультиплексора, а четвертый выход блока формирования сигналов отклонения соединен с третьим входом блока регулярных точек, первый выход которого подключен к соответствующему входу ЭЛТ, а второй выход - к четвертому входу блока интерполяции. 2. Устройство по п.1, отличающееся тем, что блок граг ничных точек содержит два счетчика, два блока оперативной памяти и мультиплексор, при этом выход первого счетчика через первый блок оперативной памяти соединен с первым входом (мультиплексора, второй вход которого через второй блок оперативной памяти соединен с выходом второго счетчика, причем второй вход первого блока оперативной памяти соединен со вторым входом второго блока оперативной памяти и является первым входом блока граничных точек, соответствукяций вход мультиплексора первого и второго счетчиков является вторым входом блока граничных точек , а выход мультиплексора является выходом бЛока граничных точек. 3. Устройство по п.1, отлиающееся тем, что блок реулярных содержит два канала, аждый из которых состоит из двух четчиков, блока постоянной памяти, умматора, блока оперативной памяти. мультиплексора, сдвигового регистра регистра, цифроаналогового преобразователя (ЦАП), компаратора и элемента И, при этом выход первого сче чика через блок постоянной памяти соединен с первым входом сумматора, ко второму входу которого подключен выход второго счетчика и первый вхо блока оперативной памяти, выход сум матора соединен со вторым входом блока оперативной памяти, первый вы ход которого через последовательно соединенные мультиплексор и сдвиго)вый регистр подключен к первому вхо ду элемента И, ко.второму входу которогр подключен через последовател НС соединенные ЦАП и компаратор выход регистра, причем вход второго счетчика первого канала соединен с входом второго счетчика второго канала и является первым входом блока регулярных точек, выход второго сче чика первого канала подключен к первому входу первого дополнительно го мультиплексора, а выход-второго счетчика второго канала подключен ко второму входу первого дополнительного мультиплексора, выход которово соединен через дополнительный счетяик с входом регистров первого и вто|эого каналов, и с первым входом блока сравнения, ко второму входу которого подключен выход дополнительного регистра, второй выход блока оперативной памяти первого канала соединен со вторым входом мультиплексора второго канала, второй выход блока оперативной памяти второго канала соединен со вторым входом мультиплексора первого канала, второй вход сдвиго.вого регистра первого канала подключен ко второму входу, сдвигового регистра второго канала, выход второго дополнительного мультиплексора соединен со вторым входом дополнительного счетчика, при этом соответ ствующие входы второго дополнительного мультиплексора, первого дополнительного мультиплексора, мультиплексоЬов каналов,счетчиков каналов .сдвиговых регистров каналов,регистр каналов, дополнительного счетчика дополнительного регистра являются вторым входом блока регулярных точек, второй вход компаратора первого канала соединен со вторым входом компаратора второго канала и является третьим входом блока регулярных точек, причём выход компаратора первого канала подключен к первому входу первого элементаИЛИ, а выход компаратора второго канала подключен ко второму входу первого элемента ИЛИ, выход которого является вторым выходом блока регулярных точек, выход элемента И первого канала подключен к первому входу второго элемента ИЛИ, а- выход элемента И второго канала подключен ко второму входу BTopgro элемента ИЛИ, выход которого является первым выходом блока регулярных точек. 4. Устройство ПОП.1, отличающеес.я тем, что блок интерполяции содержит три мультиплексора, пять регистров и сумматор, при этом первый вход первого мультиплексора соединен с входом первого и второго регистров, выход первого мультиплексора подключен к входу третьего и четвертого регистров, выходы .которых через второй мультиплексор соединены с первым входом сумматора, ко второму входу которого через третий мультиплексор подключены выходы первого и второго регистров, выход сумматора через пятый регистр подключен ко второму входу первого мультиплексора, причем первый вход первого мультиплексора является первым входом блока интерполяции, третий вход - вторым входом блока интерполяции, соответствующие входы второго и третьего мультиплексоров являются третьим входом блока интерполяции, второй вход пятого регистра является четвертым входом блока интерполяции, выход пятого регистра является, первым выходом блока интерполяции, а выход сумматора является вторым выходом блока интерполяции. Источники информации, , принятые во внимание при экспертизе 1. Патент США 4,027,4037 кл. Н 04 N 7/18, 1977. 2. Патент США 4,077,062, кл. G 09 В 9/08; Н 04 N 7/00, 28.02.78 (прототип).

фиг, 2

eff.J

Авторы

Даты

1982-10-07—Публикация

1981-01-26—Подача