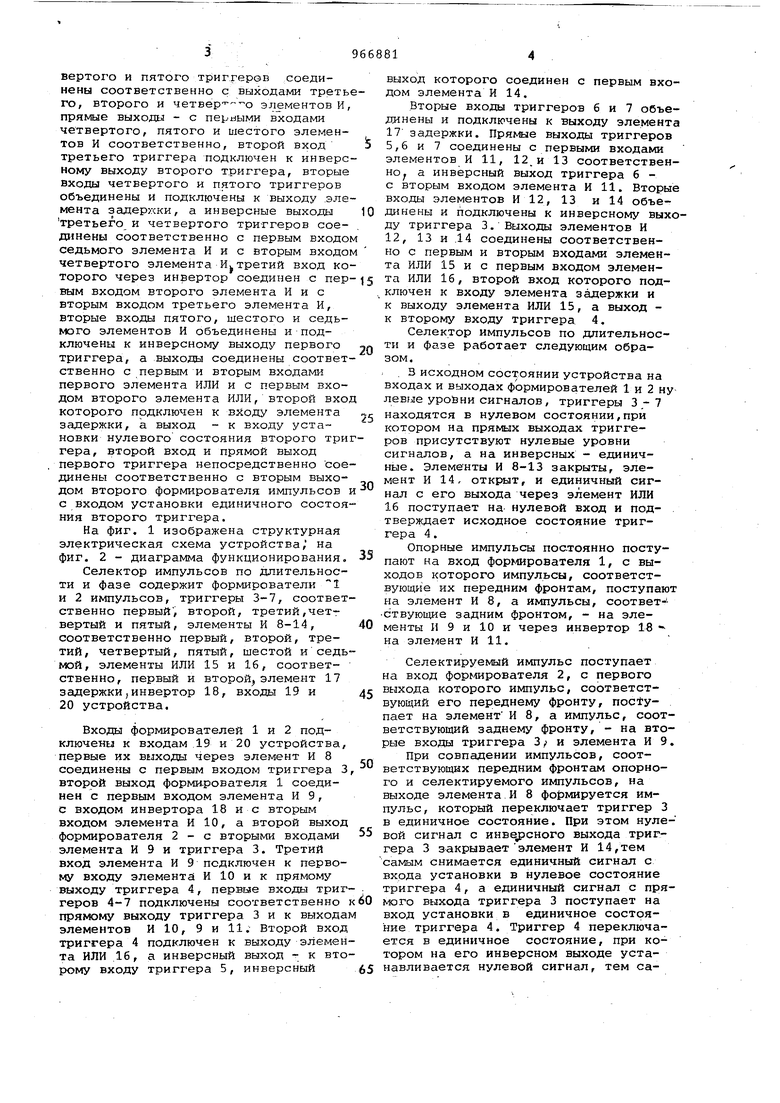

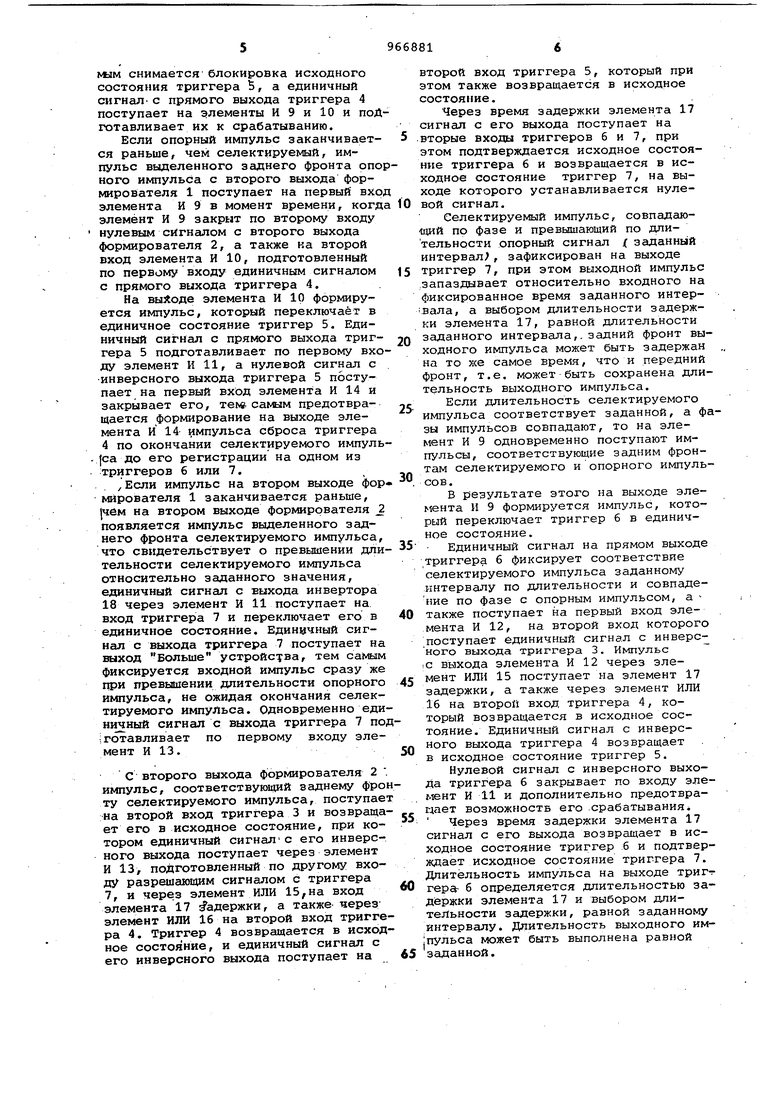

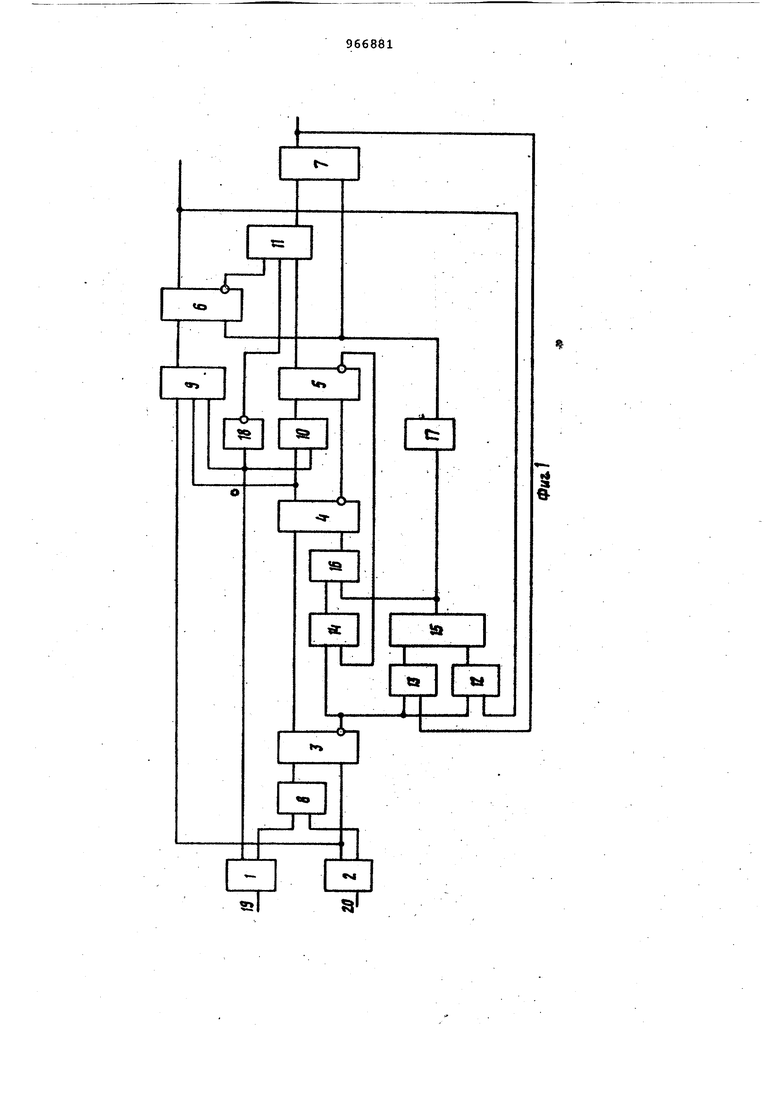

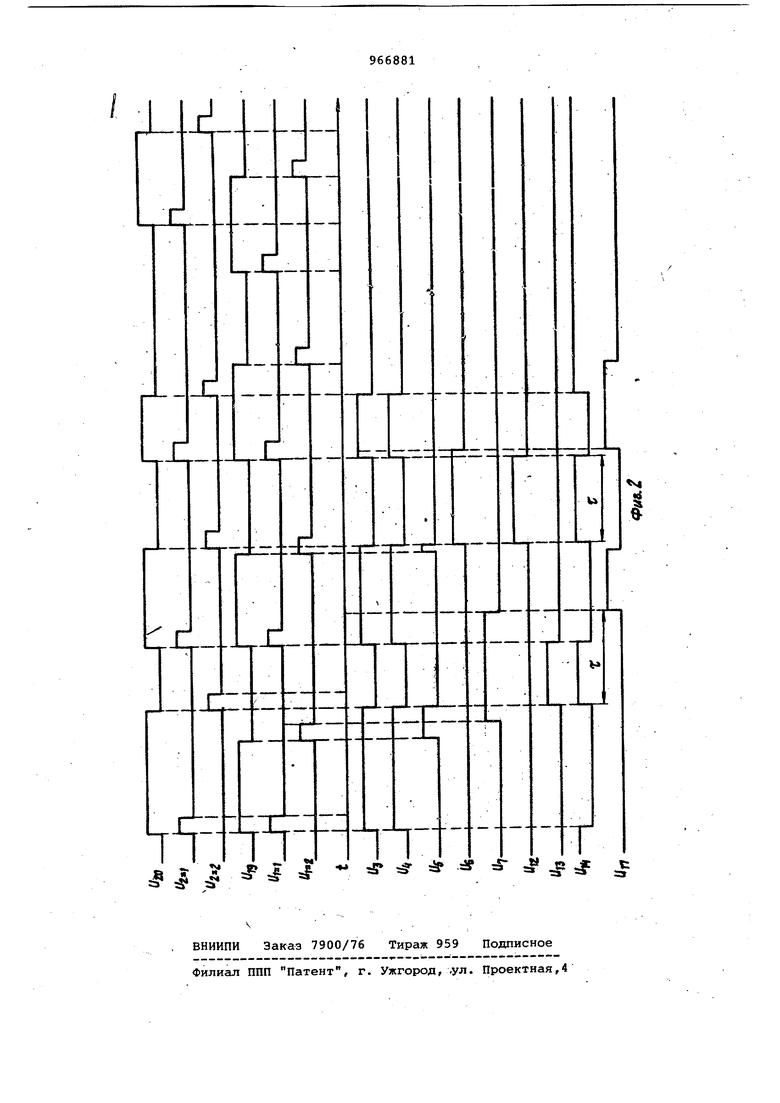

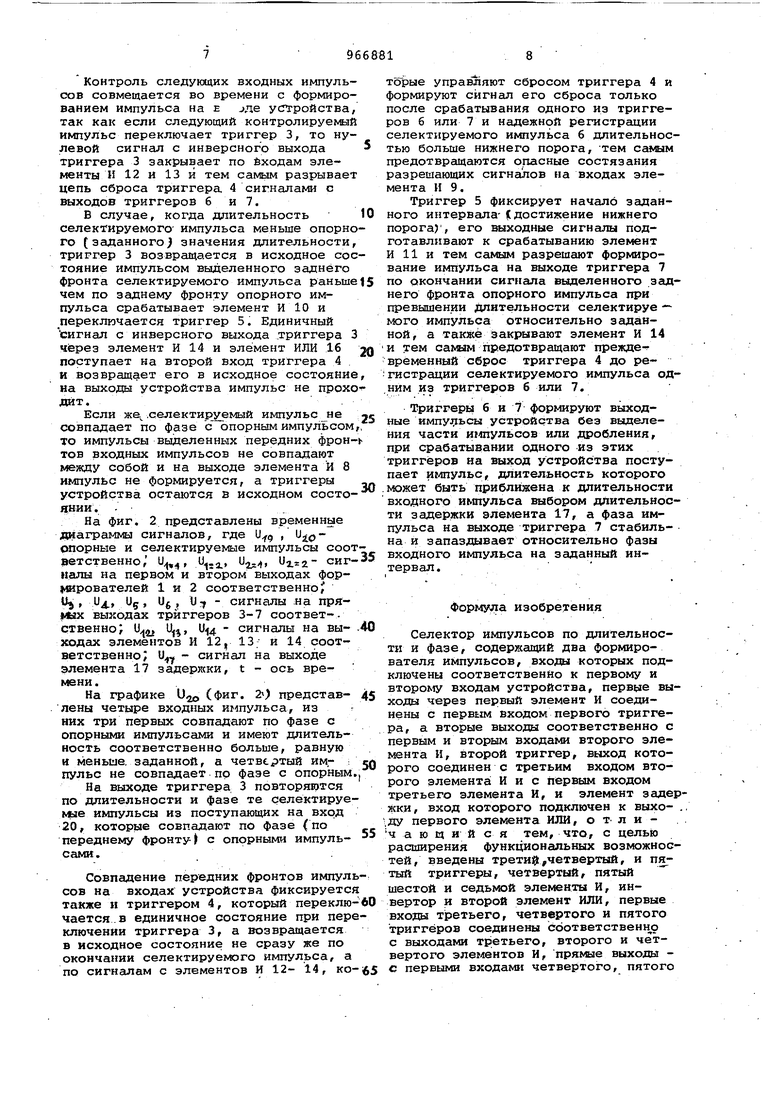

вертого и пятого триггеров соединены соответственно с выходами треть го, второго и четвер- - о элементов И прямые выходы - с первыми входами четвертого, пятого и шестого элементов И соответственно, второй вход третьего триггера подключен к инверс ному выходу второго триггера, вторые входы четвертого и пятого триггеров объединены и подключены к выходу эле мента задеркки, а инверсные выходы третьего и четвертого триггеров соединены соответственно с первым входо седьмого элемента И и с вторым входо четвертого элемента И третий вход ко торого через инвертор соединен с пер вым входом второго элемента И и с вторым входом третьего элемента И, вторые входы пятого, шестого и седьмого элементов И объединены и подключены к инверсному выходу первого триггера, а выходы соединены соответ ственно с первым и вторым входами первого элемента ИЛИ и с первым входом второго элемента ИЛИ, второй вхо которого подключен к элемента задержки, а выход - к входу установки нулевого состояния второго ТрИ гера, второй вход и прямой выход первого триггера непосредственно сое динены соответственно с вторым выходом второго формирователя импульсов с входам установки единичного состоя ния второго триггера. На фиг. 1 изображена структурная электрическая схема устройства, на фиг. 2 - диаграмма функционирования. Селектор импульсов по длительности и фазе содержит формирователи 1 и 2 импульсов, триггеры 3-7, соответ ственно первый , второй, третий,четвертый и пятый, элементы И 8-14, соответственно первый, второй, третий, четвертый, пятый, шестой и седь мой, элементы ИЛИ 15 и 16, соответственно, первый и второй, элемент 17 задержки,инвертор 18, входы 19 и 20 устройства. Входы формирователей 1 и 2 подключены к входам 19 и 20 устройства, первые их ВЕ1ходы через элемент И 8 соединены с первым входом триггера 3 второй выход формирователя 1 соединен с первым входом элемента И 9, с входом инвертора 18 и с вторым входом элемента И 10, а второй выход формирователя 2-е вторыми входами элемента И 9 и триггера 3. Третий вход элемента И 9 подключен к первому входу элемента И 10 и к прямому выходу триггера 4, первые входы триг геров 4-7 подключены соответственно прямому выходу триггера 3 и к выхода элементов И 10, 9 и 11. Второй вход триггера 4 подключен к выходу элемен та ИЛИ 16, а инверсный выход - к вто рому входу триггера 5, инверсный выход которого соединен с первым входом элемента И 14. Вторые входы триггеров 6 и 7 объединены и подключены к выходу элемента 17 задержки. Прямые выходы триггеров 5,6 и 7 соединены с первыми входами элементов И 11, 12.и 13 соответственно а инверсный выход триггера 6 с вторым входом элемента И 11. Вторые входы элементов И 12, 13 и 14 объединены и подключены к инверсному выходу триггера 3. Выходы элементов И 12, 13 и .14 соединены соответственно с первым и вторым входами элемента ИЛИ 15 и с первым входом элемента ИЛИ 16, второй вход которого подключен к входу элемента задержки и к выходу элемента ИЛИ 15, а выход к второму входу триггера 4. Селектор импульсов по длительности и фазе работает следующим образом. : . 3 ИСХОДНОМ состоянии устройства на входах и выходах формирователей 1 и 2 ну лeвFлe уроЬни сигналов, триггеры 3-7 находятся в нулевом состоянии,при котором на прямых выходах триггеров присутствуют нулевые уровни сигналов, а на инверсных - единичные. Элементы И 8-13 закрыты, элемент И 14, открыт, и единичный сигнал с его выхода через элемент ИЛИ 16 поступает на- нулевой вход и подтверждает исходное состояние триггера 4. Опорные импульсы постоянно поступают на вход фop 1иpoвaтeля 1, с выходов которого импульсы, соответствующие их передним фронтам, поступают на элемент И 8, а импульсы, соответ- ствующие задним фронтом, - на элементы И 9 и 10 и через инвертор 18 на элемент И 11. Селектируемый импульс поступает на вход фop Iиpoвaтeля 2, с первого выхода которого импульс, соответствующий его переднему фронту, noctyпает на элемент И В, а импульс, соответствующий заднему фронту, - на вторые входы триггера 3; и элемента И 9. При совпадении импульсов, соответствующих передним фронтам опорного и селектируемого импульсов, на выходе элемента И 8 фо|)мируется импульс, который переключает триггер 3 в единичное состояние. При этом нулевой сигнал с HHBejJCHoro выхода триггера 3 закрываетэлемент И 14,тем самым снимается единичный сигнал с входа установки в нулевое состояние триггера 4, а единичный сигнал с прямого выхода триггера 3 поступает на вход установки в единичное состояние триггера 4. Триггер 4 переключается в единичное состояние, при котором на его инверсном выходе устанавливается нулевой сигнал, тем саNtiM снимается блокировка исходного состояния триггера 5, а единичный сигнал- с прямого выхода триггера 4 поступает на элементы И 9 и 10 и под готавливает их к срабатыванию. Если опорный импульс заканчивается раньше, чем селектируемый, импульс выделенного заднего фронта опо ного импульса с второго выхода формирователя 1 поступает на первый вхо элемента И 9 в момент времени, когд элемент И 9 закрыт по второму входу нулевым сигналом с второго выхода формирователя 2, а также на второй вход элемента И 10, подготовленный по первому входу единичным сигналом с прямого выхода триггера 4. На выводе элемента И 10 формируется импульс, который переключает в единичное состояние триггер 5. Единичный сигнал с прямого выхода триггера 5 подготавливает по первому вхо ду элемент И 11, а нулевой сигнал с инверсного выхода триггера 5 поступает на первый вход элемента И 14 и закрывает его, те№ самым предотвращается формирование на выходе элемента И 14 импульса сброса триггера 4 по окончании селектируемого импуль |са до его регистрации на одном из триггеров 6 или 7. / Если импульс на втором выходе фор мирователя 1 заканчивается раньше, |чем на втором выходе формирователя 2 появляется импульс выделенного заднего фронта селектируемого импульса, что свидетельствует о превышении дли тельности селектируемого импульса относительно заданного значения, единичный сигнал с выхода инвертора 18 через элемент И 11 поступает на вход триггера 7 и переключает его в единичное состояние. Единичный сигнал с выхода триггера 7 поступает на выход Больше устройства, тем самым фиксируется входной импульс сразу же при превышении длительности опорного импульса, не ожидая окончания селектируемого импульса. Одновременно еди ничный сигнал с выхода триггера 7 по Уготавливает по первому входу элемент И 13. С второго выхода формирователя 2 импульс, соответствующий заднему фро ту селектируемого импульса, поступае на второй вход триггера 3 и возврата ет его в исходное состояние, при котором единичный сигналс его инверсного выхода поступает через элемент И 13, подготовленный по другому входу разрешающим сигналом с триггера 7, и через элемент ИЛИ 15,на вход элемента 17 Задержки, а также через элемент ИЛИ 16 на второй вход тригге ра 4. Триггер 4 возвращается в исход ное состояние, и единичный сигнал с его инверсного выхода поступает на второй вход триггера 5, который при этом также возвращается в исходное состояние. Через время задержки элемента 17 сигнал с его выхода поступает на вторые входы триггеров 6 и 7, при этом подтверждается исходное состояние триггера 6 и возвращается в исходное состояние триггер 7, на выходе которого устанавливается нулевой сигнал. Селектируемый импульс, совпадающий по фазе и превышающий по длительности опорный сигнал ( заданный интepвaл, зафиксирован на выходе триггер 7, при этом выходной импульс ,запаздывает относительно входного на фиксированное время заданного интер:вала, а выбором длительности задержки элемента 17, равной длительности заданного интервгша,. задний фронт выходного импульса может быть задержан на то же самое время, что и передний фронт, т.е. может быть сохранена длительность выходного импульса. Если длительность селектируемого импульса соответствует заданной, а фазы импульсов совпадают, то на элемент И 9 одновременно поступают импульсы, соответствующие задним фронтам селектируемого и опорного импульсов. В результате этого на выходе элемента И 9 формируется импульс, который переключает триггер 6 в единичное состояние. Единичный сигнал на прямом выходе триггера 6 фиксирует соответствие селектируемого импульса заданному интервалу по длительности и совпадение по фазе с опорным импульсом, а также поступает на первый вход элемента И 12, на второй вход которого поступает единичный сигнал с инверсного выхода триггера 3. Импульс С выхода элемента И 12 через элемент ИЛИ 15 поступает на элемент 17 задержки, а также через элемент ИЛИ 16 на второй вход триггера 4, который возвращается в исходное состояние. Единичный сигнал с инверсного выхода триггера 4 возвращает в исходное состояние триггер 5. Нулевой сигнал с инверсного выхода триггера 6 закрывает по входу элемент И 11 и дополнительно предотврагдает возможность его .срабатывания. Через время задержки элемента 17 сигнал с его выхода возвращает в исходное состояние триггер 6 и подтверждает исходное состояние триггера 7. Длительность импульса на выходе тригт гера- 6 определяется длительностью задержки элемента 17 и выбором длительности задержки, равной заданному интервалу. Длительность выходного импульса может быть выполнена равной заданной. Контроль следующих входных импульсов совмещается во времени с формированием импульса на Е де устройства так как если следующий контролируе1«ий импульс переключает триггер 3, то нулевой сигнал с инверсного выхода триггера 3 закрывает по ёходам элементы Н 12 и 13 и тем самьлм разрывает цепь сброса триггера 4 сигналами с выходов триггеров 6 и 7. В случае, когда длительность селектируемого импульса меньше опорно го (заданного значения длительности триггер 3 возвращается в исходное сос тояние импульсом выделенного заднего фронта селектируемого импульса раньше чем по заднему фронту опорного импульса срабатывает элемент И 10 и переключается триггер 5. Единичный сигнал с инверсного выхода триггера 3 через элемент И 14 и элемент ИЛИ 16 поступает на второй вход триггера 4 и возвращает его в исходное состояние на выходы устройства импульс не прохо дат.. Если же .селектируемый импульс не совпадает по фазе с опорным импульсом то импульсы выделенных передних фронтов входных импульсов не совпадают между собой и на выходе элемента И 8 импульс не формируется, а триггеры устройства остаются в исходном состо1|ЫИИ. . На фиг. 2 представлены временные днаграм1Ф1 сигналов, где , i опорные и селектируемые импульсы соот ветственно, и,,,, Ц-а., U-j., Uizj- сигналы на первом и втором выходах Формирователей 1 я 2 соответственно Uj 4. Ug, Uj, D-f - сигналы на пряИых выходах триггеров 3-7 соответ-. ственно Ц, сигналы на выходах элементов И 12, 13 и 14 соответственно; и - сигнал на выходе элемента 17 задержки, t - ось времени. На графике , (фиг. 2) представлены четыре входных импульса, из них три первых совпадают по фазе с опорными импульсами и имеют длительность соответственно больше, равную и меньше, заданной, а четвертый имг пульс не совпадает по фазе с опорным На выходе триггера 3 повторяются по длительности и фазе те селектируе Ie импульсы из поступающих на вход 20, которые совпадают по фазе (по переднему фронту с опорными импульсами. Совпадение передних фронтов импуль сов на входах устройства фиксируется также и триггером 4, который переключается.в единичное состояние при пере ключении триггера 3, а возвращается в исходное состояние не сразу же по окончании селектируемого импульса, а по сигнсшам с элементов И 12- 14, которые управляют сбросом триггера 4 и формируют сигнал его сброса только после срабатывания одного из триггеров 6 или 7 и надежной регистрации селектируемого импульса 6 длительностью больше нижнего порога, тем предотвращаются о пасные состязания разрешающих сигналов на входах элемента И 9. Триггер 5 фиксирует начало заданного интервала- С достижение нижнего порога), его выходные сигналы подготавливают к срабатыванию элемент И 11 и тем самым разрешают формирование импульса на выходе триггера 7 по окончании сигнала выделенного заднего фронта опорного импульса при превышении Длительности селектируе мого импульса относительно заданной, а также закрывают элемент И 14 и тем самым предотвращают преждевременный сброс триггера 4 до регистрации селектируемого импульса од,ним из триггеров 6 или 7. Триггеры б и i формируют вьссодные импу.1г1ьсы устройства без выделения части ттулъсов или дробления, при срабатывании одного из этих триггеров на выход устройства поступает импульс, длительность которого может быть приближена к длительности входного и myльca выбором длительности задержки элемента 17, а фаза импульса на выходе триггера 7 стабильна и запаздывает относительно фазы входного импульса на заданный интервал. Формула изобретения Селектор импульсов по длительности и фазе, содержащий два формирователя импульсов, входы которых подключены соответственно к первому и второму входам устройства, первые выходы через первый элемент И соединены с первым входом первого триггера, а вторые выходы соответственно с первым и вторым входами второго элемента И, второй триггер, выход которого соединен с третьим входом второго элемента; И и с первым входом третьего элемента И, и элемент задержки , вход которого подключен к выхо- ., ДУ первого элемента ИЛИ, о т л и ч а ю ц и и с я тем, что, с целью расширения функциональных возможностей, введены трети: четвертый, и пя тый триггеры, четвертый, пятый шестой и седьмой элементы И, инвертор и второй элемент ИЛИ, первые входа третьего, четвертого и пятого триггеров соединены соответственно с выходами третьего, второго и четвертого элементов И, прямые выходы с первыми входами четвертого, пятого

и шестого элементов И соответственно, второй вход третьего триггера подключен к инверсному выходу второго триггера, Bioptie входы четвертого и пя того триггеров объединены и подключены к выходу элемента задержки, а инверсные выходы третьего и четвертого триггеров соединены соответственно с первым входом седьмогоэлемента И и с -Вторым входом четвертого элемента И, третий вход которого череэ инвертор соединен с первым входом второго элемента И н с втором входом третьего элемента И, вторые входы пятого, шестртчз и седьмого элементов И объединены и подключе.ны к инверсному выходу первого триггера, а duxo,ma соединены соответственно с первым и вторым входами первого элемента ИЛИ и с первым входом второго элемента ИЛИ, второй вход которого подключен к входу элемента задержки, а выход - к входу установкнулевого состояния второго триггера, второй вход и прямой выход первого триггера непосредственно соединены соответственно с вторым выходом второго формирователя импульсов и с ВХОДОМустановки единичного состояни второго триггера.

Источники ИНфорМЕЩИИ,

принятые во внимание при экспертизе 1. Авторское свидетельство СССР

566336, кл. Н 03 К 5/18, 1977. 2i Авторское свидетельство СССР

725218, кл. Н 03 К 5/18, 1989.

| название | год | авторы | номер документа |

|---|---|---|---|

| Селектор импульсов по длительности и фазе | 1981 |

|

SU972651A1 |

| Селектор импульсов по длительности | 1981 |

|

SU1001458A2 |

| Селектор импульсов по длительности | 1980 |

|

SU917331A2 |

| Селектор импульсов по длительности | 1979 |

|

SU805485A1 |

| Селектор импульсов | 1980 |

|

SU936415A1 |

| Селектор импульсов по длительности | 1983 |

|

SU1150746A1 |

| Селектор серий импульсов по дли-ТЕльНОСТи | 1979 |

|

SU813768A1 |

| Селектор импульсов | 1980 |

|

SU928631A1 |

| Селектор импульсов | 1981 |

|

SU993465A1 |

| Селектор импульсов по длительности | 1979 |

|

SU813744A1 |

г|

ш

IlITJ

и

JLJ

Авторы

Даты

1982-10-15—Публикация

1981-03-30—Подача