1

Изобретение относится к источникам вторичного электропитания и может быть использовано в качестве источника электропитания радиоэлектронной аппаратуры.

Известен стабилизатор напряжения с регулирующим транзистором и устройством для защиты от перегрузки по току и короткого замыкания на выходе стабилизатора, содержащий датчик тока, тиристор, резистивный делитель, диод и времязадающий конденсатор 1.

Однако в известном стабилизаторе обеспечивается помехозащищенность только от импульсов, длительность которых меньще времени срабатывания устройства.

Кроме того, известен стабилизатор напряжения, который обеспечивает высокую помехозащищенность 2.

Однако такое устройство имеет сложное схемное решение.

Наиболее близким к предлагаемому является стабилизатор, содержащий регулирующий транзистор, коллектор которого подключен к положительному входному выводу, блок управления, резистивный датчик тока, включенный между эмиттером регулирующего транзистора и положительным выходным

выводом, узел сравнения, вход которого подключен к датчику тока, времязадающую цепь и исполнительный орган защиты 3.

Недостатком указанного устройства является то, что не имеет защиты от помех, длительность импульсов которых соизмерима с длительностью импульсов тока нагрузки, а также от помех, амплитуда импульсов которых превыщает предельно допустимое значение.

Цель изобретения - обеспечение незави10симости уровня срабатывания защиты от формы импульсов тока нагрузки и устранение влияния помех на,работу стабилизатора.

Указанная цель достигается тем, что в стабилизаторе времязадающая цепь выполнена в виде двух каскадов на транзисто15рах п-р-п-тина, включенных по схеме с общим эмиттером, эмиттеры которых соединены с положительным выходным выводом, причем транзистор первого каскада соединен базой через резистор и диод с выходом узла

20 сравнения, а коллектором через диод и резистор - с базой транзистора второго каскада, коллектор которого подключен ко входу исполнительного органа защиты, при этом соединенные выводы указанных диодов

и резисторов через конденсаторы подключены к положительному выходному выводу.

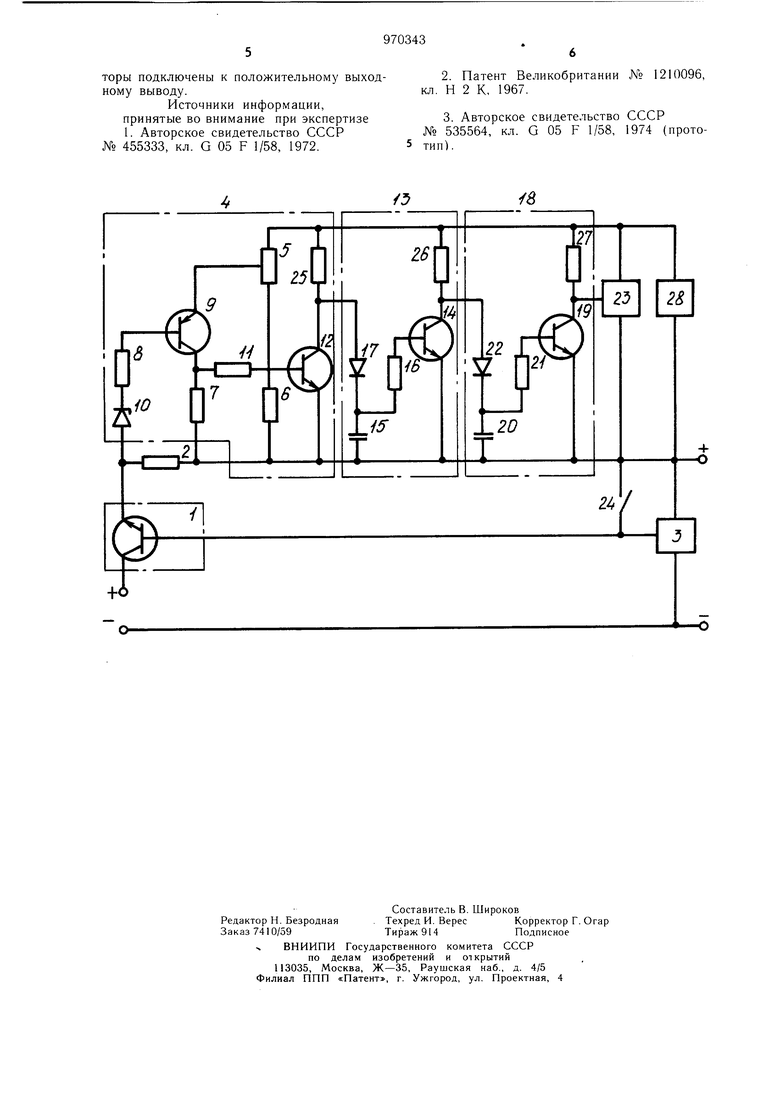

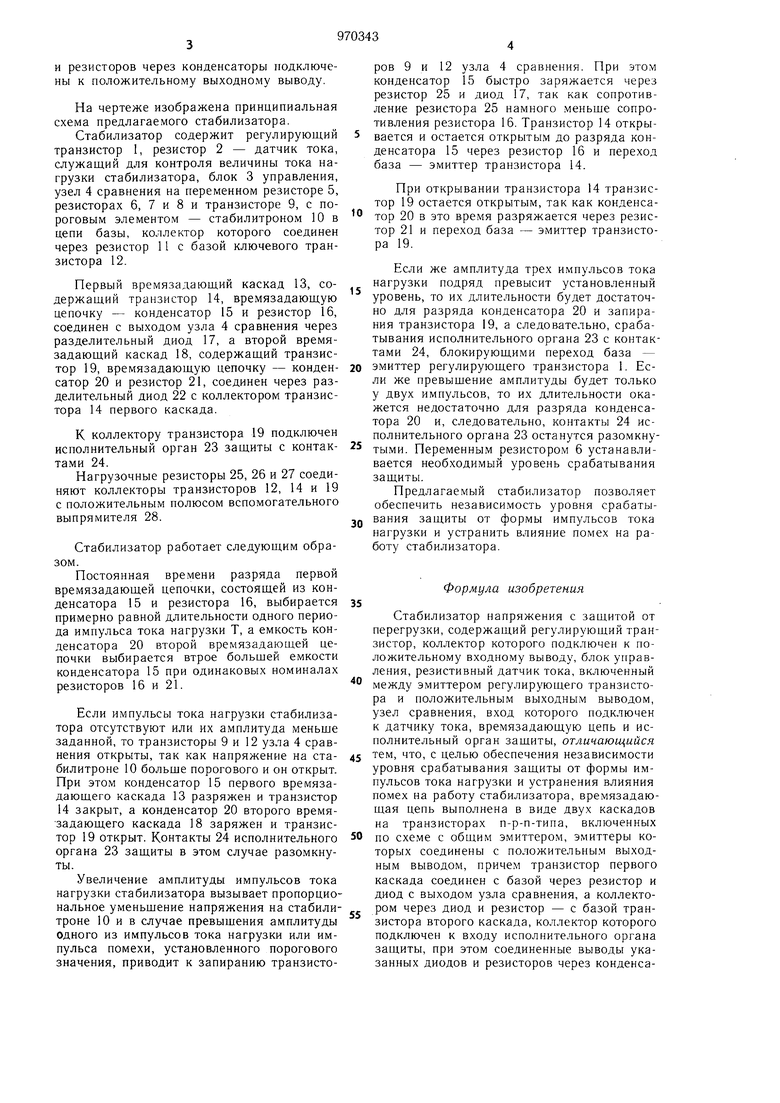

На чертеже изображена принципиальная схема предлагаемого стабилизатора.

Стабилизатор содержит регулирующий транзистор 1, резистор 2 - датчик тока, служащий для контроля величины тока нагрузки стабилизатора, блок 3 управления, узел 4 сравнения на переменном резисторе 5, резисторах 6, 7 и 8 и транзисторе 9, с пороговым элементом - стабилитроном 10 в цепи базы, коллектор которого соединен через резистор 11 с базой ключевого транзистора 12.

Первый времязадающий каскад 13, содержащий транзистор 14, времязадающую цепочку - конденсатор 15 и резистор 16, соединен с выходом узла 4 сравнения через разделительный диод 17, а второй времязадающий каскад 18, содержащий транзистор 19, времязадающую цепочку - конденсатор 20 и резистор 21, соединен через разделительный диод 22 с коллектором транзистора 14 первого каскада.

К коллектору транзистора 19 подключен исполнительный орган 23 защиты с контактами 24.

Нагрузочные резисторы 25, 26 и 27 соединяют коллекторы транзисторов 12, 14 и 19 с положительным полюсом вспомогательного выпрямителя 28.

Стабилизатор работает следующим образом.

Постоянная времени разряда первой времязадающей цепочки, состоящей из конденсатора 15 и резистора 16, выбирается примерно равной длительности одного периода импульса тока нагрузки Т, а емкость конденсатора 20 второй времязадающей цепочки выбирается втрое большей емкости конденсатора 15 при одинаковых номиналах резисторов 16 и 21.

Если импульсы тока нагрузки стабилизатора отсутствуют или их амплитуда меньше заданной, то транзисторы 9 и 12 узла 4 сравнения открыты, так как напряжение на стабилитроне 10 больще порогового и он открыт. При этом конденсатор 15 первого времязадающего каскада 13 разряжен и транзистор 14 закрыт, а конденсатор 20 второго времязадающего каскада 18 заряжен и транзистор 19 открыт. Контакты 24 исполнительного органа 23 защиты в этом случае разомкнуты.

Увеличение амплитуды импульсов тока нагрузки стабилизатора вызывает пропорциональное уменьщение напряжения на стабилитроне 10 и в случае превышения амплитуды одного из импульсов тока нагрузки или импульса помехи, установленного порогового значения, приводит к запиранию транзисторов 9 и 12 узла 4 сравнения. При этом конденсатор 15 быстро заряжается через резистор 25 и диод 17, так как сопротивление резистора 25 намного меньще сопротивления резистора 16. Транзистор 14 открывается и остается открытым до разряда конденсатора 15 через резистор 16 и переход база - эмиттер транзистора 14.

При открывании транзистора 14 транзистор 19 остается открытым, так как конденсатор 20 в это время разряжается через резистор 21 и переход база - эмиттер транзистора 19.

Если же амплитуда трех импульсов тока нагрузки подряд превысит установленный уровень, то их длительности будет достаточно для разряда конденсатора 20 и запирания транзистора 19, а следовательно, срабатывания исполнительного органа 23 с контактами 24, блокирующими переход база -

эмиттер регулирующего транзистора 1. Если же превыщение амплитуды будет только у двух импульсов, то их длительности окажется недостаточно для разряда конденсатора 20 и, следовательно, контакты 24 исполнительного органа 23 останутся разомкнутыми. Переменным резистором 6 устанавливается необ.ходимый уровень срабатывания защиты.

Предлагаемый стабилизатор позволяет обеспечить независимость уровня срабатывания защиты от формы импульсов тока нагрузки и устранить влияние помех на работу стабилизатора.

Формула изобретения

Стабилизатор напряжения с защитой от перегрузки, содержащий регулирующий транзистор, коллектор которого подключен к положительному входному выводу, блок управления, резистивный датчик тока, включенный между эмиттером регулирующего транзистора и положительным выходным выводом, узел сравнения, вход которого подключен к датчику тока, времязадающую цепь и исполнительный орган защиты, отличающийся

тем, что, с целью обеспечения независимости уровня срабатывания защиты от формы импульсов тока нагрузки и устранения влияния помех на работу стабилизатора, времязадающая цепь выполнена в виде двух каскадов на транзисторах п-р-п-типа, включенных

0 по схеме с общим эмиттером, эмиттеры которых соединены с положительным выходным выводом, причем транзистор первого каскада соединен с базой через резистор и диод с выходом узла сравнения, а коллектором через диод и резистор - с базой транзистора второго каскада, коллектор которого подключен к входу исполнительного органа защиты, при этом соединенные выводы указанных диодов и резисторов через конденсаторы подключены к положительному выходному выводу.

Источники информации, принятые во внимание при экспертизе I. Авторское свидетельство СССР № 455333, кл. G 05 F 1/58, 1972.

2.Патент Великобритании № 1210096, кл. Н 2 К, 1967.

3.Авторское свидетельство СССР

№ 535564, кл. G 05 F 1/58, 1974 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Стабилизатор постоянного напряжения | 1977 |

|

SU737935A1 |

| Устройство защиты источника питания | 1979 |

|

SU830362A1 |

| Стабилизатор постоянного напряжения с защитой от перегрузки | 1974 |

|

SU535564A1 |

| Импульсный источник питания с бестрансформаторным входом | 1986 |

|

SU1543392A1 |

| Стабилизатор постоянного напряжения | 1986 |

|

SU1372311A1 |

| Стабилизирующий источник электропитания | 1984 |

|

SU1179301A1 |

| Стабилизатор напряжения с самозащитой | 1982 |

|

SU1046751A1 |

| Стабилизированный источник питания | 1979 |

|

SU763870A1 |

| УСТРОЙСТВО ЗАЩИТНОГО ОТКЛЮЧЕНИЯ ЭЛЕКТРОТЕХНИЧЕСКИХ ПРИБОРОВ И АППАРАТОВ | 2007 |

|

RU2321125C1 |

| Реле времени | 1981 |

|

SU951455A1 |

Авторы

Даты

1982-10-30—Публикация

1980-07-15—Подача