(5«) ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ (ЕГО ВАРИАНТЫ)

| название | год | авторы | номер документа |

|---|---|---|---|

| Стабилизатор постоянного напряжения | 1983 |

|

SU1130842A2 |

| Формирователь управляющих импульсов | 1990 |

|

SU1714767A1 |

| Формирователь импульсов | 1977 |

|

SU702499A1 |

| БИПОЛЯРНЫЙ КЛЮЧЕВОЙ КАСКАД | 2013 |

|

RU2524679C1 |

| ТРАНЗИСТОРНЫЙ КЛЮЧ (ВАРИАНТЫ) | 1994 |

|

RU2076441C1 |

| Устройство для токовой защиты мощного транзистора | 1990 |

|

SU1725321A1 |

| УСТРОЙСТВО СОПРЯЖЕНИЯ ДВУХПРОВОДНОГО И ЧЕТЫРЕХПРОВОДНОГО ТРАКТОВ | 2001 |

|

RU2195073C1 |

| Высоковольтный электронный ключ | 2024 |

|

RU2837267C1 |

| Высоковольтный электронный ключ | 2022 |

|

RU2780816C1 |

| Коммутатор импульсных сигналов | 1980 |

|

SU940302A1 |

1

Изобретение относится к импульсной технике, в частности - к устройствам формирования импульсов наносекундного диапазона с большим током и напряжением, и может быть ис пользовано в узлах электронновычислительных машин в качестве интегрального быстродействующего формирователя импульсного тока для управления

магнитными запоминающими устройствами импульсами тока 0,1-1,0 А напряжением В.

Известно устройство для формирования больших импульсных токов, содержащее входной, фазоразделительный и выходной каскады набиполярных транзисторах, подключенного к общему источнику питания, причем.в качестве эмиттерной нагрузки транзистора фазоразделительного каскада использована катушка индуктивности, и связи с чем (схема формирует выходной ток только в момент переключения входного напряжения от низкого к высокому уровню си.

Однако в данном устройстве длительность йыходного токового импульса определяется не длительностью входного управляющего импульса, а параметрами катушки индуктивности. Недостатками устройства являются также значительное потребление мощности от источника питания, так как фазоразделительный каскад потребляет от источника питания мощность в течение всего времени, пока его транзистор находится во включенном состоянии и ограниченные функциональные возможности, в частности устройство не позволяет получать выходные импульсы повышенного напряжения и мощности при управлении от стандартных 20 низковольтных схем (например - ТТЛ схем).

Наиболее близким техническим реиением к предлагаемому является фор. мирователь импульсов, содержащий

входной, фазоразделительный и выходной каскады на транзисторах. Входной каскад содержит логическую схему и подключен к низковольтному источнику питания для маломощных цепей, а фазоразделительный каскад имеет прямой и инвертирующий выходы, оодсоединенные ко входам выходного каскада, и подключен к высоковольтному источнику питания для мощных цепей. Выходно каскад содержит ключ с мощным выходным транзистором, а также первый и второй предвыходные транзисторы и подсоединен к отдельному либо общему с фазоразделительным каскадом высоковольтному источнику питания для мощных цепей.

Недостатком этого формирователя является значительное потребление мощности от высоковольтного источника питания, которую потребляет в ждущем режиме фазоразделительный каскад формирователя. Кроме того, устройству присущи ограниченные функциональные возможности, связанные с однонаправленностью формируемого тока. Цель изобретения - уменьшение потребляемой мощности и расширение функциональных возможностей за счет формирования как втекающего, так и вытекающего токов.

Указанная цель достигается согласно 1-ому варианту за счет того, что в формирователе импульсов, содержащем входной, фазоразделительный и выходной каскады, входной каскад подключен к источнику питания для маломощных цепей, а выходной - к источнику питания для цепей, выходной каскад выполнен на первом, втором и третьем транзисторах, фазоразделительный каскад подключен к источнику питания для маломощных цеПей, причем между фазоразделительным и выходным каскадами введен каскад коммутатора, содержащий то козадающий полевой транзистор, сток которого соединен с базой первого транзистора выходного каскада и коллектором первого транзистора коммутатора, эмиТтер которого соединен с. общей шиной, затвор токозадающего полевого транзистора через параллельно соединенные резистор и первый стабилитрон подключен к источнику питания для мощных цепей, непосредственно соединен с коллектором второго транзистора коммутатора, исток токозадающего полевого транзистора

через второй стабилитрон- подключен к источнику питания для мощных цепей, при этом фазоразделительный каскад выполнен по схеме с тремя дополнительными транзисторными ключами, входы .которых включены в неинвертирующую цепь фазоразделительного каскада, причем выход первого дополнительного ключа через токоограничивающий резистор подсоединен к эмиттеру второго транзистора коммутатора выход второго дополнительного ключа подсоединен к базе первого транзистора коммутатора, выход третьего дополнительного ключа подсоединен к базе второго транзистора выходного каскада .

Согласно второму варианту указанная цель достигается за счет того, что фазоразделительный каскад подключен к источнику питания для маломощных цепей, между фазоразделительным и выходным каскадами введен каскад коммутатора, содержащий первый, второй и токозадающий транзисторы, где эмиттер токозадающего транзистора соединен с базой первого транзистора выходного каскада и коллектором первого транзистора коммутатора, эмиттер которого соединен с общей шиной, база токозадающего транзистора через резистор подключена к его коллектору и непосредственно соединена с коллектором второго транзистора коммутатора, эмиттер которого соединен с общей/шиной, коллектор токозадающего транзистора через резистор подключен к источнику питания для мощных цепей, при этом фазоразделительный каскад выполнен по схеме с тремя дополнительными транзисторными ключами, входы которых включены в неинвертирующую цепь фазоразделительного каскада, причем выход первого дополнительного ключа подсоединен к базе Второго транзистора коммутатора, выход второго дополнительного ключа подсоединен к базе первого транзистора коммутатора, выход третьего дополнительного ключа подсоединен к базе второго транзистора выходного каскада.

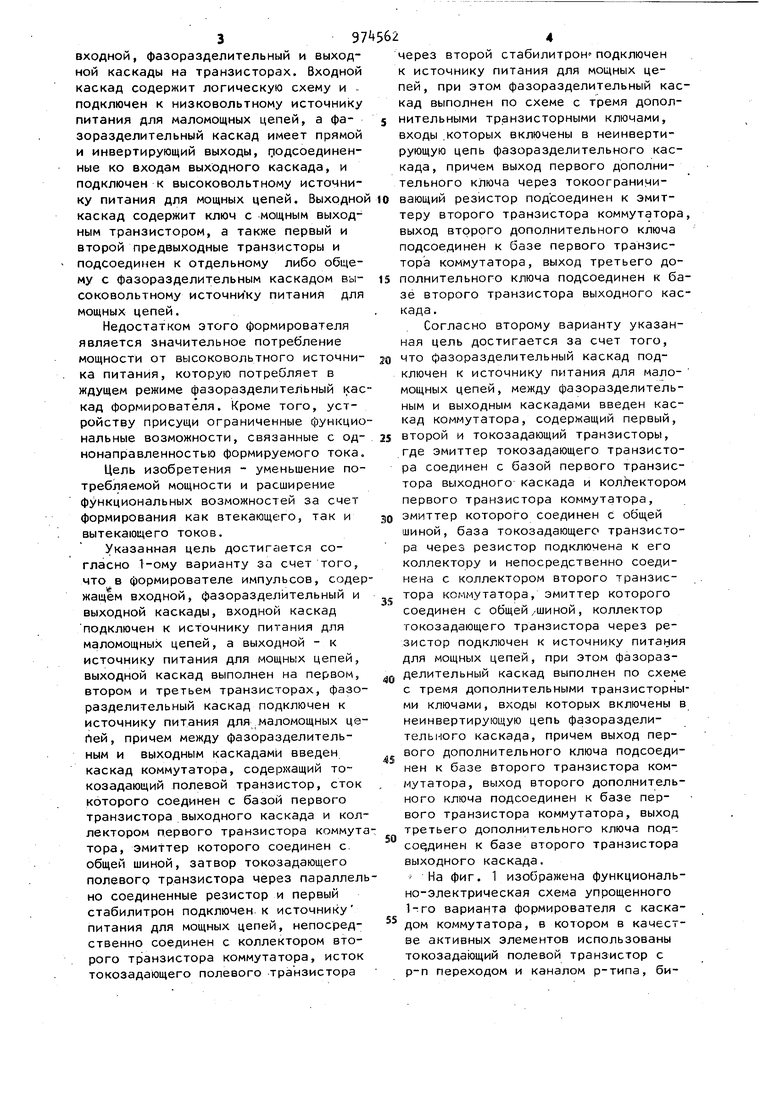

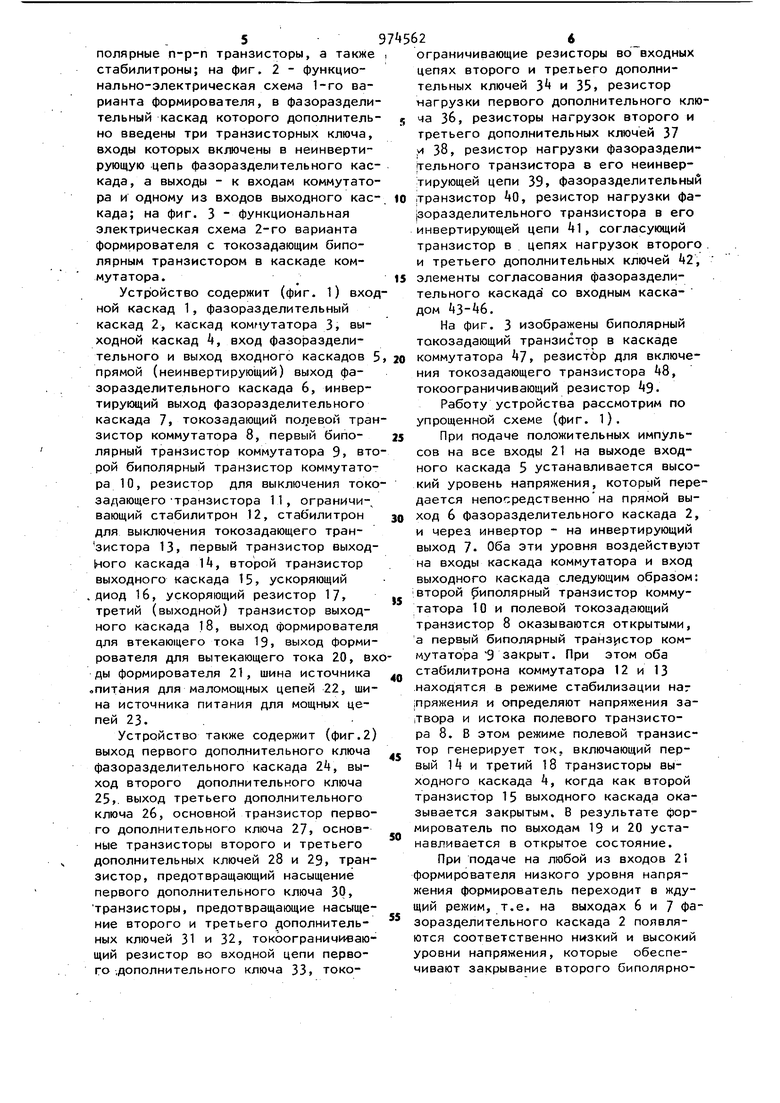

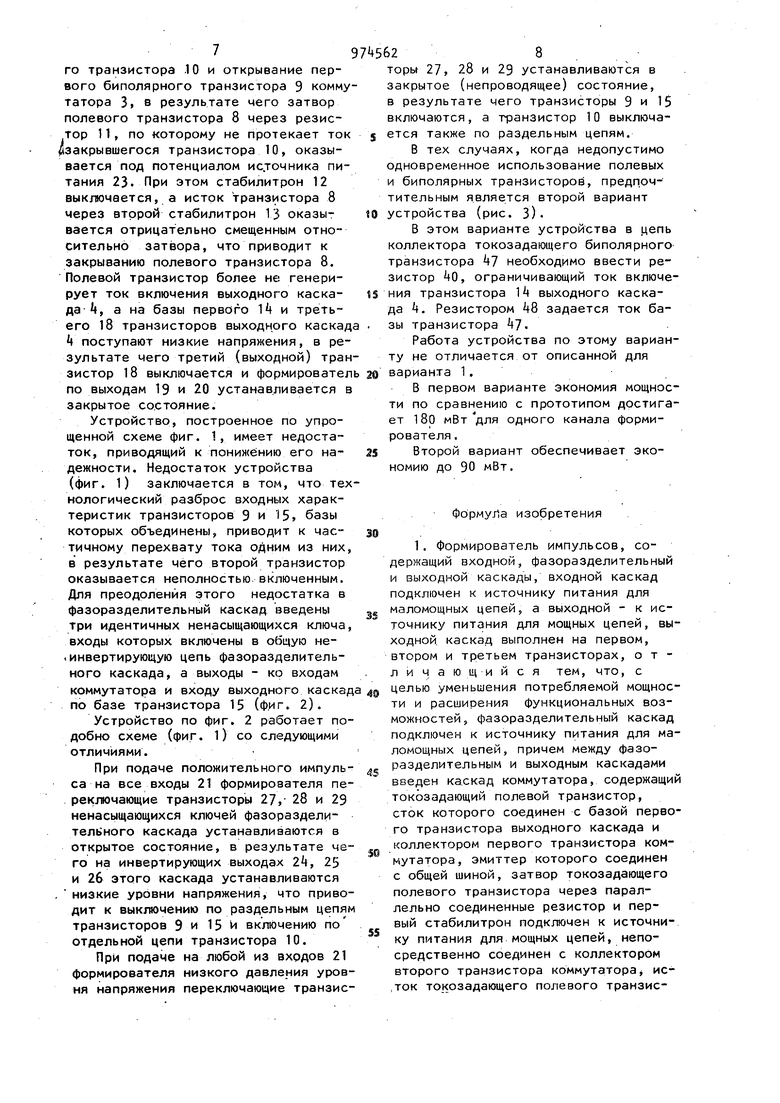

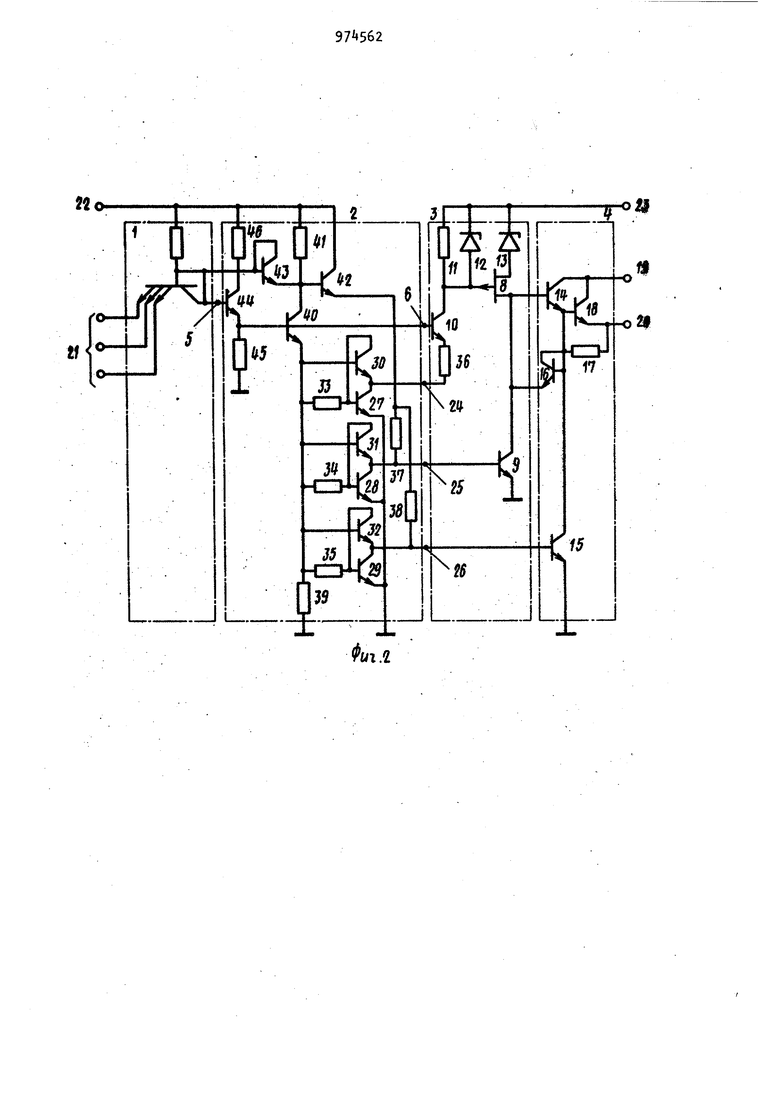

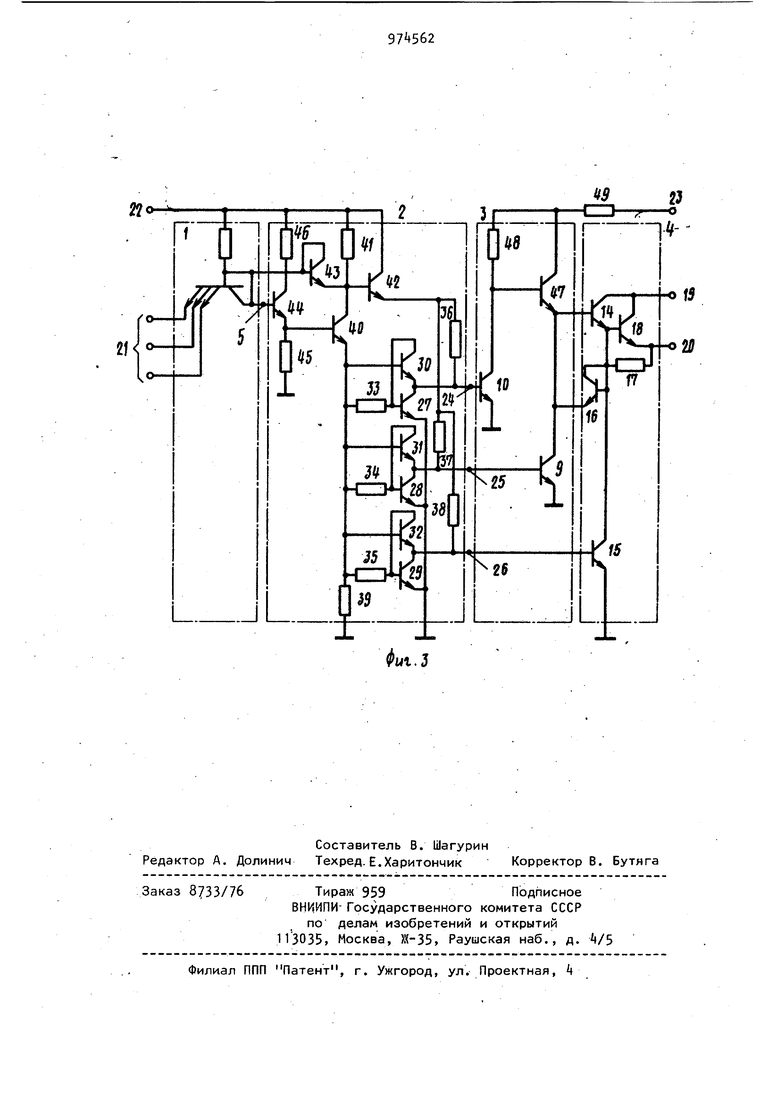

На фиг. 1 изображена функционально-электрическая схема упрощенного 1-го варианта формирователя с каскадом коммутатора, в котором в качестве активных элементов использованы токозадающий полевой транзистор с р-п переходом и каналом р-типа, биполярные n-p-n транзисторы, а также стабилитроны; на фиг. 2 - функционально-электрическая схема 1-го варианта формирователя, в фазоразделительный каскад которого дополнительно введены три транзисторных ключа, входы которых включены в неинвертирующую цепь фазоразделительного каскада, а выходы - к входам коммутатора и одному из входов выходного каскада; на фиг. 3 функциональная электрическая схема 2-го варианта формирователя с токозадающим биполярным транзистором в каскаде коммутатора. Устройство содержит (фиг. 1) входной каскад 1, фааоразделительный каскад 2, каскад коммутатора 3, выходной каскад k, вход фазоразделительного и выход входного каскадов 5, зо прямой (неинвертирующий) выход фазоразделительного каскада 6, инвертирующий выход фазоразделительного каскада 7, токозадающий тра зистор коммутатора 8, первый биполярный транзистор коммутатора 9, вт рой биполярный транзистор коммутато ра 10, резистор для выключения ток задающего -транзистора 11, ограничи-, вающий стабилитрон 12, стабилитрон для выключения токозадающего транзистора 13, первый транзистор выход ного каскада 1, второй транзистор выходного каскада 15, ускоряющий .диод 16, ускоряющий резистор 17, третий (выходной) транзистор выходного каскада 18, выход формирователя цля втекающего тока 19, выход формирователя для вытекающего тока 20, вх ды формирователя 21, шина источника «питания для маломощных цепей 22, шина источника питания для мощных цепей 23. . Устройство также содержит (фиг.2 выход первого дополнительного ключа фазоразделительного каскада 2k, выход второго дополнительного ключа 25,. выход третьего дополнительного ключа 2б, основной транзистор первого дополнительного ключа 27, основные транзисторы второго и третьего дополнительных ключей 28 и 29, транзистор, предотвращающий насыщение первого дополнительного ключа 3Q, транзисторы, предотвращающие насыщение второго и третьего дополнительных ключей 31 и 32, токоограничиеающий резистор во входной цепи первого .дополнительного ключа 33, токо15ограничивающие резисторы во входных цепях второго и третьего дополнительных ключей 3 и 35 резистор нагрузки первого дополнительного ключа 36, резисторы нагрузок второго и третьего дополнительных ключей 37 ,ч 38, резистор нагрузки фазораздели тельного транзистора s его неинвертирующей цепи 39, фазоразделительный транзистор tO, резистор нагрузки фа|зоразделительного транзистора в его инвертирующей цепи k , согласующий транзистор в цепях нагрузок второго и третьего дополнительных ключей 42, элементы согласования фазоразделительного каскада со входным каскадом . На фиг. 3 изображены биполярный токозадающий транзистор в каскаде коммутатора k7, резистбр для включения токозадающего транзистора jS, токоограничивающий резистор 9Работу устройства рассмотрим по упрощенной схеме (фиг. 1). При подаче положительных импульсов на все входы 21 на выходе входного каскада 5 устанавливается высокий уровень напряжения, который передается непосредственнона прямой выход 6 фазоразделительного каскада 2, и через инвертор - на инвертирующий выход 7. Оба эти уровня воздействуют на входы каскада коммутатора и вход выходного каскада следующим образом: Второй биполярный транзистор коммутатора 10 и полевой токозадающий транзистор 8 оказываются открытыми, а первый биполярный транзистор коммутатора 9 закрыт. При этом оба стабилитрона коммутатора 12 и 13 .находятся в режиме стабилизации наг лряжения и определяют напряжения заiTBOpa и истока полевого транзистора 8. В этом режиме полевой транзистор генерирует ток. включающий первый 1 и третий 18 транзисторы выходного каскада 4, когда как второй транзистор 15 выходного каскада оказывается закрытым. В результате формирователь по выходам 19 и 20 устанавливается в открытое состояние. При подаче на любой из входов 21 формирователя низкого уровня напряжения формирователь переходит в ждущий режим, т.е. на выходах 6 и 7 фазоразделительного каскада 2 появляются соответственно низкий и высокий уровни напряжения, которые обеспечивают закрывание второго биполярного транзистора .10 и открывание первого биполярного транзистора 9 комму татора 3, в результате чего затвор полевого транзистора 8 через резистор 11, по которому не протекает ток закрывшегося транзистора 10, оказывается под потенциалом источника питания 23. При этом стабилитрон 12 выключается, а исток транзистора 8 через второй стабилитрон 13 оказывается отрицательно смещенным относительно затвора, что приводит к закрыванию полевого транзистора 8. Полевой транзистор более не генерирует ток включения выходного каскада i, а на базы первого Tt и третьего 18 транзисторов выходного каскад k поступают низкие напряжения, в результате чего третий (выходной) тран зистор 18 выключается и формировател по выходам 19 и 20 устанавливается в закрытое состояние. Устройство, построенное по упрощенной схеме фиг. 1, имеет недостаток, приводящий к понижению его надежности. Недостаток устройства (фиг. 1) заключается в том, что тех нологический разброс входных характеристик транзисторов 9 и 15, базы которых объединены, приводит к частичному перехвату тока одним из них, в результате чего второй транзистор оказывается неполностью, включенным. Для преодоления этого недостатка в фазоразделительный каскад введены три идентичных ненасыщающихся ключа, входы которых включены в общую не.инвертирующую цепь фазоразделительного каскада, а выходы - ко входам коммутатора и входу выходного каскад по базе транзистора 15 (ф.иг. 2). Устройство по фиг. 2 работает подобно схеме (фиг. 1) со следующими отличиями. При подаче положительного импульса на все входы 21 формирователя переклочающие транзисторы 27,- 28 и 29 ненасыщающихся ключей фазораздели каскада устанавливаются в открытое состояние, в результате чего на инвертирующих выходах 2, 25 и 26 этого каскада устанав.пиваются низкие уровни напряжения, что приводит к выключению по раздельным цепям транзисторов 9 и 15 И включению по отдельной цепи транзистора 10. При подаче на любой из входов 21 формирователя низкого давления уровня напряжения переключающие транзисторы 27, 28 и 29 устанавливаются в закрытое (непроводящее) состояние, в результате чего транзисторы 9 и 15 включаются, а транзистор 10 выключается также по раздельным цепям. В тех случаях, когда недопустимо одновременное использование полевых и биполярных транзисторов, предпочтительным является второй вариант устройства (рис. 3). В этом варианте устройства в цепь коллектора токозадающего биполярного транзистора kj необходимо ввести резистор 40, ограничивающий ток включения транзистора 1 выходного каскада k. Резистором 48 задается ток базы транзистора 7. Работа устройства по этому варианту не отличается от описанной для варианта 1. В первом варианте экономия мощности по сравнению с прототипом достигает 18р мВт для одного канала формирователя . Второй вариант обеспечивает экономию до 90 мВт. Фбрмуг)а изобретения 1. Формирователь импульсов, содержащий входной, фазоразделительный и выходной каскады, входной каскад подключен к источнику питания для маломощных цепей, а выходной - к источнику питания для мощных цепей, ходной. каскад выполнен на первом, втором и третьем транзисторах, отличающийся тем, что, с Целью уменьшения потребляемой мощности и расширения функциональных возможностей, фазоразделительный каскад подключен к источнику питания для маломощных цепей, причем между фазоразделительным и выходным каскадами введен каскад коммутатора, содержащий токозадающий полевой транзистор, сток которого соединен с базой первого транзистора выходного каскада и коллектором первого транзистора коммутатора, эмиттер которого соединен с общей шиной, затвор токозадающего полевого транзистора через параллельно соединенные резистор и первый стабилитрон подключен к источнику питания для мощных цепей, непосредственно соединен с коллектором второго транзистора коммутатораj ис,ток токозадающего полевого транзистора через второй стабилитрон под,ключей к источнику питания для мощ;ных цепей, при этом фазоразделитель ный каскад выполнен по схеме с тремя дополнительными транзисторными ключами, входы которых включены в неинвертирующую цепь фазоразделительного каскада, причем выход первого дополнительного ключа через то коограничивающий резистор подсоединен к эмиттеру второго транзистора коммутатора, выход второго дополни тельного ключа подсоединен к базе первого транзистора коммутатора, вы ход третьего дополнительного ключа подсоединен к базе второго транзисто ра выходного каскада. 2. Формирователь импульсов, содер жащий входной, фазоразделительный и выходной каскады, входной каскад под ключен к источнику питания для маломощных цепей, а выходной - к источни ку питания для мощных цепей, выходной каскад выполнен на первом, втором и третьем транзисторах, о т л и уменьшения потребляемой мощности и расширения функциональных возможностей, фазоразделительный,каскад подключен к источнику питания для маломощных цепей, причем между фазоразделительным и выходным каскадом введен каскад коммутатора, содержащий первый, второй и токозадающий J- j,j транзисторы, где эмиттер токозадающего транзистора соединен с базой «первого транзистора выходного каскада и коллектором первого транзистора коммутатора, эмиттер которого соединен с общей шиной, база токозадающего транзи стора через резистор подключена к его коллектору и -непосредственно соединена ic коллектором второго транзистора коммутатора, эмиттер которого соединен с общей шиной, коллектор токозадающего транзистора через резистор подключен к источнику питания для мощных цепей, при этом фазоразделительный каскад выполнен по схеме с тремя дополнительными транзисторными ключами, входы которых включены 8 неинвертирующую цепь фазоразделительного каскада, причем выход первого дополнительного ключа . подсоединен к базе второго транзистора коммутатора, выход второго дополнительного ключа подсоединен к базе первого транзистора коммутатора, выход третьего дополнительного ключа подсоединен к базе второго транзистора выходного каскада. Источники информации, принятые во внимание при экспертизе 1.Патент США W 3959671, кл. 307-270, 197. 2.Texas instruments, 1973, р.б38640.(каталог) (прототип). о. .|,

#wi.3 P

Авторы

Даты

1982-11-15—Публикация

1980-12-22—Подача