(Sk) ДИФФЕРЕНЦИРУЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Дифференцирующее устройство | 1980 |

|

SU888141A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПЕРИОДИЧЕСКОГО СИГНАЛА В ЧАСТОТУ И ПЕРИОД | 2012 |

|

RU2520409C2 |

| ФАЗОСДВИГАЮЩЕЕ УСТРОЙСТВО | 2006 |

|

RU2320071C1 |

| Устройство для измерения амплитуды импульсных усилий | 1986 |

|

SU1352254A1 |

| ЦИФРОВОЙ ИЗМЕРИТЕЛЬ КРИТЕРИЯ ВОСПЛАМЕНЯЮЩЕЙ СПОСОБНОСТИ ИСКРОВЫХ РАЗРЯДОВ В СВЕЧАХ ЗАЖИГАНИЯ | 2000 |

|

RU2182336C2 |

| УСТРОЙСТВО ДЛЯ ИССЛЕДОВАНИЯ АГРЕГАЦИОННЫХ СВОЙСТВ БИОЛОГИЧЕСКИХ ОБЪЕКТОВ | 1990 |

|

RU2006032C1 |

| Устройство для управления вентильным преобразователем | 1991 |

|

SU1774446A1 |

| Устройство для управления @ -пульсным вентильным преобразователем | 1984 |

|

SU1246289A1 |

| ФАЗОСДВИГАЮЩЕЕ УСТРОЙСТВО | 2008 |

|

RU2373624C1 |

| Демодулятор сигналов с фазово-импульсной модуляцией | 1989 |

|

SU1621161A2 |

1

Изобретение относится к аналоговой вычислительной технике.

Известно дифференцирующее устрой ство, в котором производная определяется разностью интегральных значений сигнала, взятых на соседних интервалах времени, содержащее преобразователь входного напряжения в частоту, реверсивный счетчик, управляемый от .задатчика калиброванных промежутков времени, и ключ 1 .

Недостатком устройства является сложность сопряжения с аналоговыми источниками информации и потребителями, а также незащищенность от периодических помех, если их период не совпадает с интервалом времени между реверсами счетчика..

Наиболее близким по технической сущности к предлагаемому является дифференцирующее устройство,.в котором интервал интегрирования подстраивается под период помехи, наложенной, на входной- сигнал,, благодаря

чему влияние помехи на интегральное значение сигнала исключается. Это осуществляется применением специального формирователя, выявляющего в результате обработки входного сигнала периодическую помеху. Масштаб производной не изменяется при изменении интepвaJ a интегрирования за счет включения;на входе устройства управляемого усилителя, связанного с форtoмирователем 2.

Недостатком устройства является невысокая динамическая точность, что обусловлено запаздыванием в получении производной и значительным искажением

IS формы выходного сигнала при вычислении производной от сигнала, частота которого близка к частоте помехи.

Цель изобретения - повышение,динамической точности.

20

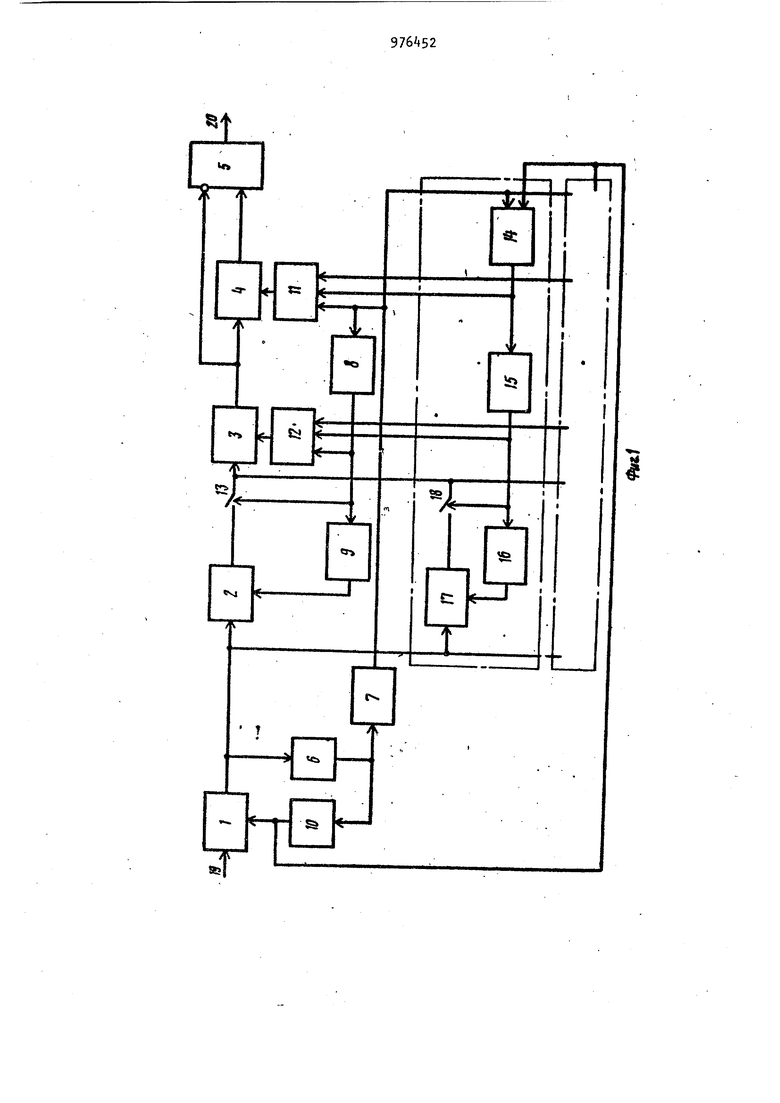

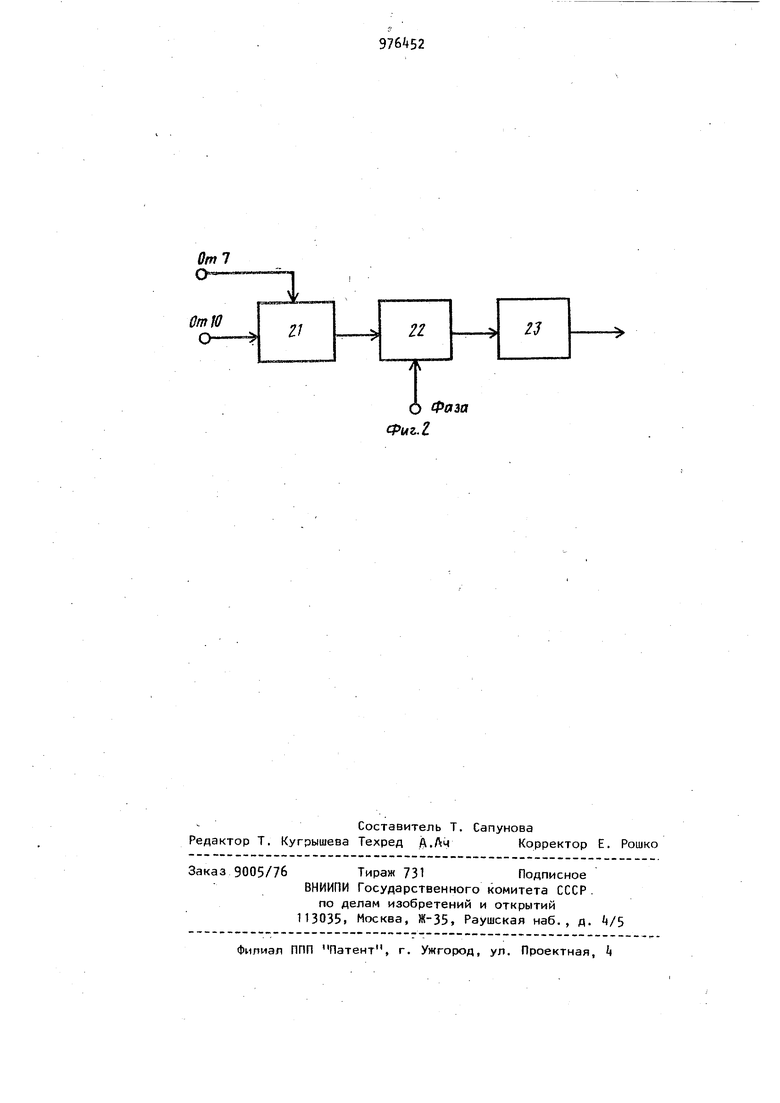

Цель достигается тем, что дифференцирующее устройство, содержащее усилитель с управляемым коэффициентом передачи, вход которого является входом устройства, а выход подключен к входу интегратора и формиг рователя импульсов опорной частоты, первый запоминающий элемент, информационный вход которого через ключ связан с выходом интегратора, а выход соединен с информационным входом запоминающего элемента, выходы первого и второго запоминающих элемен.тов соединены с соответствующими вхо дами блока вычитания, выход формирователя импульсов опорной частоты через прербразоватеда частота-напряжение связан с управляющим в) усилителя с управляемым коэффициентом передачи и через одновибратор с входом первого элемента задержки, выход которого соединен с управляющим входом ключа и через второй элемент задержки - с входом сброса интегратора содержит два элемента ИЛИ, а также п каналов, каждый из которых содержит ключ, два элемента задержки, интегратор и фазосдвигающий блок, при этом вход интегратора каждого канала соединен с выходом усилителя с управляемым коэффициентом передачи, первый вход фазосдвигаюЩего блока подключен к выходу одновибратора, второй вход фазосдвигающего блока подключен к выходу преобразователя частота-напряжение, выход фазовдвигающего блoкaf в каждом канале соединен с входом первого элемента задержки этого канала и с соответствую щими входом первого элемента ИЛИ, выход первого элемента задержки канала соединен с соответствующим входом второго элемента ИЛИ, с входом второго элемента задержки канала и с управляющим входом ключа, выход второго элемента задержки канала сое динен с входом сброса интегратора того же канала, выход которого через ключ соединен с входом первого запоминающего элемента, выход одновибратора соединен с соответствующим входом первого элемента ИЛИ, выход которого соединен с управляющим второго запоминающего элемента, 8Ы)(од первого элемента задержки соединен, с соответствующим входом второго элемента ИЛИ, выход которого соединен с управляющим входом первого запоминающего элемента. Фазосдвигающий блок содержит интегратор, компаратор yi одновибратор, при этом вход сброса интегратора является первым входом блока,информацио ный вход интегратора является вторым входом блока, выход интегратора соединен с первым входом KOMnapaToiaa, второй вход которого подключен к шине задания фазы,а выход компаратора соединен с входом одновибратора, выход кЪ торого является выходом блока. На фиг. 1 представлена схема устройства; на фиг. 2 - схема фазосдвигающего блока. Устройство Содержит управляемый усилитель 1,интегратор 2, запоминающие элементы 3 и , блок 5 вычитания, формирователь 6 импульсов опорной частоты, одновибратор 7, элементы 8 и 9 задержки, преобразователь 10 частота-напряжение, элементы ИЛИ 11 и 12, ключ 13, дополнительный фазосдвигающий блок Н, дополнительные элементы 15 и 16 задержки дополнительный интегратор 17, Дополнительный ключ 18 (rta чертеже раскрыт один из П дополнительных каналов). Позициями 19 и 20 обозначены соответственно вход и выход устройства. Фазосдвигающий блок 1 содержит интегратор 21, компаратор 22, одновибратор 23. Устройство работает следующим образом. На вход управляемого усилителя 1 поступает напряжение, котррое масштабируется соответственно периоду помехи Т.(период помехи выявляется с помощью формирователя 6, частота импульсов на его выходе определяет коэффициент передачи управляемого усилителя 1) . Масштабированный сигнал периодически интегрируется интеграторами 2,17,.., в течение интервала Т, причем интервалы интегрирования сдвинуты по фазе относительно импульсов .опорной частоты на величину i где i - порядковый номер интегратора, i 0,1,..., п (нулевой номер относится к интегратору 2), ап - число дополнительных интеграторов. Перед сбросом каждого интегратора производится фиксация значения интегратора в запоминающем элементе 3. Для этого на аналоговые ключи 13,18.-.., подаются управляющие импульсы с элементов 8,15..., задержки соответственно, а на запоминающий элемент 3 подается управляющий импульс с элемента ИЛИ 12, что обеспечивает считывание и запоминание информации о конечном значении интеграла поочередно со всех интегоаторов. Перед з писью информации в запоминающий эле мент 3 происходит фиксация информации о предыдущем значейии интеграла в запоминающем элементе k, что обес печивается управляющим импульсом, п ступающим с элемента ИЛИ 13. Таким о15разом, на выходе блока 5 вычитани получается сигнал, соответствующий приращению напряжения. Частота обно ления приращения увеличивается в П+1, раз, за счет чего увеличивается динамическая точность устройства, однако помехоустойчивость устройств не уменьшается, так как период инте рирования каждого интегратора остае ся равным периоду основной помехи. фазосдвигающий блок 14, определяю щий сдвиг на фазе интервала работы интегратора 17, работает следующим образом,. Линейно возрастающее напряжение, поступающее с интегратора 21, сравнивается в компараторе 22 с заданным уровнем. В момент равенства одновибратор 23 вырабатывает нормированный по длительности импульс. Его фаза оп рёделяется величиной заданного уров;ня и не изменяется при изменении периода помехи благодаря соответствующему изменению масштаба напряжения, поступающего на интегратор 21 с преобразователя 10. Технико-экономический эффект от использования изобретения определяет ся повышением динамической точности дифференцирования при сохранении с:глаживающих свойств..Формула изобретения iДиффepeнциpyющee устройство, содержащее усилитель с управляемым коэффициентом передачи, вход которого является входом устройства, а выход подключен к входу интегратора и формирователя импульсов опорной частоты, первый запоминающий элемент информационный вход которого через ключ связан с выходом интегратора, а .выход соединен с информационным входом второго запоминающего элемента, выходы первого и второго запо минающих элементов соединены с соот ветствующими входами блока вычитания, выход формирователя импульсов опорной частоты через преобразователь частота-напряжение связан с управляющим входом усилителя с управляемым коэффициентом передачи и через одновибратор с входом первого элемента задержки, выход которого соединен с управляющим входом ключа и через второй элемент задержки - с входом сброса интегратора, отличающееся тем, что, с-целью , повышения динамической точности, устройство содержит два элемента ИЛИ, а также /V каналов, каждый из которых содержит ключ, два элемента задержки, интегратор и фазосдвигающий блок, при этом вход интегратора каждого канала соединен с выходом усилителя с управляемым коэффициентом передачи, первый вход фазосдвигающего блока подключен к выходу одновибратора, второй вход фазосдвигающего блока подключен к выходу преобразователя частота-напряжение, выход фазосдвигающего блока в каждом канале соединен с входом первого элемента задержки канала и с соответствующим входом первого элемента ИЛИ, выход первого элемента задержки канала соединен с соответствующим входом второго элемента ИЛИ, с входом второго элемента . задержки канала и с управляющим входом ключа, выход второго элемента задержки канала соединен с входом сброса интегратора же канала, йыхрд которого через ключ соединен с ВХОДОМ первого запоминающего элемента, выход одновибратора соединен с соответствующим входом первого элемента ИЛИ, выход которого соединен с управляющим входом второго запоминающего элемента, выход первого элемента задержки соединен с соответствующим входом второго элемента ИЛИ ыход которого соединен с управляющим входом первого запоминающего элемента. 2. Устройство по п, 1, о т л и ч а ю щ е е ся тем, .что фазосдвигающий блок содержит интегратор, компаратор и одновибратор, при этом вход сброса интегратора является первым входом блока, информационный .вход интегратора является вторым входом блока, выход интегратора соединен с v первым входом компаратора, второй вход которого подключен к шине задания фазы, а выход компаратора соеди нен с входом одновибратора, выход которого является выходом блока.

7976 528

.Источники информации,2. Авторское свидетельство СССР

принятые во внимание при экспертизе по заявке № 2883283/18-2,

1, Авторское свидетельство СССР кл. G Об G 7/18, 1980 (прото№ 35П59; кл. G 01 Р 15/00, 1969. тип).

I

Фаза

сриг.1

Авторы

Даты

1982-11-23—Публикация

1981-05-13—Подача