Изобретение относится к автоматике и вычислительной технике и может быть использовано для автоматического конт роля работоспособности электронных устройств систем автоматики, регулирования и управления, в частности для определения отказов в устройствах со ступен чатым иаменением выходного сигнала. Известно устройство дай контроля цифровых схем, содержащее задатчик тес тов, блок сравнения, блок ввода -Ч Недостатком данного устройства является ограниченная область применения вследствии невозможности контроля цифроаналоговых преобразователей. Наиболее близким техническим решением к изобретению .является устройство для контроля радиоэлектронных блоков, содержащее компаратор, дифференциатор, индикатор 2 j . Недостатком данного устройства является низкая точность контроля вследствие того, что его абсолютная погрешКОСТЬ определяется величиной стуненьвая, выходного напряжения генератора эталоЕ&-кого ступенчатого напряжения. Цель изобретения - повьппение точности контроля. Поставленная цель.достигается тем, что в устройст для автоматического контроля цифроаналогового преобразоватеАя, содержащее дифференгшатор, компаратор и индикатор введены формирователь импульсов, логический блок и элемент ИЛИ, соединенный выходом со взюдом ин- дикатора, первым входом через компаратор - с выходом дифференциатора и с входом формирователя импульсов, соединенного выходом с первым входом логического блока, вь1зсод которого подключен к второму входу элемента ИЛИ, второй вход - к входу контролируемого преобразователя, соединенного выходом с входам дифференциатора. Причем логический блок содержит элемент ИЛИ-НЕ, элемент ИЛИ ИСКЛЮЧИТЕЛЬНОЕ; первый и второй одновибратрьг, .первый и второй элементы ИЛИ, перBbrii и второй элементы И, триггер, сое динешгый S -входом с выходом элемен.та ИЛИ-11Е, прямым выходом с первым входом первого элемехста ИЛИ, соединенного B.ropbLM входом с вторым входом логическог-о блока, входом первого одновибраторЯз первым входом элемента и первьм входом элемента Р1ЛИ ИСКЛЮЧИТЕЛЬНО.Е, соединенного выхо.--. дом с выходом логиг1ес.кого блока, вторым входом - с выходом первого элемента И, соединенного непосредственно пер™ вьш входом .с вторым входом эпемента ИЛИ-Н.Е, а через второй однови6рг.тор с выходом второго эиеиента И, соедгшен-, него iiepBbtvi входом с выходом первого элемента И.;1И и вторым входом первого элемеггта И, вторым вяодо.м « с выходом второго элсяугента ИЛИ, первый вход ко-торого подключен к вьгхо..цу первого однО вибратора ц R -входу триггера, второй вход - к первогл-гу вхощ- логического,

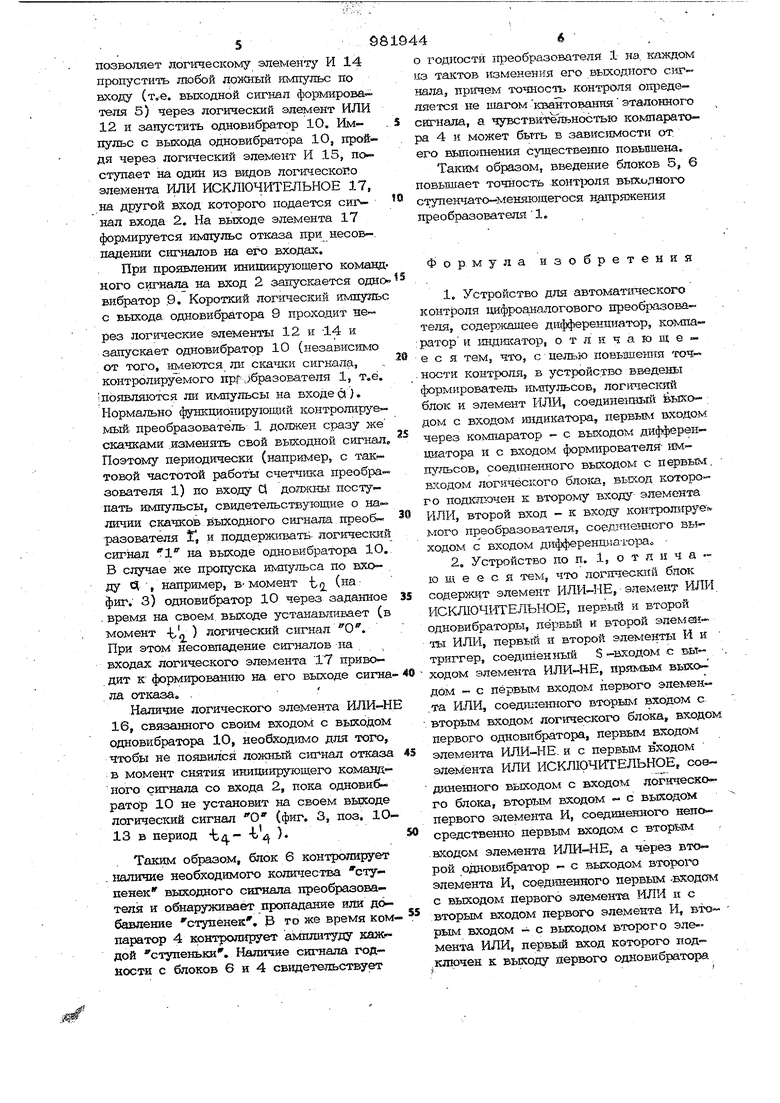

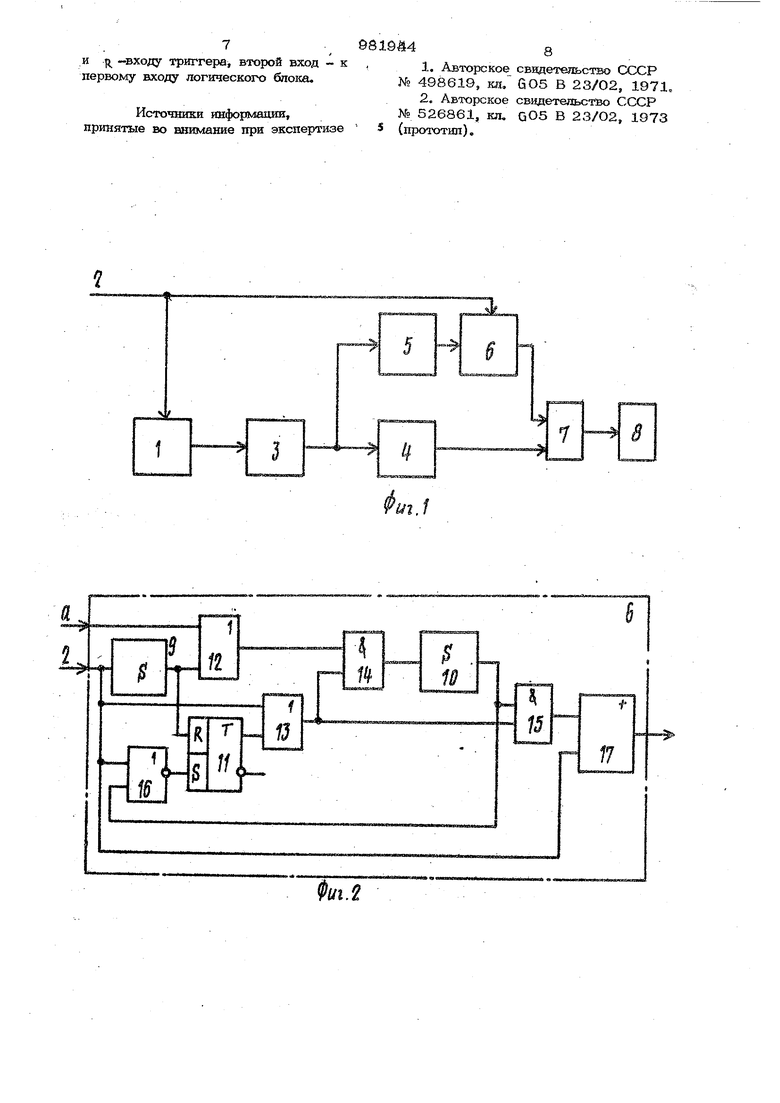

На фщ% 1 пр.иведепа бгюк-схем-.а устройства 11Й фиг, 2 - ,пртп.ц-шиальная схема логического 6nojtaj на фиг, -3 време1шые диаграл а«л работы устройства.,

Устро1 сгво для контроля преобразовав тел.я 1 содер П1Т вход 2, дифференциатор 3. компаратор 4. формиг юватель импуш-. сов 5. логический блок 6, элемент ИЛИ 7, гауцпсатор 8, первый 9 и второй 10 одновибраторы, триггер 11, второй 12 и первьШ 13 эяементы ИЛИ, второй 14 и первьй 15 элементы И, элемент ИЛИ-НЕ 16, элемент ИЛИ ИСКЛЮЧИТЕЛЬНОЕ 1

Устройство работает слещаспщи обра- зр.м.

Контролнруе.мый преобэ азователь 1 содерлшт, например, двоичный счетчик и преобразова.тель двоичный код-напряжение и работает следующим образом: при отсутствии ин 1Щ-5иру1О1цих командных сигна лов на входе 2 выходной .сигнал контроЛ1фуемого преобразователя имеет неизменое йостоя.1пюе значен11е (на любом уров не во всем диапазоне работы контролируемого источника)} при пояззлении W.KKшшрующего командного сигнала (прибавить-убавить) выходной сигнал сразу же (H.aiipiiMep, Б интервале нериода следования тактовых 10/шульсов счетчика контролируемого преобразо.вателя) начикает изме1шться ступенями строго дозиро величины соответствующей, например, младшему разр5аду счетчика контролируемого преобразователя.

Дифдюренздйатор 3 фиксирует любые скачкн вьзходпо.го сигнала контролируемого преобразователя в ввде импульоов, амплит да которых пропорциональна величине скачков сигнала источника.

При контроле преобразователя 1 допускается, что сбой в работе реверсив ного счетчика этого преобразователя может произойти только в младшем разряде. Сбой Б работе преобразователя 1, например. сбоя в любом разря.це его счетчика контролируемого устройства, приводит к тому, что выходной его имеет увеличетшый скачок, что выявляется компаратором 4 в виде импульса на его выходе (см, фиг. 3, поз, 3, 4 |в момент 4 3), Далее вьзделенный импульс, пройдя через элемент ИЛИ 7, по ciyiiaeT на индикатор 8 и фикс1фуется как неисправность контролир емого уст ройства.

Одновременно любые скачки выходного сигнала контролируемого преобразователя 1, выявленные дифферезЕЩиатором 3, поступают на В.ХОД формирователя 5 и преобразуются в нормированные короткие логичесюте икшульсы.

Далее полученные логические импульсы поступают на вход логического блока 6, работаю.1аего по следующему ал1Х)ритму.

При отсутствии инициирующих команд- ных сигналов со входа 2 скачки выходно сигнала контролируемого преобразовате- ля 1 (а, следовательно, и ямпульсы на выходе формирователя 5) доллшы соответствовать. Любой ложньй скачок, например в момент -t (фиг. 3), свидетельствует о неисправности контролируемого преобразователя 1,- отмечается в виде логического сш-гнала отказа на выходе блока 6 и, пройдя по второму входу по«гического элемента ИЛИ, фиксируется индикатором 8.

При появлении шшциирующегч) комацдного сигнала логический блок 6 формируе с вгнал отказа, если будет пропущен хотя бы один скачок в течение времени существования командного сигнала (например в момент tgr-bi иа фиг. 3). Указанный алгоритм обеспечивается логическим блоком 6.

Логический блок 6 работает следующим образом.

При о-тсутствии инициирующего командного сигнала на входе 2 вьосод триггера 11 устанааэливается (логическим сигналом 1 на вхоДе 5 триггера 11) Б сост05шие логической что позволяет логическому элементу И 14 пропустить любой лонсный 1-гмпульс по входу (т,-е. выходной сигнал формирователя 5) через логический ИЛИ 12и запустить одновибратор 1О. Импульс с выхода одновибратора 1О, пройдя через логический элемент И 15, поступает на один из видов логического элемента ИЛИ ИСКЛЮЧИТЕЛЬНОЕ 17, на другой вход которого подается CHI нал входа 2. На выходе элемента 17 формируется импульс отказа при несов-. падении сигналов на его входах. При проявлении инициирующего комацд кого сигнала на вход 2 запускает-ся одно вибратор .9. Короткий логичес1сий импуль с выхода одновибратора 9 проходит не рез логические элементы 12 и 14 и запускает одновибратор 10 (независимо , от того, 1шеются ли скачки сигнала, контролируемого npf ,бразователя 1, т.е. .появляются ли импульсы на входе q). Нормально фу1жционирующий контролир емый- преобразователь 1 должен сразу же скачками .изменять свой выходной сигнал Поэтому периодически (например, с так. товой частотой работъ счетчика преобразователя 1) по входу О долксны посту пать импульсы, свидетельствующие о наличии скачков выходного сигнала преоб разователя 1, и поддерж1-шать- логический сигнал i на выходе одновибратора 1О. В случае же пропуска импульса по входу Ч/например, в момент tQ (на: фиг, 3) одновибратор 10 через заданное . время на своем выходе устаяавугавает (в момент -Ьп ) логический сигнал О. При этом несозетадение сигналов на входах логическоххэ элемента 17 приводит К формированию на его выходе сигаа ла oTicaaa, . Наличие логического элемента ИЛИ-Н 16, связанного своим входом с выходом одновибратора 10, необходимо для того, чтобы нб портился лолшый сигнал отказа в момент снятия инициирующего командного сигнала со входа 2, пока одновибратйр 10 не установит на своем выходе логический сигнал О (фиг, 3, поз, 1О13в период -t ). Таким образом, блок 6 контролирует наличие необходимого колш-1ес-тБа стуиенек выходного сигнала преобразователя и обнаруживает пропадание Ю1И добавление соупенек. В то же время ком- паратор 4 контролирует амплитуду каждой ступеныш . Наличие сигнала годкости с блоков 6 и 4 свидетепьствует S -46 о годности преобразователя. 1 на 1ш,ждом из тактов изменения его выходного ciir- нала, пр1гчем точность кон1роля определяется не шагом квантования эталонного сйгнеша, а чувстви-гельностью компаратора 4 и может быть в зависимости от его вьшолшения cymecTBeimo повышена, TaKfflvi образом, введение блоков 5, 6 повьялает точность конт1хшя выходного ступенчато-меняющегося напряжения преобразователя 1. Формула изобретения 1,Устройство для автоматического контроля цифрюаналогового преобразователя, содержащее дие1)ференциатор, ко л1аратор и 1Щ.а1жатор, о т я н ч а ю щ е е с я тем, что, с повьапеюгя точности контроля, в устройство введены формирователь Щушульсов, логический блок и элемент ИЛИ, соединегшы выходом с входом шадикатора, первым входом через ко.мпаратор - с выходом дифференциатора и с входом формирователя- импульсов, соединенного выходом с первьгг«1. ВХОДО.М логического блока, выход которого подкгоэчен к второму входу элемента ИЛИ, второй вход - к входа- контролируем мого преобразоватаггя, соедкне шого вЫ ходом с входом дифференциач-о за 2,Устройство по п. 1, о т п и ч а .ю щ е е с я тем, что логический блок содерж.чт элемент ИЛИ-НЕ, элемент ИЛИ ИСКШОЧ}.1ТЕЛЬНОЕ, первьй н второй одновибраторы, первьй и второй эпема - пы ИЛИ, nepBbrti и второй элементы И и триггер, соединенный S -входом с БЫ- ходом элемента ИЛИ-НЕ, itpssNajOvJ дом - с пёрвык входом первого эпемен- .та ИЛИ, соедшхешюго вторым входом с. вторым входом логического блока, входом первого одновибратора, первым входом элемента ИЛИ-НЕ. и с первым входом элемента ИЛИ ИСКЛЮЧИТЕЛЬНОЕ, соединенного выходом с входом norii ieoKO- го блока, вторым входам - с выходом первого элемента И, соединенного непосредственно первым входом с вторшл ксодом элемента ИЛИ-НЕ, а через второй одаовнбратор - с выходом второх о элемента И, соед11ненного первым -входом с выходом первого элеметгга 1-ШИ и с вторым входом первого элемента И, Bixj- рым входом - с выходом второго элемента ИЛИ, первый кход которого подключен к выходу первого одновибратох а

и р -входу триггера, второй вход - к первому входу логического бпо1Ш.

Источники информации, принятые во книмание при экспертизе

8

1.Авторское свидетельство СССР № 498619, кл, 605 В 23/02, 1971.

2.Авторское свидетельстйо СССР № 526861, кл, GO5 В 23/О2, 1973

(прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Следящий фазометр | 1980 |

|

SU894595A1 |

| Следящий фазометр | 1980 |

|

SU1038885A1 |

| Вихретоковый дефектоскоп | 1983 |

|

SU1103141A1 |

| Устройство для контроля качества поверхности изделий | 1983 |

|

SU1116388A1 |

| Устройство для автоматизированного контроля параметров реле | 1985 |

|

SU1265704A1 |

| Устройство для контроля передаточной характеристики КМОП-инвертора | 1987 |

|

SU1522131A1 |

| Система управления | 1983 |

|

SU1168896A1 |

| Гидрологический измеритель скорости звука | 1986 |

|

SU1465715A2 |

| Следящий фазометр (его варианты) | 1981 |

|

SU1029095A1 |

| Устройство для регулирования режимов работы скиповых подъемных установок | 1987 |

|

SU1430334A1 |

Авторы

Даты

1982-12-15—Публикация

1981-05-07—Подача