(54) ЧАСТОТНЫЙ СЕЛЕКТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Селектор | 1981 |

|

SU970671A2 |

| Селектор серий импульсов по частоте повторения | 1981 |

|

SU970673A1 |

| Селектор импульсных последовательностей | 1976 |

|

SU681549A1 |

| Дискриминатор нулевых биений | 1987 |

|

SU1524158A1 |

| Частотный компаратор | 1982 |

|

SU1045376A1 |

| Селектор пар импульсов | 1981 |

|

SU984019A1 |

| Система передачи сигналов тонального телеграфировани | 1982 |

|

SU1107321A1 |

| Частотный компаратор | 1987 |

|

SU1531199A1 |

| Селектор пачки импульсов по длительности | 1978 |

|

SU790248A2 |

| Селектор импульсов | 1979 |

|

SU860299A1 |

Изобретение относится к импульсной технике и может быть использовано в устройствах анализа импульсных последовательностей по частоте.

Известен селектор, содержащий п-кан.альный временной анализатор и n-l логических каскадов запрета

Недостатком данного устройства являетсй возможность возникновения ложной информации.

Наиболее близким по назначению и технической сущности к предлагаемому изобретению является селектор, содержащий два форглирователя импульсов, входы которых соединены с входной шиной, вь1ходы. соответственно с первым и, через элемент НЕ, вторым входом элемента И, выход которого соейинен с выходной шиной С2.}.

Недостатком известного селектора является появление на его выходе ложных сигналов после прекращения последовательности импульсов с частотой, превышающей верхнюю частоту заданного диапазона Fg .

цель изобретения - исключение ложных срабатываний.

Поставленнс1я цель достигается тем, что в частотный селектор, содержащий первый формирователь импульсов.

вход которого соединен с входной шиной, второй формирователь импульсов, выход которого через элемент интегрирования соединен с входом порогового элемента, введен формирователь импульсов по срезу сигнала вход которого соеда1нен с выходом первого форкшрователя импульсов, а выход - с входом второго формирователя

10 импульсов, причем выход порогового элемента соединен с выходной шиной.

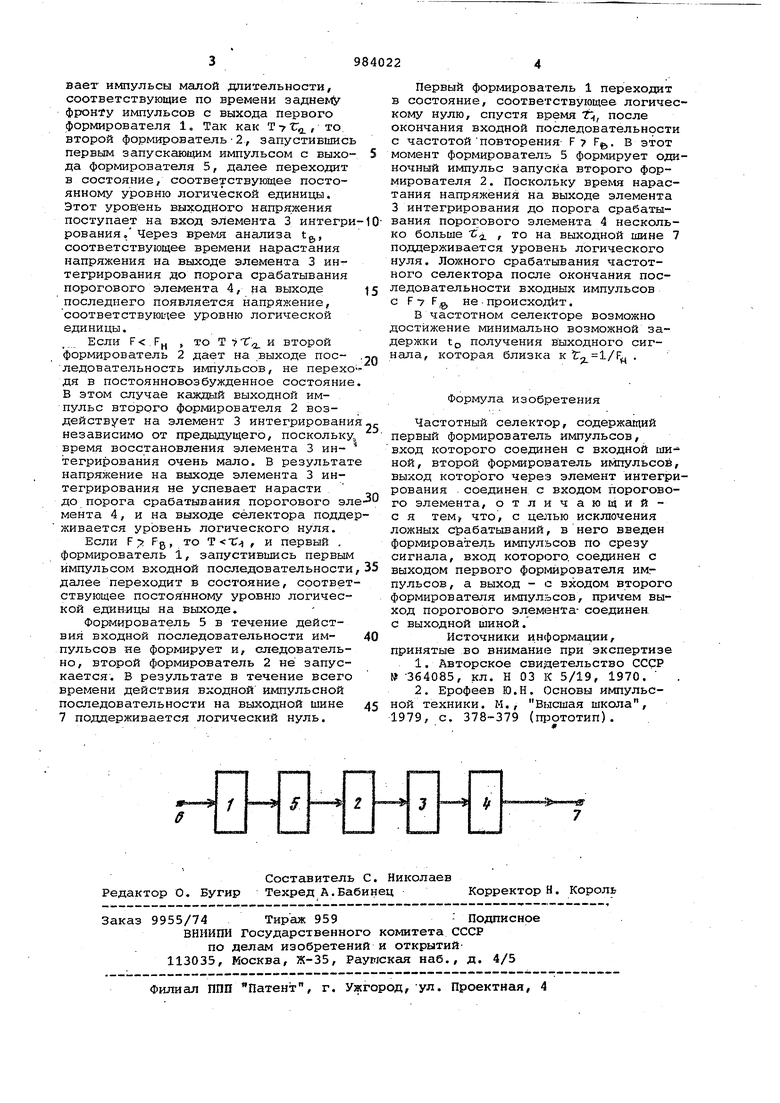

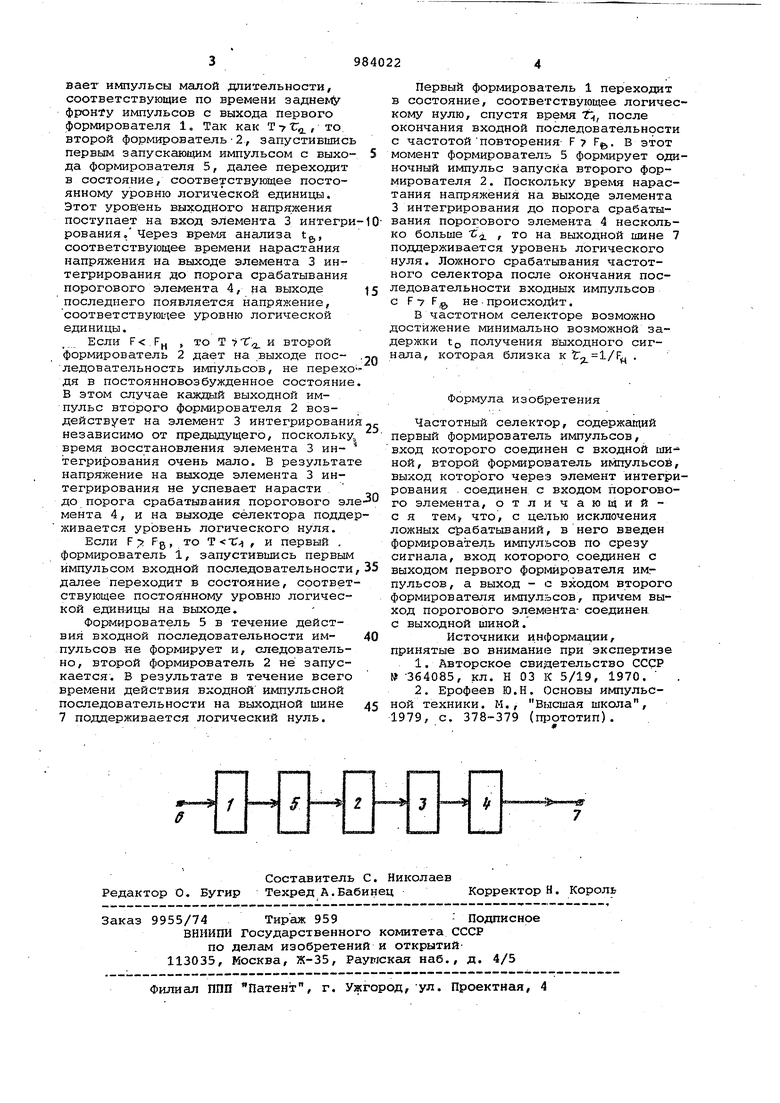

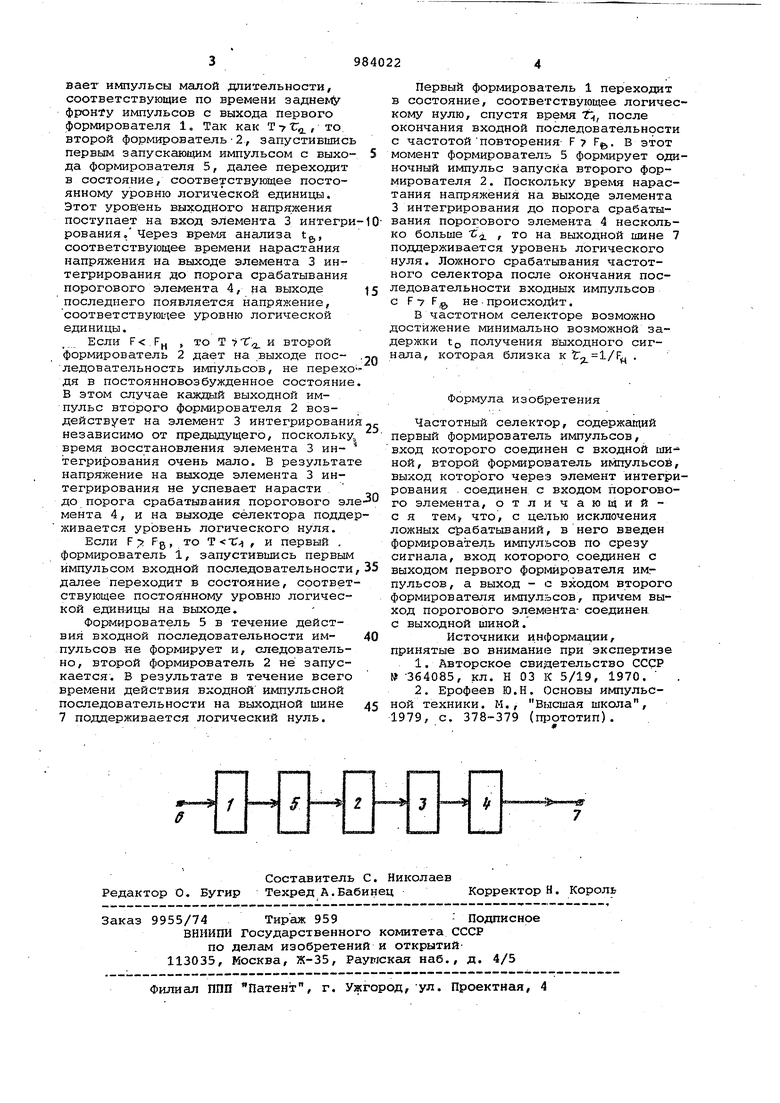

На чертеже представлена структурная схема частотного селектора.

Частотный селектор содержит первый

5 фор1лирователь 1 импульсов, второй формирователь 2 импульсов, элемент 3 интегрирования, пороговый элемент 4, формирователь 5 импульсов по сразу сигнала, входную шину 6 и выходную

шину 7.

Частотный селектор работает следукядим образом.

На его входную шину 6 поступает последовательность входных импульсов

25 с частотой повторения FH F F. В . этом случае T l/F7T.,(r l/Fe и t(l/FH - длительность импульсов, формируемых соответственно первьш форглирователем 1. и, вторы1Л формирова30 хелем 2). Формирователь 5 вырабатываег импульсы малой длительности, соответствующие по времени заднему фронту импульсов с выхода первого формирователя 1 „ Так как Т 7 Т, , то второй формирователь2, запустившис первым запускающим импульсом с выхо да формирователя 5, далее переходит в состояние, соответствующее постоянному уровню логической единицы. Этот уровень выходного напряжения поступает на вход элемента 3 интегр рования, Через врег/1я анализа tg,, соответствующее времени нарастания напряжения на выходе элемента 3 ин тегрирования до порога срабатывания порогового элемента 4, на выходе последнего появляется напряжение, соответствуюь- ее уровню логической единицы. Если F.FH , то Т , и второй формирователь 2 дает на выходе последовательность импульсов, не перех дя в постоянновозбужденное состояни В этом случае каждый выходной импульс второго форг-лирователя 2 воздействует на элемент 3 интегрирован независимо от предыдущего, поскольку время восстановления элемента 3 интегрирования очень мало. В результа напряжение на выходе элемента 3 интегрирования не успевает нарасти до порога срабатывания порогового эл мента 4, и на выходе селектора подде живается уровень логического нуля. Если F/г Fg, то ) , и первый , формирователь i, запустившись первым импульсом входной последовательности далее переходит в состояние, соответ ствующее постоянному уровню логической единицы на выходе. Формирователь 5 в течение действия входной последовательности импульсов не формирует и, следовательно, второй формирователь 2 не запускается. В результате в течение всего времени действия входной импульсной последовательности на выходной шине 7 поддерживается логический нуль. Первый форг-тарователь 1 переходит в состояние, соответствующее логическому нулю, спустя время 7:, после окончания входной последовательности с частотойповторения F Fg,, В этот момент формирователь 5 формирует одиночный импульс запуска второго формирователя 2. Поскольку время нарастания напряжения на выходе элемента 3 интегрирования до порога срабатывания порогового элемента 4 несколько больше Ci , то на выходной шине 7 поддерживается уровень логического нуля. Ложного срабатывания частотного селектора после окончания последовательности входных импульсов с F7 F не происходит. в частотном селекторе возможно достижение минимально возможной задержки to получения выходного сигнала, которая близка к t, . Формула изобретения Частотный селектор, содержащий первый формирователь импульсов, вход которого соединен с входной шиной, второй формирователь импульсов, выход которого через элемент интегрирования соединен с входом порогового элемента, отличающийс я тем, что, с целью исключения ложных срабатываний, в него введен формирователь импульсов по срезу сигнала, вход которого, соединен с выходом первого фopIvшpoвaтeля имг пульсов, а выход - с входом второго формирователя импульсов, причем выход порогового элемента- соединен с выходной шиной. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № -364085, кл. Н 03 К 5/19, 1970. . 2.Ерофеев Ю.Н. Основы импульсной техники. М., Высшая школа, 1979, с. 378-379 (прототип).

Авторы

Даты

1982-12-23—Публикация

1981-06-04—Подача