«зобретение относится к измерительной технике и может использоваться в приемниках многочастотного кода для определения параметров двухтональных сигналов, неизвестных на приемной стороне.

Известно устройство для определения параметров двухтональных сигналов, содержащее блок управления (формирователь интервала), блок стробирования, вычислитель, .переключаннций элемент (для подачи строб-импульсов в цифровой форме на вычислитель), детектор уров.ня и индикатор частоту причем вычислитель состоит из измерителя интервалов, ;;анализатора полярности, анализатора частот сигнала, компаратора Cl.

Основньм недостатком известного устройства является низкое качество оценки параметров двухтональных сигналов, неизвестных на приемной стороне.

Это объясняется тем, что при неравенстве амплитуд тональных сигналов, оценка частот двухтональных сигналов в известном устройстве осу1ществляется с ошибкой, зависящей от соотношения амплитуд тональных сигналов, поскольку суммарная частотная составляющая модулирована по фазе и является функцией разностной частоты и соотношения амплитуд тональных сигналов. Кроме того,-в известном устройстве отсутствует возможность оценки амплитуд тональных сигналов, что значительно снижает качество оценки параметров двух тональных сигналов, неизвестных на

10 приемной стороне.

Цель изобретения - повышение точности оценки при повышении быстродействия процесса оценки.

Поставленная цель достигается

15 тем, что в устройство, содержащее блок управления, блок стробирования и вычислитель, введены фо эмирователь второй производной, четыре блока

- .-памяти и четыре электронных ключа,

первые входы которых подключены соответственно к четырем выходам вычислителя, первыйf второй, третий и четвертый входы которого соединены соответственно с выходами первого,

25 второго, третьего и четвертого блоков памяти, причем вход устройства соединен с первьм входом блока етробирования, с первьвии входами первого и второго блоков памяти, выходы

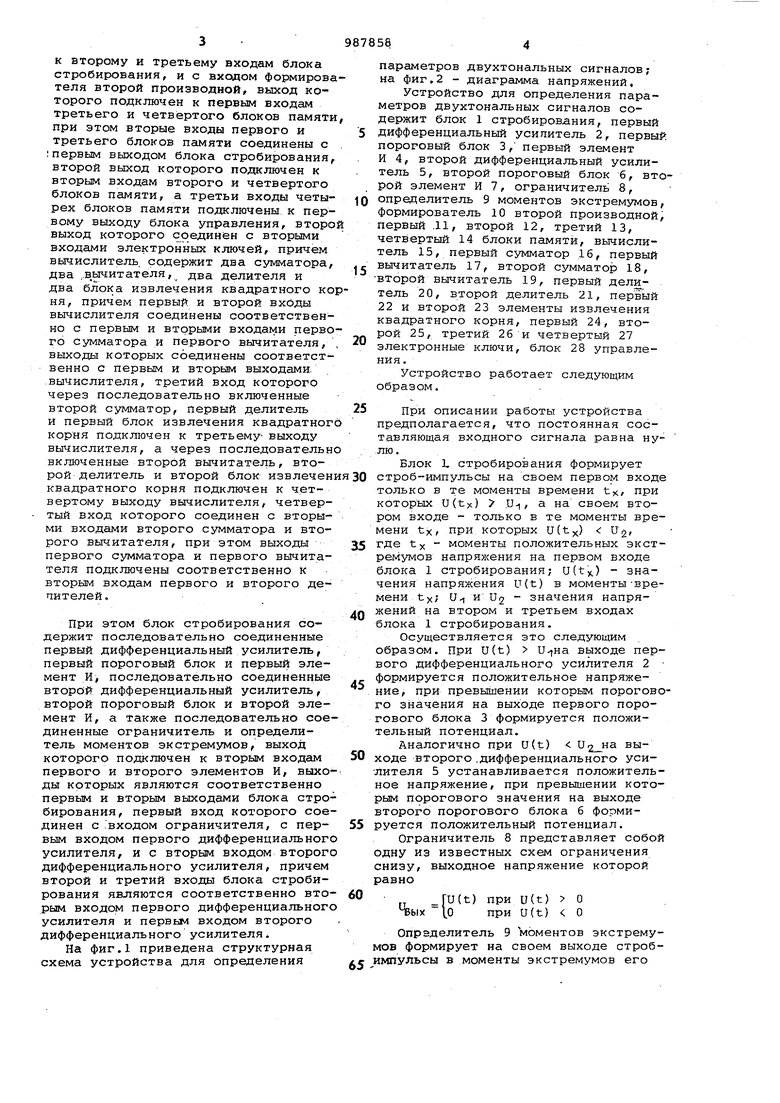

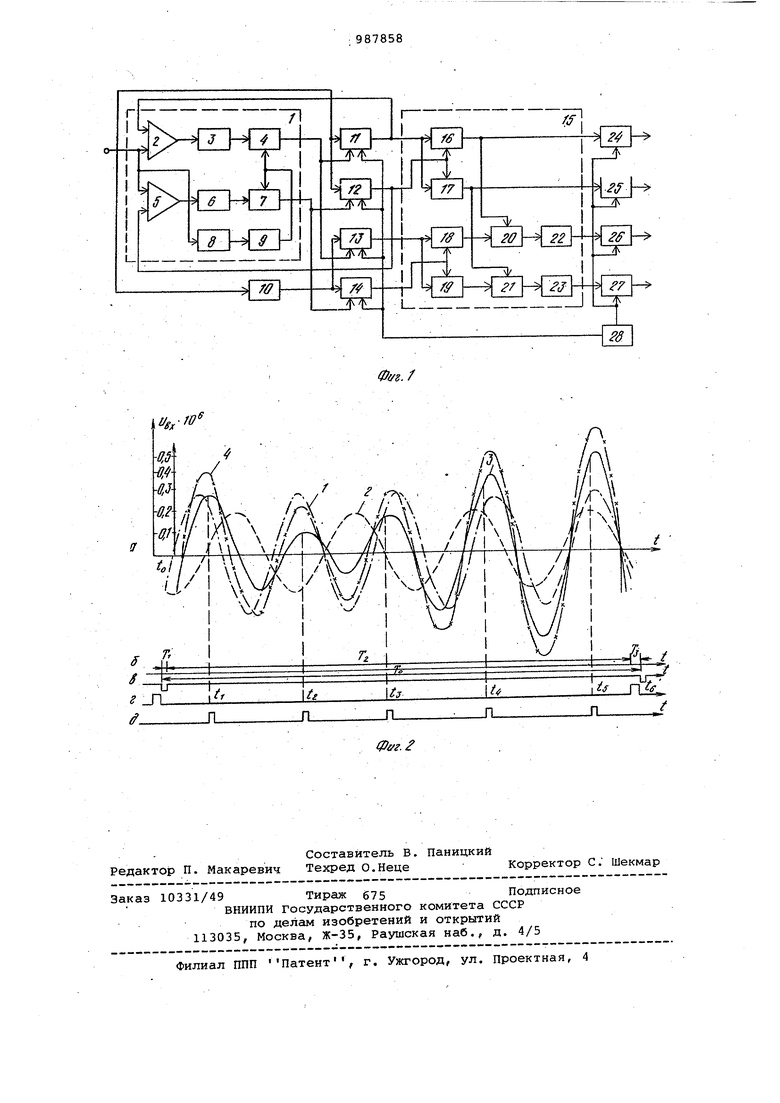

30 которых подключены соответственно к второму и третьему входам блока стробирования, и с входом формирова теля второй производной, выход которого подключен к первым входам третьего и четвертого блоков памяти при этом вторые входы первого и третьего блоков памяти соединены с I первым выходом блока стробирования второй выход которого подключен к вторым входам второго и четвертого блоков памяти, а третьи входы четырех блоков памяти подключены к первому выходу блока управления, второ выход которого соединен с вторыми входами электронных ключей, причем вычислитель, содержит два сумматора, два ..в.ычитателя, два делителя и два блока извлечения квадратного ко ня, причем первый и второй вхОды вычислителя соединены соответственно с первым и вторыми входами перво го сумматора и первого вычитателя, выходы которых соединены соответственно с первым и вторым выходами, вычислителя, третий вход которого через последовательно включенные второй сумматор, первый делитель и первый блок извлечения квадратног корня подключен к третьему- выходу вычислителя, а через последовательн включенные второй вычитатель, второй делитель и второй блок извлечен квадратного корня подключен к четвертому выходу вычислителя, четвертый вход которого соединен с вторыми входами второго сумматора и второго вычитателя, при этом выходы первого сумматора и первого вычитателя подключены соответственно к вторым входам первого и второго депителей. При этом блок стробирования содержит последовательно соединенные первый дифференциальный усилитель, первый пороговый блок и первый элемент И, последовательно соединенные второй дифференциальный усилитель, второй пороговый блок и второй элемент И, а также последовательно сое диненные ограничитель и определитель моментов экстремумов, выход которого подключен к вторым входам первого и второго элементов И, выхо ды которых являются соответственно первым и вторым выходами блока стро бирования, первый вход которого сое динен с .входом ограничителя, с первым входом первого дифференциальног усилителя, и с вторым входом второг дифференциального усилителя, причем второй и третий входы блока стробирования являются соответственно вто рым входом первого дифференциальног усилителя и первьм входом второго дифференциального усилителя. На фигЛ приведена структурная схема устройства для определения параметров двухтональных сигналов; на фиг,2 - диаграмма напряжений. Устройство для определения параметров двухтональных сигналов содержит блок 1 стробировлния, первый дифференциальный усилитель 2, первый пороговый блок 3, первый элемент И 4, второй дифференциальный усилитель 5, второй пороговый блок б, второй элемент И 7, ограничитель 8, определитель 9 моментов экстремумов, формирователь 10 второй производной, первый .11, второй 12, третий 13, четвертый 14 блоки памяти, вычислитель 15, первый сумматор .16, первый вычитатель 17, второй суммато р 18, второй вычитатель 19, первый дели- . тель 20, второй делитель 21, первый 22 и второй 23 элементы извлечения квадратного корня, первый 24, второй 25, третий 26 и четвертый 27 электронные ключи, блок 28 управления. Устройство работает следующим образом. При описании работы устройства предполагается, что постоянная составляющая входного сигнала равна ну.лю. Блок 1, стробирования формирует строб-импульсы на своем первом входе только в те моменты времени tx/ при которых U(tx) .U-,, а на своем втором входе - только в те моменты времени txf при которых U(t) Ugf где ty - моменты положительных экстремумов напряжения на первом входе блока 1 стробирования; U{ty.) - значения напряжения U(t) в моменты-времени U-I и U2 - значения напряжений на втором и третьем входах блока 1 стробирования. Осуществляется это следующим образом. При U(t) вьзходе первого дифференциального усилителя 2 формируется положительное напряжение, при превышении которым порогового значения на выходе первого порогового блока 3 формируется положительный потенциал. Аналогично при U(t) выходе второго .дифференциального уси-лителя 5 устанавливается положительное напряжение, при превышении которым порогового значения на выходе второго порогового блока 6 формируется положительный потенциал. Ограничитель 8 представляет собой одну из известных схем ограничения снизу, выходное напряжение которой равно U(t) при U(t) О 1Быx при U(t) О Опраделитель 9 моментов экстремумов формирует на своем выходе стробимпульсы в моменты экстремумов его

входного напряжения одним из известных спос6бов

Импульсы с выхода определителя 9 моментов экстремумов проходят на первый выход блока 1 стробирования при наличии положительного потенциала на первом входе первого элемента И 4, т.е. при U(tx) U-,, а при наличии положительного-потенциала на первом входе второго элемента И 7, т.е. при U(tx). U2 проходят на второй выход блока 1 стробирования.

Формирователь 10 втЪрой проиэводной формирует на своем в.ыходе напряжение, равное второй производной его входного сигнала, одним из известных способов, например путем двойного дифференцирования входного сигнала и усиления в I/T; раз, где т; - время дифференцирования.

В качестве первого, второго, третьего и четвертого блоков 11 - 1 памяти используются схемы ВЫБОРКАЗАПОМИНАНИЕ , на выходах каждой из которых устанавливается и хранится напряжение, равное напряжению на ее первом входе в момент наличия импулса на ее втором входе. При поступлении нулевого потенциала на третьи входы первого, третьего и четвертог блоков 11, 13 и 14 памяти на их выходах устанавливается нулевое напряжение, а при поступлении нулевого потенциала на третий вход второго блока 12 памяти на ее выходе устаналивается положительный потенциал, близкий к напряжению питания.

Выходные напряжения первого,второго и третьего и четвертого блоков 11 - 14 памяти поступают соответственно на первый, второй, третий и четвертый входы вычислителя 15, осуществляющего операции сложения, вычитания и деления напряжений, а также операцию извлечения квадратного корня, при этом входящие в состав вычислителя 15 первый и второй сумматоры 16 и 18, а также первый и второй вычитатели 17 и 19 представляют собой известные схемы сумматора и вычитателя с той лишь разницей что на их входах сигналы делятся в 2 раза, например, с помощью резисторов, а на их выходах формируются .напряжения, равные полусумме и соответственно полуразности их входных напряжений.

Выходные сигналы вычислителя 15 проходят на выходы устройства при наличии положительных потенциалов на вторых входах первого, второго, третьего и четвертого электронных ключей 24 - 27, формируемых блоком 28 управления.

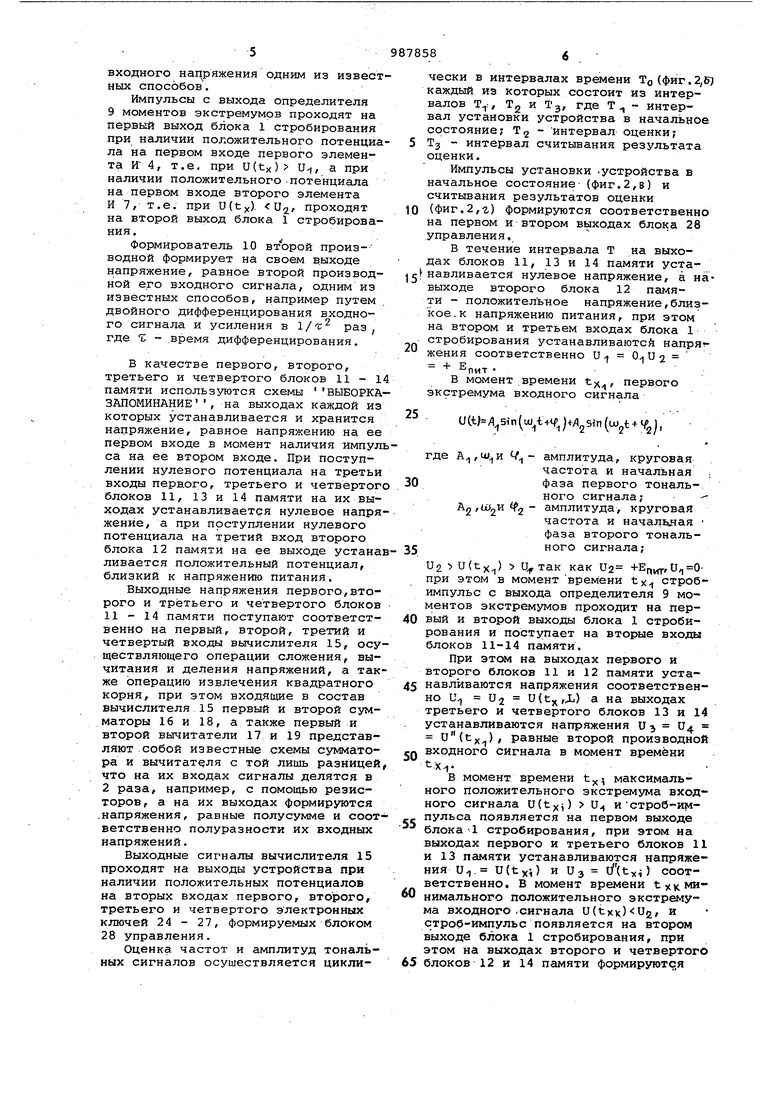

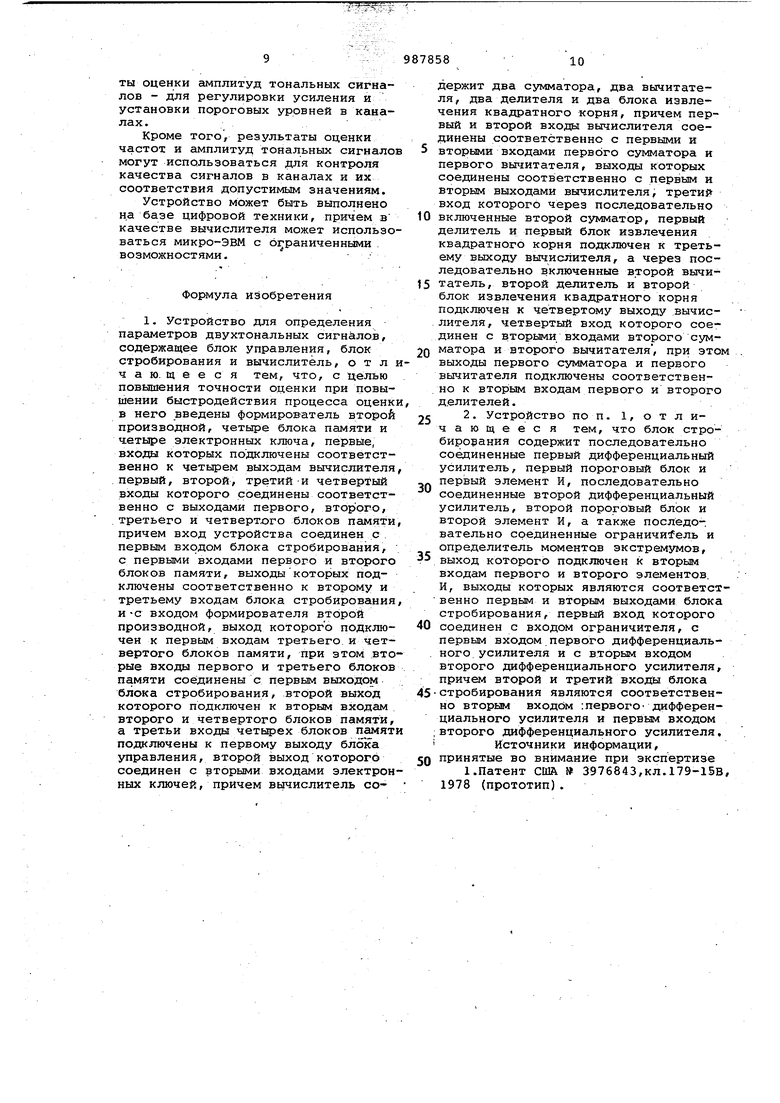

Оценка частот и амплитуд тональных сигналов осуществляется циклически в интервалах времени То(фиг.2,& каждый из которых состоит из интервалов TY, Tg и Тз, где Т - интервал установки устройства в начальное состояние; f-2 интервал оценки;

5 Tj - интервал считывания результата оценки.

Импульсы установки .устройства в начальное состояние-(фиг.2,в) и считывания результатов оценки

10 (фиг.2,г) формируются соответственно на первом и втором выходах блока 28 управления.

В течение интервала Т на выходах блоков 11, 13 и 14 памяти уста jfнавливаетсЯ нулевое напряжение, а навыходе второго блока 12 памяти - положительное напряжение,близкое, к напряжению питания, при этом на втором и третьем входах блока 1 стробирования устанавливаются напрят жения соответственно и 0.) U 2

+ Е

пит

В момент времени tj, первого экстремума входного сигнала

25

и Ct) (wJ.,i+4, ) (Wjt + 21,

где А, амплитуда, круговая частота и начальная

30фаза первого тональ-.

ного сигнала; А2ги 2 2 амплитуда, круговая частота и начальная фаза второго тональ35ного сигнала;

U2 ) ц, так как 02 +Епит, при этом в момент времени tx стробимпульс с выхода определителя 9 моментов экстремумов проходит на пер40 вый и второй выходы блока 1 стробирования и поступает на вторые входы блоков 11-14 памяти.

При этом на выходах первого и второго блоков 11 и 12 памяти уста45 навливаются напряжения соответственно U., Uj ) а на выходах третьего и четвертого блоков 13 и 14 устанавливаются напряжения U(t;(), равные второй производной

входного сигнала в момент времени

50 -х.

в момент времени tj, максимального положительного экстремума входного сигнала U(txi) U истроб-импульса появляется на первом выходе

55 блока 1 стробирования, при этом на выходах первого и третьего блоков 11 и 13 памяти устанавливаются напряжения U-,. U{txi) и 03 (txi) соответственно. В момент времени

нймального положительного экстремума входного сигнала U(txK) и строб-импульс появляется на втором выходе блока 1 стробирования, при этом на выходах второго и четвертого

65 блоков 12 и 14 памяти формируютс,я напряжения Ug, V(t) и v U(tx/ соответственно. Следовательно, в течение интерва ла времени Т оценки на выходах первого и второго блоков 11 и 12 па мяти устанавливаются напряжения U-, и Uj, равные соответственно значениям входного сигнала в моменты вре мени t и t,, т.е. в моменты максимального и минимального положител ных экстремумов входного сигнала, а на выходах третьего и четвертого блоков 13 и 14 памяти устанавливают ся напряжения, равные второй производной входного сигнала соответственно в моменты времени и txK (фиг., 2,0) . Максимальное экстремальное значе ние входного сигнала имеет место при при этом и (первый сигнал) я А Если предположить, что А то минимальное положительное экстре мальное значение входного сигнала имеет место при + {j«jT/2 , при этом Ug (второй сигнал) ss А-,- А Значение второй .производнойвход ного сигнала в моменты его максимального и минимального положительного экстремумов соответственно равны2 а Uj {третий сигнал) .,+ A2UJ2 5; ASUI Ui (четвертый сигнал) Ввычислителе 15 первый и второй сумматоры 16 и 18 формируют на своих выходах сигналы, равные полусуммам ИХ входных сигналов, а первый и вто рой вычитатели 17 и 19 формируют на своих выходах сигналы, nojiy- раГзйостям сигналов на их входах. Дос тигается это использованием известных схем суммирования и вычитания, входные сигналы которых делятся на 2, например, на резисторах. В этом случае напряжения Ug - на выходах узлов вычислителя 15 соответственно равны (U-1 + Uj).,,; Ue V2 (UT - Ug)-Ag; U, 1/2(0., + U.)%-A u).,; Ug 1/2 (Uj - U) -A2U)|; где U5, U{j, U-j и UB - напряжения на выходах первого сумматора, первого вычитателя, второго сумматора и второго вычитателя,, Ug и-,/и сй-ы ; Ue/Ufe . UV., .-Lo, i 11 где Ug, , напряжения на входах первого и второго делителей 2J) и. 21, и первого и второго элемантов 22 и 23 извлечения квадратного корня. Напряжения и UfoU-r-fH 12 тервалы Т проходят на выходы устройства через электронные ключи 24 27, открытые импульсами со второго выхода блока 28 управления. При этом на выходы первого и второго электронных ключей 24 и 25 проходят напряжения, соответствующие. амплитудам первого (с большей амплитудой) и второго (с меньшей амплитудои) тональных сигналов, на выходы третьего и четвертого электронных ключей 26 и 27 проходят напряжения, соответствующие частотам первого и второго тональных, сигналов, В. случае ji если :/ А минимальноеположительное экстремальное значе.ние входного .сигнала имеет место при ,., 4. л-(О jj-jy .... 1 .1 при этом + и т « -А гу U) и.,, к-и; 2 , Следовательно, независимо от соотношений амплитуд тональных сигналов на выходах первого и третьего электронных ключей 24 и 26 устанавливаются напряжения, соответствующие амплитуде и частоте тонального сигнала с большей амплитудой, а на выходах второго и четвертого элект- ронных ключей 25 и 27 - соответствующие а лплитуде и частоте тоналвного сигнала с меньшей амплитудой (фиг.2,Э). При равенстве амплитуд тональных сигналов напряжения на выходах первого и второго электронных ключей 24 и 25 равны, так как Ug О и Us и 1/2 и. . . Следовательно, предлагаемое устройство определяет частоты и амплитуды тональных сигналов, неизвестные на приемной стороне, так как осуществляет оценку параметров тональных сигналов при отсутствии эталонов частот входных сигналов, причем частоты и амплитуды тональных сигналов определяются независимо друг от друга, а результаты оценки частот сигналов не зависят от соотношения их амплитуд. При использовании предлагаемого устройства в составе приемника многочастотного крда представляется возможность применения только двух каналов с автоматической настройкой на тональные частоты сигнала, параетры которого неизвестны на приемной стороне. При этом результаты оценки частот могут использоваться ля автоматической настройки канаов на частоты сигналов, а результаты оценки амплитуд тональных сигналов - для регулировки усиления и установки пороговых уровней в каналах.

Кроме того, результаты оценки частот и амплитуд тональных сигналов могут использоваться для контроля качества сигналов в каналах и их соответствия допустимым значениям.

Устройство может быть выполнено на базе цифровой техники, причем в качестве вычислителя может использоваться микро-ЭВМ с ограниченными . возможностями.

Формула изобретения

1. Устройство для определения параметров двухтональных сигналов, содержащее блок управления, блок стробирования и вычислитель, о т л ич а ю. щ е е с я тем, что, с целью повышения точности оценки при повышении быстродействия процесса оценки в него введены формиров атель второй производной, четьфе блока памяти и четыре электронных ключа, первые, входа которых подключены соответственно к четырем выходам вычислителя, первый, второй, третий-и четвертый входы которого соединены соответственно с выходами первого, , третьего и четвертого блоков памяти, причем вход устройства соединен с первым входом блока стробирования, с первыми входами первого и второго блоков памяти, выходы которых подключены соответственно к второму и третьему входам блока стробирования/ и-с входом формирователя второй производной, выход которого подключен к первым входам третьего и четвертого блоков памяти, при этом вторые входы первого и третьего блоков памяти соединены с первым выходом блока стробирования, второй выход которого подключен к вторым входам второго и четвертого блоков памяти, а третьи входы четь1рех блоков памяти подключены к первому выходу блока управления, второй выход которого соединен с вторыми входами электронных ключей, причем вычислитель содержит два сумматора, два вычитателя, два делителя и два блока извлечения квадратного корня, причем первый и второй входы вычислителя соединены соответственно с первыми и

вторыми входами первого сумматора и первого вычитателя, выходы которых соединены соответственно с первым и вторым выходами вычислителя, третий вход которого через последовательно

включенные второй сумматор, первый делитель и первый блок извлечения квадратного корня подключен к третьему выходу вычислителя, а через последовательно включенные второй вычитатель, второй делитель и второй блок извлечения квадратного корня подключен к четвертому выходу вычислителя, четвертый вход которого соединен с вторыми входами второго сумматора и второго вычитателя, при этом выходы первого сумматора и первого вычитателя подключены соответственно к вторым входам первого и второго д.елителей.

2. Устройство по п. 1, о т л ичающеес я тем, что блок стробиро ания содержит последовательно соединенные первый дифференциальный усилитель, первый пороговый блок и первый элемент И, последовательно соединенные второй дифференциальный усилитель, второй пороговый блок и второй элемент И, а также последо-. вательно соединенные ограничитель и определитель моментов экстремумов,

выход которого подключен к вторым входам первого и второго элементов. И, выходы которых являются соответственно первьм и вторым выходами блока стробирования, первый вход которого

соединен с входом ограничителя, с первым входом первого дифференциального усилителя и с вторым входом второго дифференциального усилителя, причем второй и третий входы блока

стробирования являются соответственно вторым входом : первогоДифференциального усилителя и первым входом ;второго дифференциального усилителя, i Источники информации,

принятые во внимание при экспертизе

1.Патент США 3976843,КЛ.179-15В, 1978 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для выделения двухтональных сигналов | 1982 |

|

SU1059705A1 |

| Радиоимпульсный фазометр | 1982 |

|

SU1081561A1 |

| Устройство для определения параметров экстремумов сигналов | 1982 |

|

SU1075178A2 |

| Устройство для измерения отношения сигнала к помехе в телевизионном канале | 1985 |

|

SU1292206A1 |

| Фазометр | 1984 |

|

SU1228040A2 |

| Устройство для поиска координат точки экстремума функции двух переменных | 1981 |

|

SU966703A1 |

| СИСТЕМА ДЛЯ УПРАВЛЕНИЯ ПРОЦЕССОМ ПРОДАЖИ ТОВАРОВ | 1999 |

|

RU2168762C2 |

| Устройство для измерения фазовых сдвигов | 1986 |

|

SU1370597A1 |

| УСТРОЙСТВО ДОПУСКОВОГО КОНТРОЛЯ ПАРАМЕТРОВ РАДИОСИГНАЛА ВЕЩАТЕЛЬНОГО ТЕЛЕВИДЕНИЯ | 1989 |

|

RU2019062C1 |

| Способ уравновешивания цифровых экстремальных мостов переменного тока и устройство для его осуществления | 1986 |

|

SU1418626A1 |

У

Авторы

Даты

1983-01-07—Публикация

1980-08-18—Подача