(54) ДВУХПОРОГОЫ Й ЛОГИЧЕСКИЙ ЭЛЕМЕНТ

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОКАНАЛЬНЫЙ ИЗМЕРИТЕЛЬ ПАРАМЕТРОВ ДАТЧИКОВ | 2022 |

|

RU2795214C1 |

| Формирователь импульсов | 1978 |

|

SU744942A1 |

| Импульсный стабилизатор постоянного разнополярного напряжения | 1985 |

|

SU1403041A1 |

| Однотактный преобразователь постоянного напряжения | 1990 |

|

SU1767649A1 |

| Устройство для управления центрифугой | 1990 |

|

SU1733107A1 |

| Устройство для трехпозиционного управления (его варианты) | 1983 |

|

SU1185586A1 |

| Формирователь импульсов | 1979 |

|

SU809353A1 |

| Стабилизатор напряжения | 1989 |

|

SU1700546A1 |

| Устройство для управления электромагнитом | 1984 |

|

SU1163385A1 |

| Стабилизированный источник питания постоянного напряжения | 1990 |

|

SU1718205A1 |

Изобретение относится к импульсной технике и может быть использовано в устройствах автоматики и вычислительной техники.

Известен двухпороговый логический элемент, содержащий резистор, конденсатор и суммирующие резисторн, соединяющие входы двухпорогового логического элемента с первой обкладкой конденсатора, входом формирователя передаточной характеристики, который через резистор соединен с общей шиной и второй обкладкой конденсатора, а выход формирователя передаточной характеристики соединен с входом генератора и myльcoв l j.

Недостатком этого элемента явля,ется относительно низкая надежность.

Известен двухпороговый логический элемент, содержащий транзистор, резистор и суммирующие резисторы 2

Недостатком известного двухпорогового логического элемента является невозможность обеспечения с помощью этого элемента достаточно высокой достоверности функциониройания.

Целью изобретение является повышение достоверности функционирования.

Поставленная цель достигается тем, что в двухпороговый логически элемент, содержащий транзистор, резистор и суммирующие резисторы, введены первый, второй и третий конденсаторы, дополнительный резистор, первый и второй вспомогательные резисторы, первый и второй диоды, стабилитрон, вспомогательный п-р-п транзистор и вспомогательный р-п-р транзистор, эмиттер которого соединен с эмиттером вспомогательного п-р-п транзистора, база которого соединена с общей шиной, которая соединена с катодом первого диода, через первый конденсатор - с ко.гтектором вспомогательного п-р-п транзистора, через второй конденсатор - с выходом двухпорогового логического элемента и

20 анодом второго диода и через резистор - с катодом второго диода, который чбрез третий конденсатор соединен с эмиттером транзийтора, который через дополнительный резистор сое25динен с коллектором вспомогательного п-р-п транзистора и анодом стабилитрона, который через суммирующие резисторы соединен с входами двухпорогового логического элемента, катод

30 стабилитрона соединен с анодом пер.вого диода и через первый вспомогательный резистор с отрицательным полисом источника питания, который соединен с коллектором транзистора и через второй вспомогательный резнетор с базой транзистора, которая соединена с коллектором вспомогательного р-п-р транзистора.

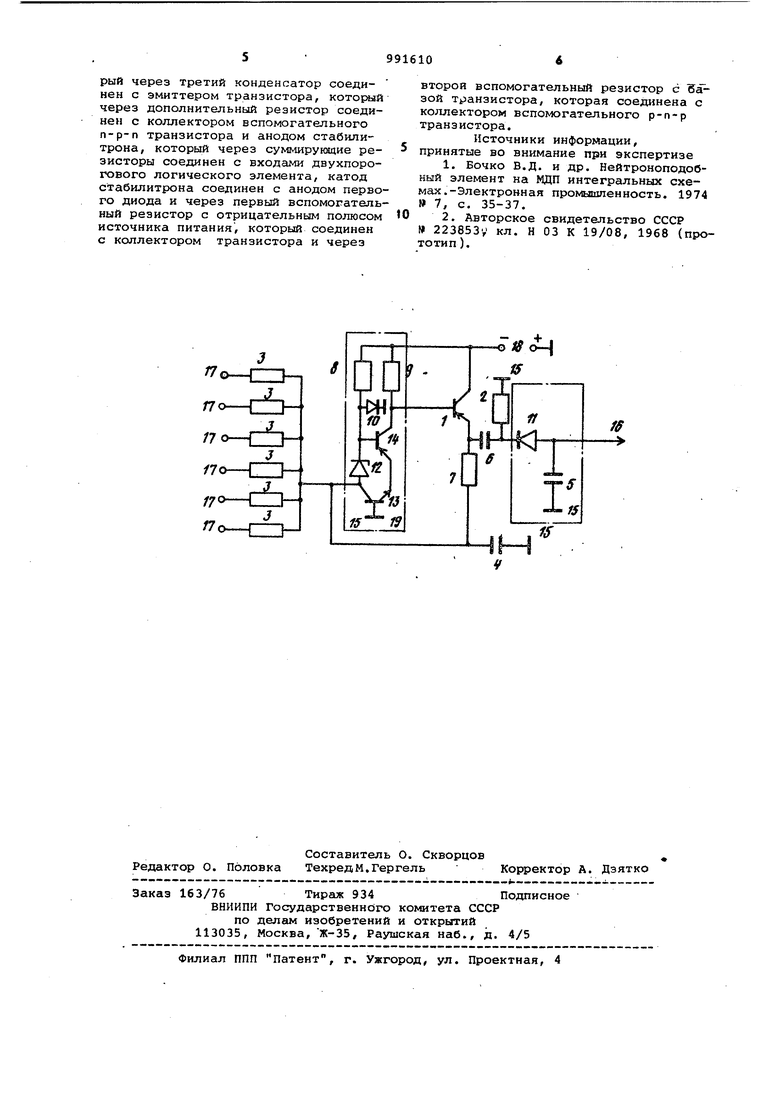

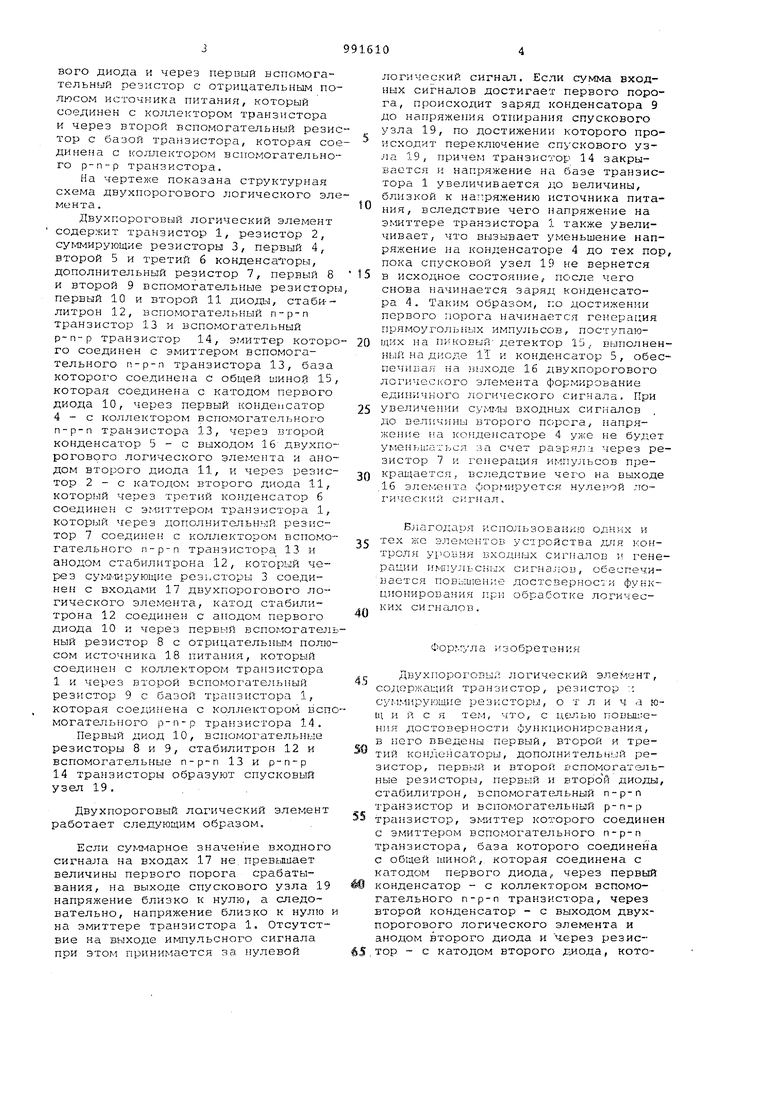

На чертеже показана структурная схема двухпорогового логического элемента .

Двухпороговый логический элемент содержит транзистор 1, резистор 2, суммирующие резисторы 3, первый 4, второй 5 и третий б конденсаторы, дополнительный резистор 7, первый 8 и второй 9 вспомогательные резисторЕ первый 10 и второй 11 диоды, стаби-литрон 12, вспомогательный п-р-п транзистор 13 и вспомогательный р-п-р транзистор 14, эмиттер которого соединен с эмиттером вспомогательного п-р-п транзистора 13, база которого соединена с общей шиной 15, которая соединена с катодом первого диода 10, через первый конденсатор 4 с коллектором вспомогательного п-р-п транзистора 13, через второй конденсатор 5 - с выходом 16 двухпорогового логического элемента и анодом второго диода 11, и через резистор 2-е катодом второго диода 11, который через третий конденсатор б соединен с эмиттером транзистора 1, который через дополнительный резистор 7 соединен с коллектором вспомогательного п-р-п транзистора 13 и анодом стабилитрона 12, который через сумг-шрующие резисторы 3 соединен с входами 17 двухпорогового логического элемента, катод стабилитрона 12 соединен с анодом первого диода 10 и через первый вспомогательный резистор 8 с отрицательным полюсом источника 18 питания, который соединен с коллектором транзистора 1 и через второй вспомогательный резистор 9 с базой транзистора 1, которая соединена с коллектором вспомогательного р-п-р траьЗистора 14.

Первый диод 10, всгюмогательнЕле резисторы В и 9, стабилитрон 12 и вспомогательные п-р-п 13 и р-п-р 14 транзисторы образуют спусковый узел 19.

Двухпороговый логический элемент работает следующим образом.

Если суммарное значение входного сигнала на входах 17 не.превышает величины первого порога срабатывания, на выходе спускового узла 19 напряжение близко к нулю, а следовательно, напряжение близко к нулю и на эмиттере транзистора 1. Отсутствие на выходе импульсного сигнала при этом принимается за нулевой

логический сигнал. Если сумма входных сигналов достигает первого порога, происходит заряд 1сонденсатора 9 до напряжения отпирания спускового узла 19, по достижени1 которого происходит переключение спускового узла 19, причем транзистор 14 закрывается и напряжение на базе транзистора 1 увеличивается до величины, близкой к напряжению источника питания, вследствие чего напряжение на эмиттере транзистора 1 также увеличивает, что вызывает уменьшение напряжение на конденсаторе 4 до тех пор, пока спусковой узел 19 не вернется

5 в исходное состояние, после чего снова начинается заряд конденсатора 4. Таким образом, по достижении первого порога начинается генерация прямоугольных импульсов, поступаю0 щих на пикоЕый детектор 15, выполненный на диоде II и конденсатор 5, обеспечивая на } ыходе 16 двухпорогового логического элемента формирование единичного логического сигнала. При

5 увеличении суммы входных сигналов до величины второго пс;рога, напряже1И1е на кор денсаторе 4 уже не будет уменыьап- сл за счет разряда через резистор 7 и генерация импульсов преQ кращается, вследствие чего на выходе .16 элемента формируетс:я нулевой логический сигнал.

Благодаря использованию одних и ij тех же элемс;нтов устройства для контроля ypo.iiHH входных сигналов генерации с гналов, обеспечивается повышение достсзернос: и функционирования г.ри обработке логичесКих сигналов .

Фор.:;/л а и з о бр е т е н и я

.р Двухпороговый логический элемент, содержащий транзистор, резистор :. суммирующие резисторы, о т л и ч а join и и с я тем, что, с повы11;ения достоверности функционирования, в него введены первый, второй и тре конденсаторы, дополнительный резистор, первый и второй вспомогательные резисторы, первый и второй диоды стабилитрон, вспомогат«гльный транзистор и вспомогательный р-п-р

55 транзистор, которого соедине с эмиттером вспомогательного п-р-п транзистора, база которого соединена с общей шиной, которая соединена с катодом первого диода,, через первый

и® конденсатор - с коллектором вспомогательного п-р-п транзистора, через второй конденсатор - с выходом двухпорогового логического элемента и анодом второго диода и Через резне6S,Top - с катодом второго длода, который через третий конденсатор соединен с эмиттером транзистора, который через дополнительньлй резистор соединен с коллектором вспомогательного п-р-п транзистора и анодом стабилитрона, которЕЛй через суммирующие резисторы соединен с входами двухпорогового логического элемента, катод стабилитрона соединен с анодом первого диода и через первый вспомогательный резистор с отрицательным полюсом источника питания, который соединен с коллектором транзистора и через

второй вспомогательный резистор с Вазой транзистора, которая соединена с коллектором вспомогательного р-п-р транзистора.

Источники информации, принятые во внимание при экспертизе

223853V кл. Н 03 К 19/08, 1968 (прототип).

Авторы

Даты

1983-01-23—Публикация

1981-03-05—Подача