ИзоЯретение относится к вычислительной технике и дискретной автоматике и может быть использовано в аппаратуре, обработки цифровой информации, телеуправления, автоматики радиоэлектроники.

Известен управляемый делитель частоты, содержащий двоичный счетчик, счетный вход которого подключен к входной шине, элементы И-НЕ, первые входы которых подключены к шине управления, а выходы всех элементов И-НЕ, кроме первого, - к единичным входам соответствующих триггеров двоичного счетчика, и триггер управления, нулевой вход которого подключен к входной шине, а единичный выход - ко еторым входам элементов И-НЕ 1.

Недостатком такого устройства является невысокое быстродействие, обусловленное влиянием задержек переключения в цепи обратной связи.

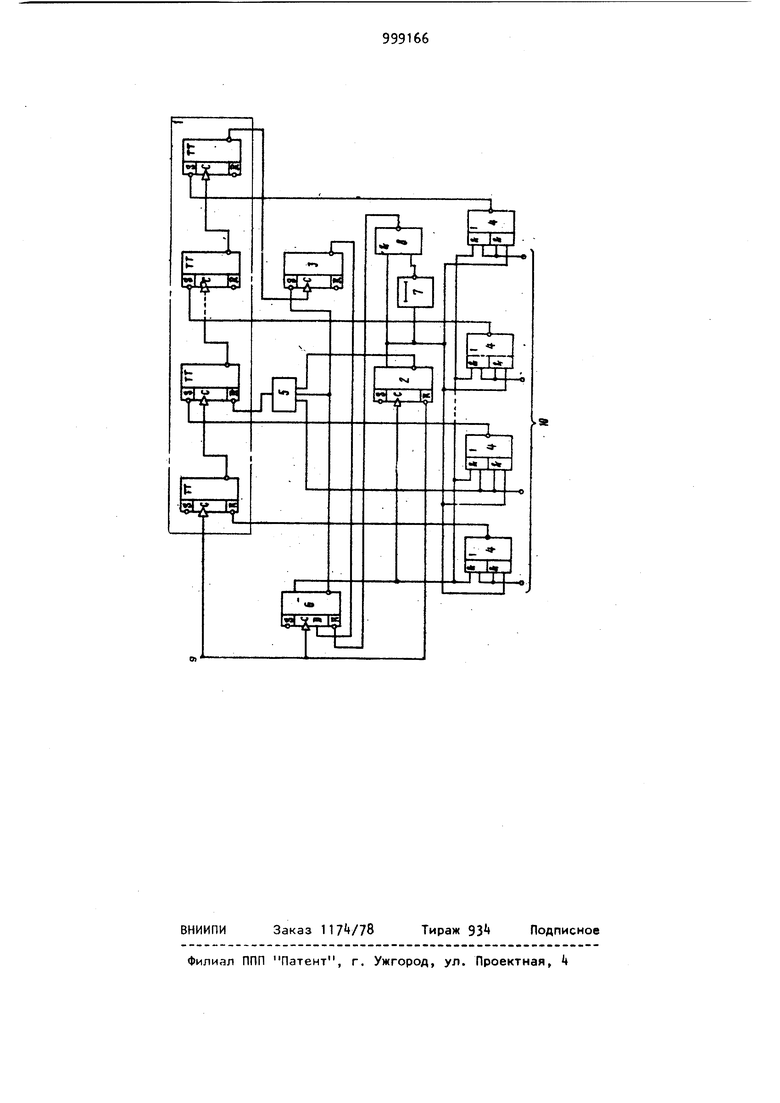

Наиболее близок к изобретению управляемый делитель частоты, содержащий двоичный счетчик, счетный вход которого подключен к входной шине, элементы И-НЕ, первые входы которых подключены к шине управления, а выходы всех элементов И-НЕ, кроме первого, - к единичным входам соответствующих триггеров двоичного счетчи,Q ка, триггер управления, нулевой вход которого подключен к входной шине, а единичный выход - к вторым входам элементов И-НЕ, дополнительный три|- гер и элемент ИЛИ, первыйвход к.о,5 торого соединен с шиной управления второго-разряда двоичного счетчика, второй вход - с нулевым выходом триггера управления и с единичным входом дополнительного триггера, а выход 20 с нулевым входом триггера второго разряда двоичного счетчика, при этом выход первого элемента И-НЕ соединен с нулевым входом триггера первого сигнал обратной связи, который, воздействуя на четвертые входы всех разрядных элементов 2И-ИЛИ-НЕ t, дублирует действие первичного сигна ла обратной связи с единичного выхо да триггера 6. Одновременно под воз действием положительного фронта, фор мирующегося на единичном выходе три гера 2, на выходе элемента И-НЕ 8 на чинается формирование сигнала логического О, который, спустя время ап переключает триггер 6 в состоя ние О, при этом действие первичного сигнала обратной связи прекращает .ся, но те из элементов 2И-ИЛИ-НЕ k, на которые с шин 10 был подан уровень логической 1, продолжают уже под действием вторичного сигнала обратной связи уровнем логического О устанавливать соответствующие тоиггера счетчика 1 в состояние 1, Таким образом, запись соответствующего двоичного кода с шин 10 в счетчик 1 произойдет спустя примерно 95 НС после прихода переднего фронта входного импульса (40.нс на срабатывание триггера 6, 15 не на срабатывание элемента 2И-ИЛИ-НЕ k и АО НС на запись кода управления в счетчик 1). Если при этом принять, что длительность паузы между входными импульсами составляет 0 не (время срабатывания D-триггера по R-BXOду), то период входного имИульса при этом .составляет. не, а значит, максимальная граничная частота предлагаемого устройства равна f 7,5 МГц. При окончании первого входного импульса на входной шине 9 появляется сигнал логического О, опрокидывающий триггер 2 в состояние О, при этом сигнал вторичной обратной связи снимается и запись кода управления с шин 10 в счетчик 1 прекращается. Таким образом, к моменту поступления второго входного импульса в счетчике 1 вместо состояния 00...01 устанавливается состояние, соответствующее десятичному числу: Мц+1 , т.е. счетчик 1 пропускает t промежуточных состояний. При поступлении второго входного импульса на счетный вход триггера 6 по входу О подтверждается записанное ранее по входу R состояние логического О, при этом триггер 2 своего состояния не меняет, а кодчисла, записанного в счетчике 1 возрастет на единицу. Воздействие последующих входных импульсов вызывает изменение состояния счетчика 1 в порядке естественного возрастания двоичного числа до значения 11..,11, устанавливаемого () - М входным импульсом. При.этом поступление входных импульсов не вызывает сигналов первичной обратной связи с единичного выхода триггера 6, так как последний блокирован уровнем логического О, поданного на его вход О с нулевого выхода триггера 3Следующий (Кур-|..)-й входной им- пульс переводит счетчик 1 в состояние 00... 00 и положительный фронт импульса с нулевого выхода триггера старшего разряда указанного счет-чика переключает в О триггер 3- На входе D триггера 6 вновь подается уровень логической 1, На этом цикл деления заканчивается и устройство приходит в исходное состояние, Нечетное значение коэффициента деления устанавливается подачей на шины 10 двоичного кода, эквивалентного десятичному числу Мц 2 -Кнеч+2, где - требуемое нечетное значение коэффициента деления. При окончании первого входного импульса счетчик 1 переходит в состояние 00 . . .01 , одновременно переключается и триггер 6, переключающий триггер 2, при этом поочередно появляется сигнал первичной, а затем вторичной обратной связи, под воздействием которых открываются те из элементов 2И-ИЛИ-НЕ k, на входы которых с шин 10 подан уровень логической , 1, что вызывает переключение в О триггера младшего разряда двоичного счетчика 1 (первый элемент 2ИИЛИ-НЕ в момент действия обратной связи всегда открыт, так как при нечетном коэффициенте деления в младшем разряде кода управления присутствует 1); переключение в 1 триггеров тех разрядов счетчика 1, сумма весовых коэффициентов.которых равна 1Мц-1). Таким образом, с момента поступления второго входного импульса в счетчике 1 вместо состояния 00..01 устанавливается состояние, соответствующее десятичному числу Мц-1 2 -Кн+1, т.е. осуществляется про7пуск ()-х промежуточных состояний . В дальнейшем работа устройства протекает аналогично описанному слу чаю для четного коэффициента деления. По окончании К-го входного импульса цикл деления заканчивается и Устройство приходит в исходное состояние. Если код управления М содержит ,., содержит О во втором разряде, то опрокидывание 1 в О триггера младшего разряда счетчика 1 в момент действи обратной связи вызывает недопустимое переключение в 1 триггера вто рого разряда с.четчика 1 . Для исключ ния этого используется элемент 5, к торый открывается в момент дайотБИЛ первичного сигнала обратной связи j. а затем дублируется действием втори ного сигнала обратной связи при наличии О во втором разряде кода уп равления. Вырабатываемый им уровень логического О воздействует на вхо установки О триггера второго разряда двоичного счетчика и блокирует его переключение в 1, При отсутствии сигналов обратной связи или при наличии 1 во второ.; разряде кода управления на зыход;элемента 5 присутствует уровень ло гической 1 и триггер второго да счетчика 1 не блокирован. Введение новых элеме1-г1о-:1 /; сь; ji-. между ними позволяет повысить быстродействие данного устройства, Формула изобретения Управляемый делитель частоты сле дования импульсов, содержащий ный счетчик импульсов, счетный вход которого подключен к нулевому входу триггера управления и входной шине, а выход - к счетному входу триггера сброса, элемент И-НЕ и элемент ИЛИ, первый вход которого соединен с шиной управления второго разряда двоичного счетчика и.шульсов, -зторой вход - с нулевым выходом триггера зпнуляьзуправления, а выход щим входом второго -dOi MHOrO счетчика импульсов ., щ и и с я тем,, что 0 повышения быстродействия. еведены элементы 2И-ИЛИ-НЕ, -задерж ки и входной триггер; -:f ;-, (ЗХОД 7 :-,.,.- :. , которого coe.qHHfiH с ;:; информационный вхсд ходом триггера сброса |-1У.-,еьОЙ ВХОЯ с выходом элеиента И rit: выход - с треТс-.-чм й/со.с-., ИЛИ и единичным входов; 1 f-IJd сбрОса S а единичный - У -;8 Г НЫМ входом триггера уппаэл,-. С пер.::: -:Р -илизыми входами всех 3jicr-.c:НЕ. вторые и TijeTbH .,.:u -:С ; yiiJtlX . -.--нам подключены к соогьег.. ы к едиуправления, четвертые й Рявления J иичному выходу трип-ег Я: :у входу элемента .-.,: ;- входу эленентс: v г ;itOTOpOrC COeOtiH.::--: . - -. дом элемента зaдзp iл; всех эл811ентов 1.V . вого, соединены с ей ii Л ссотеетстиу ощ,;.-. .;, ;: ;ного счетчика ,Г:;-1, . щий вход пераог-о -подключен к выходу - 2И-ИЛИ-НЕ. McrOUi-H iKx: hh.:.,;y;. принятые во sh-tHMaHi-.e пгя3KCI lepTMSc 1,Приборь и систе;-;ы урвзления, 1872 № Ь, с, 30- 3 ; оис, 2. 2. Авторское св :;;еуельстйо СССР W , кл Н 03 : 23/OQ, 28 0.79.

se

| название | год | авторы | номер документа |

|---|---|---|---|

| Управляемый делитель частоты следования импульсов | 1984 |

|

SU1261108A1 |

| Управляемый делитель частоты следования импульсов | 1983 |

|

SU1102043A1 |

| Реверсивный формирователь двоичного кода | 1987 |

|

SU1480123A2 |

| Управляемый делитель частоты | 1976 |

|

SU658741A1 |

| Устройство для формирования серий импульсов | 1983 |

|

SU1177888A1 |

| Устройство выделения одиночного @ -го импульса | 1987 |

|

SU1443146A2 |

| Устройство выделения одиночного @ -го импульса | 1986 |

|

SU1338028A2 |

| Формирователь временного интервала | 1986 |

|

SU1383466A1 |

| Устройство приоритета | 1983 |

|

SU1160413A1 |

| Делитель частоты следования импульсов с регулируемой длительностью импульсов | 1987 |

|

SU1480120A1 |

Авторы

Даты

1983-02-23—Публикация

1981-04-14—Подача