Изобретение относится к электротехнике, в частности к источникам вторичного электропитания систем автоматики и вычислительной технике.

Известны системы электропитания микропроцессорных устройств, содержащее последовательно включенные входной фильтр, регуляторы напряжений, нерегулируемый преобразователь напряжений, трансформатор, выходные выпрямители и фильтры, установленные на шинах питания микропроцессорных устройств [1; 2] .

Недостатком таких систем является малая помехозащищенность и невысокая надежность, обусловленные взаимным влиянием каналом питания микропроцессорных устройств. Кроме того, необходимо устанавливать дополнительные сглаживающие фильтры, что приводит к повышению импульсного тока в питающей сети, что, в свою очередь, увеличивает уровень кондуктивных и индуктивных помех.

Наиболее близким к заявляемому по технической сущности и достигаемому результату решением, которое может быть принято за прототип, является система электропитания микропроцессорных устройств, содержащая последовательно включенные блоки сетевых фильтров, блоки переключения, понижающий трансформатор и блок выпрямителей, выходы которого через компенсационные стабилизаторы соединены с шинами питания микропроцессорных устройств [3] .

Основные недостатки данной системы питания состоят в невысокой надежности и помехозащищенности, что обусловлено возникновением ситуации несогласованного поступления напряжения по различным каналам питания микропроцессорных устройств. Это понижает надежность системы питания в целом. При этом существующие методы согласования подачи напряжений, основанные на логическом контроле, обладает невысокой помехозащищенностью. Кроме этого, прототип и известные аналоги не обеспечивают живучесть системы питания (например, самовосстанавливаемость при сбоях по питанию - как по сетевому, так и по выходному напряжению), не устраняют возможность появления перенапряжений, обладают собственными большими кондуктивными и индуктивными помехами.

Цель изобретения - повышение надежности и помехоустойчивости электропитания микропроцессорных устройств управления многодвигательными приводами.

Это достигается тем, что в известную систему электропитания микропроцессорных устройств, содержащую последовательно включенные блок сетевых фильтров, блок переключения, понижающий трансформатор и блок выпрямителей, выходы которого соединены с силовыми входами компенсационных стабилизаторов первой ступени стабилизации, блоки аварийной сигнализации и микропроцессорное устройство с шинами питания и управления, введены компенсационные стабилизаторы второй ступени стабилизации по числу компенсационных стабилизаторов первой ступени стабилизации, три блока контроля максимально допустимых напряжений, три блока контроля минимально допустимых напряжений, два блока контроля перекоса напряжений, три блока отсечки напряжений, первый и второй логические элементы ИЛИ, блок формирования временных задержек, блок формирования сигналов отключения, блок формирования защитных импульсов и блок формирования служебных сигналов, первый вход которого объединен с первыми входами блоков аварийной сигнализации, с первыми входами первого и второго логических элементов ИЛИ, с первым входом блока формирования защитных импульсов, управляющими входами блоков контроля минимально допустимых напряжений и соединен с силовым выходом первого компенсационного стабилизатора второй ступени стабилизации, силовые входы и управляющие выходы компенсационных стабилизаторов второй ступени стабилизации соединены соответственно с силовыми выходами и управляющими входами компенсационных стабилизаторов первой ступени стабилизации, управляющие входы второго, третьего и четвертого компенсационных стабилизаторов напряжений второй ступени стабилизации соединены соответственно с выходами первого, второго и третьего блоков отсечки напряжений, входы которых соединены с первыми выходами соответственно первого, второго и третьего блоков контроля максимально допустимых напряжений, вторые выходы которых соединены соответственно с вторым, третьим и четвертым входами первого логического элемента ИЛИ, первый выход которого соединен с вторым входом блока формирования защитных импульсов, третий вход которого соединен с первым выходом второго логического элемента ИЛИ, второй, третий и четвертый входы которого соединены соответственно с выходами первого, второго и третьего блоков контроля минимально допустимых напряжений, входы которых объединены соответственно с входами первого, второго и третьего блоков контроля максимально допустимых напряжений и подключены к силовым выходам второго, третьего и четвертого компенсационных стабилизаторов второй ступени стабилизации и к первой, второй, третьей шинам питания микропроцессорного устройства, шина управления которого соединена с выходом блока формирования служебных сигналов, второй вход которого соединен с первым выходом блока формирования защитных импульсов, третий вход объединен с управляющим входом блока формирования защитных импульсов и подключен к выходу блока формирования временных задержек, первый вход которого соединен с первым выходом формирователя сигналов отключения, второй выход которого соединен с управляющим входом блока переключения, первый вход - с вторым выходом блока формирования защитных импульсов, а второй вход объединен с вторым входом блока формирования временных задержек и соединен с выходом блока выпрямителей, первые входы блоков контроля перекоса напряжений объединены соответственно с входами первого и второго блоков контроля минимально допустимых напряжений и соединены соответственно с силовыми выходами второго и третьего компенсационных стабилизаторов второй ступени стабилизации, вторые входы первого и второго блоков контроля перекоса напряжений соединены соответственно с силовыми выходами третьего и четвертого компенсационных стабилизаторов второй ступени стабилизации, выходы первого и второго блоков контроля перекоса напряжений соединены с управляющими входами второго и третьего блоков контроля максимально допустимых напряжений соответственно, вторые входы блоков аварийной сигнализации соединены с вторыми входами соответственно первого и второго логических элементов ИЛИ.

Предложение позволяет исключить ситуации несогласованной запитки микропроцессорных устройств, обеспечивая высокую помехозащищенность за счет реализации зависимой амплитудно-частотно-широтной импульсной модуляции напряжений на второй ступени стабилизации. При этом существенно повышается живучесть системы электропитания.

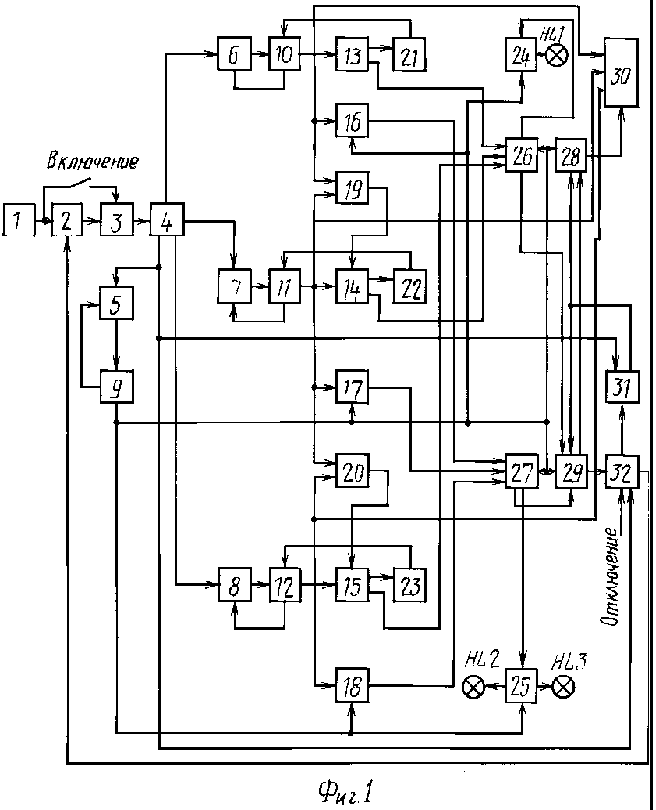

На фиг. 1 представлена структурная схема предлагаемой системы; на фиг. 2 - временные диаграммы взаимодействия блоков системы.

Система электропитания микропроцессорных устройств (МПУ) содержит последовательно включенные блок 1 сетевых фильтров, блок 2 переключения, понижающий трансформатор 3, блок 4 выпрямителей, выходы которого соединены с силовыми входами компенсационных стабилизаторов 5-8 первой ступени стабилизации, силовые выходы которых соответственно соединены с силовыми входами компенсационных стабилизаторов 9-12 второй ступени стабилизации. Кроме этого, предлагаемая система питания содержит три блока 13-15 контроля максимально допустимых напряжений, три блока 16-18 контроля минимально допустимых напряжений, два блока 19 и 20 контроля перекоса напряжений, три блока 21-23 отсечки напряжений, два блока 24 и 25 аварийной сигнализации, первый 26 и второй 27 логические элементы ИЛИ, блок 28 формирования служебных сигналов, блок 29 защитных импульсов, микропроцессорное устройство 30, блок 31 формирования временных задержек и блок 32 формирования сигналов отключения.

При этом первый вход блока 28 объединен с первыми входами блоков 24 и 25, с первыми входами логических элементов ИЛИ 26 и 27, с первым входом блока 29, управляющими входами блоков 16-18 и соединен с силовыми выходами стабилизатора 9, силовые входы и управляющие выходы стабилизаторов 9-12 соединены с силовыми выходами и управляющими входами стабилизаторов 5-8, управляющие входы стабилизаторов 10-12 соединены соответственно с выходами блоков 21-23, входы которых соединены с первыми выходами блоков 13-15, вторые выходы которых соединены соответственно с вторым, третьим и четвертым входами первого логического элемента ИЛИ 26, первый выход которого соединен с вторым входом блока 29, третий вход которого соединен с первым выходом второго логического элемента ИЛИ 27, второй, третий и четвертый входы которого соединены соответственно с выходами первого, второго и третьего блоков 16-18, входы которых объединены соответственно с входами первого, второго и третьего блоков 13-15 и подключены к силовым выходам второго, третьего и четвертого стабилизаторов 10-12 второй ступени стабилизации и к первой, второй, третьей шинам питания микропроцессорного устройства 30, шина управления которого соединена с выходом блока 28, второй вход которого соединен с первым выходом блока 29, третий вход объединен с управляющим входом блока 29 и подключен к выходу блока 31, первый вход которого соединен с первым выходом блока 32, второй выход которого соединен с управляющим входом блока 2, первый вход - с вторым выходом блока 29, а второй вход блока 32 объединен с вторым входом блока 31 и соединен с выходом блока 4 выпрямителей, первые входы блоков 19 и 20 объединены соответственно с входами первого и второго блоков 16 и 17 и соединены соответственно с силовыми выходами второго и третьего компенсационных стабилизаторов 10 и 11 второй ступени стабилизации; вторые входы блоков 19 и 20 соединены соответственно с силовыми выходами третьего и четвертого компенсационных стабилизаторов 11 и 12 второй ступени стабилизации; выходы первого и второго блоков 19 и 20 соединены с управляющими входами второго и третьего блоков 14 и 15 соответственно; вторые входы блоков 24 и 25 соединены с вторыми выходами соответственно первого 26 и второго 27 логических элементов ИЛИ; на выход первого блока 24 подключена сигнализация "НLI", на первый выход второго блока 25 - сигнализация "НL2", а на второй выход - сигнализация "НL3".

Количество каналов стабилизации должно быть равно по крайней мере (как минимум) трем, т. е. минимальное число стабилизаторов первой и второй ступени - три. Пример реализации дан на четыре канала. Соответственно блоков 13-15, блоков 16-18 и блоков 21-23 - на единицу меньше.

Система питания микропроцессорных устройств работает следующим образом.

При подаче напряжения на блок 1 сетевых фильтров отфильтрованное напряжение поступает на силовой вход блока 2 переключения. Затем осуществляется "принудительная" подача напряжения непосредственно на вход понижающего трансформатора 3, с выхода которого пониженное переменное напряжение поступает на блок 4 выпрямителей. Выпрямленное напряжение подается на силовые входы компенсационных стабилизаторов 5-8 первой ступени, силовые выходы которых соединены с соответствующими силовыми входами компенсационных стабилизаторов 9-12 второй ступени стабилизации. Полученные стабилизированные напряжения с выходов второй ступени стабилизации подаются на соответствующие шины питания микропроцессорного устройства 30 и одновременно на входы блоков контроля максимально допустимых и минимально допустимых напряжений, т. е. соответственно на входы блоков 13-15 и 16-18. Напряжение второй ступени стабилизации компенсационных стабилизаторов 10 и 11 подается соответственно на первый и второй входы первого блока 19 контроля перекоса напряжений. На входы второго блока 20 контроля перекоса напряжений подается напряжение с силовых выходов компенсационных стабилизаторов 11 и 12. При этом в случае перекоса контролируемых напряжений по уровню на выходах блоков 19 и 20 формируется управляющий сигнал, который подается на соответствующие управляющие входы блоков 14 и 15, с первого выхода которых запускаются блоки 22 и 23 соответственно, каждый из которых выполнен на базе силовых ключей. Блоки 22 и 23 поддерживают напряжения второй ступени стабилизации на заданном уровне. Любое отклонение напряжения питания микропроцессорного устройства 30 приводит к формированию сигналов на выходе элементов ИЛИ: 26 - при отклонении по Umax (на временной диаграмме фиг. 2 "Выход 26 вход 29"); 27 - при отклонении по Umin (на временной диаграмме фиг. 2 "Выход 27 вход 29"). С первых выходов этих элементов поступают сигналы соответственно на второй и третий входы блока 29, на управляющий вход которого подается проинтегрированный сигнал контроля защиты с выхода блока 3 (на временной диаграмме фиг. 2 "Выход блока 31"). На первый вход блока 31 поступают сигналы отключения с первого выхода блока 32 формирования сигналов отключения (на временной диаграмме фиг. 2 "Выход 32 вход 31"). По сигналам работы блоков 29 и 31 осуществляется выработка служебных сигналов блоком 28 для микропроцессорного устройства 30 (на временной диаграмме фиг. 2 "Выход блока 28").

Преимущество предлагаемой системы питания состоит в том, что она обеспечивает защиту микропроцессорных устройств не только от возможных всплесков перенапряжений по входу, но полностью исключает возможность перекоса напряжений питания как по амплитуде, так и по фазе. Это обеспечено за счет того, что в заявленном техническом решении реализована новая функция, состоящая в формировании зависимой амплитудно-частотно-широтной импульсной модуляции напряжений второй ступени стабилизации. При этом совмещены основные достоинства непрерывных и импульсных стабилизаторов напряжения. В сопоставлении с базовым объектом (системой питания прототипа) предлагаемая система питания на порядок уменьшает импульсные всплески нагрузки в питающей сети. Исключается необходимость отключения системы питания на 20 с после срабатывания защиты от перенапряжения. Устранены необходимость обеспечения нагрузки питания до 0,4 А на канале питания для обеспечения нормальной работы.

Реализация предлагаемой системы питания показала ее высокую эффективность, особенно в системах микропроцессорного управления многодвигательными приводами в условиях наличия ударной нагрузки и высоких (до 50% ) перепадов сетевого напряжения.

Применение предлагаемой системы электропитания микропроцессорных устройств, например, на регулируемом электроприводе бумагоделательных машин с микропроцессорным управлением, увеличивает его надежность и уменьшает вероятность обрывов бумажного полотна. (56) 1. Конев Ю. И. и др. Микроэлектронные электросистемы. Применения в радиоэлектронике. М. : Радио и связь, 1987, с. 93-97.

2. Патент ЕПВ N 0250932, кл. G 05 F 1/569, 1986.

3. Технико-эксплуатационная документация системы питания ZM-55, Завод компьютерных устройств СЕРА-ЭЛЬЗАБ, 41-813, Zabrze, ПР, N 21705, 1989.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ УПРАВЛЕНИЯ МАГНИТНО-ТРАНЗИСТОРНЫМ КЛЮЧОМ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1989 |

|

RU2006180C1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ЭЛЕКТРОПРИВОДОМ | 1992 |

|

RU2035840C1 |

| СПОСОБ ФОРМИРОВАНИЯ ТРЕХФАЗНОГО НАПРЯЖЕНИЯ, ПОДВОДИМОГО К АСИНХРОННОМУ ЭЛЕКТРОДВИГАТЕЛЮ ПРИ ПИТАНИИ ЕГО ОТ ОДНОФАЗНОЙ СЕТИ | 1992 |

|

RU2017318C1 |

| Устройство для стабилизированного питания приемников энергии | 1987 |

|

SU1545290A1 |

| Развязывающее устройство | 1990 |

|

SU1802916A3 |

| Датчик состояния вентилей реверсивного тиристорного преобразователя | 1991 |

|

SU1787303A3 |

| Устройство для управления тиристорами переключателя питания @ -фазной нагрузки переменного напряжения | 1982 |

|

SU1320865A1 |

| Устройство для управления синхронным электродвигателем | 1988 |

|

SU1621134A1 |

| Преобразователь постоянного напряжения в переменное | 1986 |

|

SU1390750A1 |

| Способ преобразования постоянного напряжения в квазисинусоидальное и устройство для его осуществления | 1981 |

|

SU1023590A1 |

Использование: для электропитания систем автоматики и вычислительной техники. Сущность изобретения: система электропитания содержит последовательно включенные блок сетевых фильтров, блок переключения, понижающий трансформатор, блок выпрямителей, компенсационные стабилизаторы первой ступени, блоки аварийной сигнализации и микропроцессорный блок. В систему введены компенсационные стабилизаторы второй ступени, охваченные зависимой обратной связью. Эта связь реализована на основе включения блоков контроля минимально 5 и максимально допустимых напряжений, управляемых от блока контроля перекоса напряжений. Такое построение схемы повышает надежность и помехоустойчивость электропитания. 2 ил.

СИСТЕМА ЭЛЕКТРОПИТАНИЯ, содержащая последовательно включенные блок сетевых фильтров, блок переключения, понижающий трансформатор и блок выпрямителей, выход которого соединен с силовыми входами компенсационных стабилизаторов первой ступени стабилизации, блоки аварийной сигнализации и микропроцессорный блок с шинами питания и управления, отличающаяся тем, что, с целью повышения надежности и помехоустойчивости электропитания, в нее введены компенсационные стабилизаторы второй ступени стабилизации по числу компенсационных стабилизаторов первой ступени стабилизации, три блока контроля максимально допустимых напряжений, два блока контроля перекоса напряжений, три блока отсечки напряжений, первый и второй логические элементы ИЛИ, блок формирования служебных сигналов, блок формирования защитных импульсов, блок формирования временных задержек и блок формирования сигналов отключения, при этом первый вход блока формирования служебных сигналов объединен с первыми входами первого и второго логических элементов ИЛИ, с первым входом блока формирования защитных импульсов, с управляющими входами блоков контроля минимально допустимых напряжений и соединен с силовым выходом первого компенсационного стабилизатора второй ступени стабилизации, силовые входы и управляющие выходы компенсационных стабилизаторов второй ступени стабилизации соединены соответственно с силовыми выходами и управляющими входами компенсационных стабилизаторов первой ступени стабилизации, управляющие входы второго, третьего и четвертого компенсационных стабилизаторов напряжений второй ступени стабилизации соединены соответственно с выходами первого, второго и третьего блоков отсечки напряжений, входы которых соединены с первыми выходами соответственно первого, второго и третьего блоков контроля максимально допустимых напряжений, вторые выходы которых соединены соответственно с вторым, третьим и четвертым входами первого логического элемента ИЛИ, первый выход которого соединен с вторым входом блока формирования защитных импульсов, третий вход которого соединен с первым выходом второго логического элемента ИЛИ, второй, третий и четвертый входы которого соединены соответственно с выходами первого, второго и третьего блоков контроля минимально допустимых напряжений, входы которых объединены соответственно с входами первого, второго и третьего блоков контроля максимально допустимых напряжений и подключены к силовым выходам второго, третьего и четвертого компенсационных стабилизаторов второй ступени стабилизации и к первой, второй и третьей шинам питания микропроцессорного блока, шина управления которого соединена с выходом блока формирования служебных сигналов, второй вход которого соединен с первым выходом блока формирования защитных импульсов, третий вход объединен с управляющим входом блока формирования защитных импульсов и подключен к выходу блока формирования временных задержек, первый вход которого соединен с первым выходом блока формирования сигналов отключения, второй выход которого соединен с управляющим входом блока переключения, первый вход - с вторым выходом блока формирования защитных импульсов, а второй вход объединен с вторым входом блока формирования временных задержек и соединен с выходом блока выпрямителей, первые входы блоков контроля перекоса напряжений объединены соответственно с входами первого и второго блоков контроля минимально допустимых напряжений и соединены соответственно с силовыми выходами третьего и четвертого компенсационных стабилизаторов второй ступени стабилизации, выходы первого и второго блоков контроля перекоса напряжений соединены с управляющим входами второго и третьего блоков контроля максимально допустимых напряжений соответственно, вторые входы блоков аварийной сигнализации соединены с вторыми входами соответственно первого и второго логических элементов ИЛИ.

Авторы

Даты

1994-01-15—Публикация

1990-12-25—Подача