Изобретение отноcитcя к вычислительной технике, в частности к цифровым устройствам сравнения.

Известно устройство сравнения (1), которое содержит сумматор, регистр, счетчик, элементы И и соответствующие связи.

Наиболее близким является устройство для сравнения чисел (2), принятое за прототип, в котором оба числа и величина допуска задаются параллельными кодами. Это устройство состоит из сумматора, элемента И, к элементов ИЛИ, где k - максимальная разность допуска, n - k+1 элементов НЕ, к элементов ИЛИ-НЕ, элемент задержки и D-триггер, причем выход переноса старшего разряда сумматора подключен непосредственно к первому входу первого элемента И и через элемент НЕ - к первому входу второго элемента И, выходы элементов И являются выходами неравенства устройства, выходы разрядов первого числа устройства с (k+1)-го по n-й подключены к входам первой группы сумматора с (k+1)-го по n-й соответственно, выходы разрядов второго числа устройства с (k+1)-го по n-й подключены к входам второй группы сумматора с (k+1)-го по n-й соответственно, прямой выход триггера является выходом равенства устройства, инверсный выход соединен с вторыми входами элементов И, синхронизирующий выход соединен с выходом переноса старшего разряда сумматора, информационный - с выходом логической единицы устройства, а выход установки в нулевое состояние является входом начальной установки устройства и соединен с входом переноса младшего разряда сумматора и через элемент задержки - с третьими входами элемента И, первые входы элементов ИЛИ и элементов ИЛИ-НЕ соединены с входами к младших разрядов соответственно первого и второго чисел устройства, вторые входы одноименных элементов ИЛИ и ИЛИ-НЕ объединены и подключены к входам допусков соответствующих разрядов устройства, выходы элементов ИЛИ подключены к соответствующим входам второй группы сумматора, выходы которого являются информационными выходами устройства.

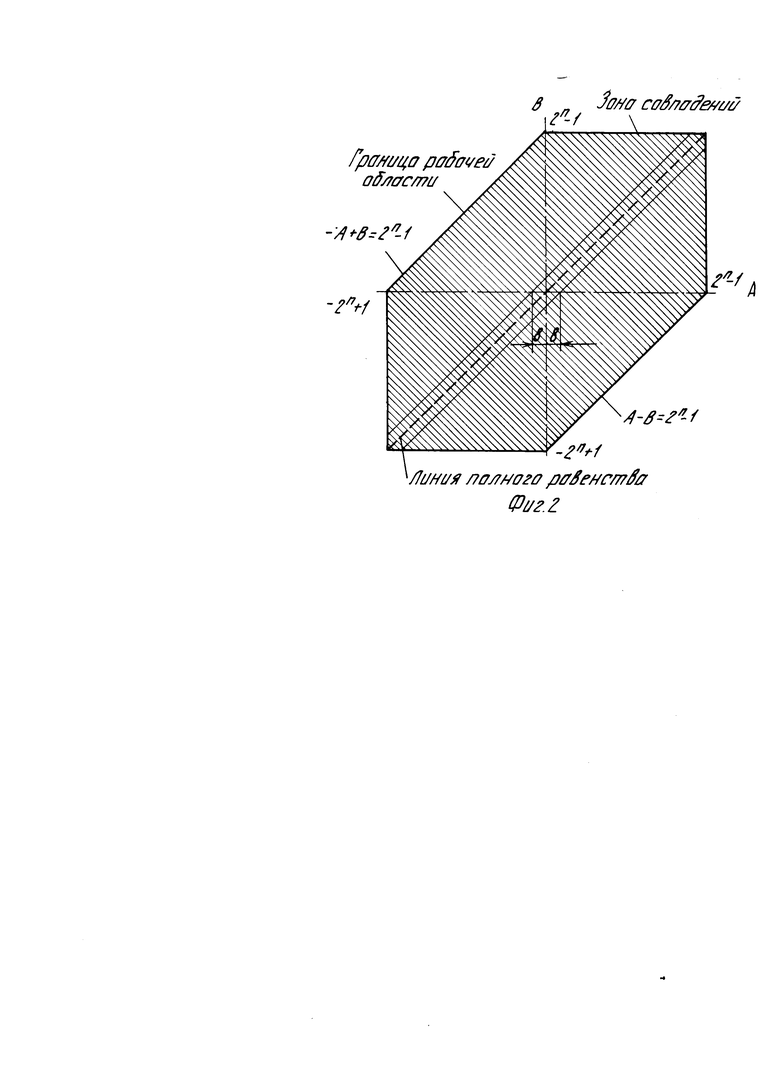

Существенным недостатком этого устройства сравнения является то, что зона допустимых значений, задаваемая путем исключения из сравнения младших разрядов обоих чисел, не остается одной и той же ширины для любых их сочетаний. Эта зона показана на фиг. 3. По сторонам рисунка показаны возможные значения сравниваемых чисел, а во внутренних клеточках даны абсолютные значения разностей (А-В). Видно, что если выведен из сравнения один младший разряд, то зона допуска состоит из четырехклеточных квадратов, в которых абсолютные величины разностей равны 0 или 1. Однако клетки, содержащие 1, имеются и за пределами зоны допуска (совпадений). Например, для А= 0100, В= 0011, А-В= 0001, но устройство сравнения будет выдавать сигнал несовпадения, а при А= 0011 и В= 0010, где А-В= 0001, устройство выдаст сигнал совпадения.

Зона допуска очень сильно возрастает при увеличении числа несравниваемых младших разрядов. Так, если этих разрядов два, то зона допуска состоит из квадратов, содержащих по 16 клеток, в которых записаны абсолютные величины разностей 0 до 3. Видно, что за границами зоны допуска тоже есть клетки, содержащие 1,2 и 3. Следующий шаг, т. е. исключение из сравнения трех младших разрядов, приводит к появлению зоны допуска, состоящей из квадратов, содержащих по 64 клетки с абсолютными значениями разностей от 0 до 7. За пределами зоны допуска имеются клетки с абсолютными значениями разности от 1 до 7, сочетаниях А и В, которые устройство будет считать несовпавшими.

Установить зоны допуска, содержащие 0,1,2 или 0,1,2,3,4 или 0,1,2,3,4,5, или 0,1,2,3,5,6, это устройство не позволяет. Таким образом, недостатком является также и грубое задание зоны допуска.

Устройство, принятое за прототип, не позволяет учитывать знаки сравниваемых чисел, что является еще одним его недостатком.

Целью изобретения является повышение точности и быстродействия устройства сравнения.

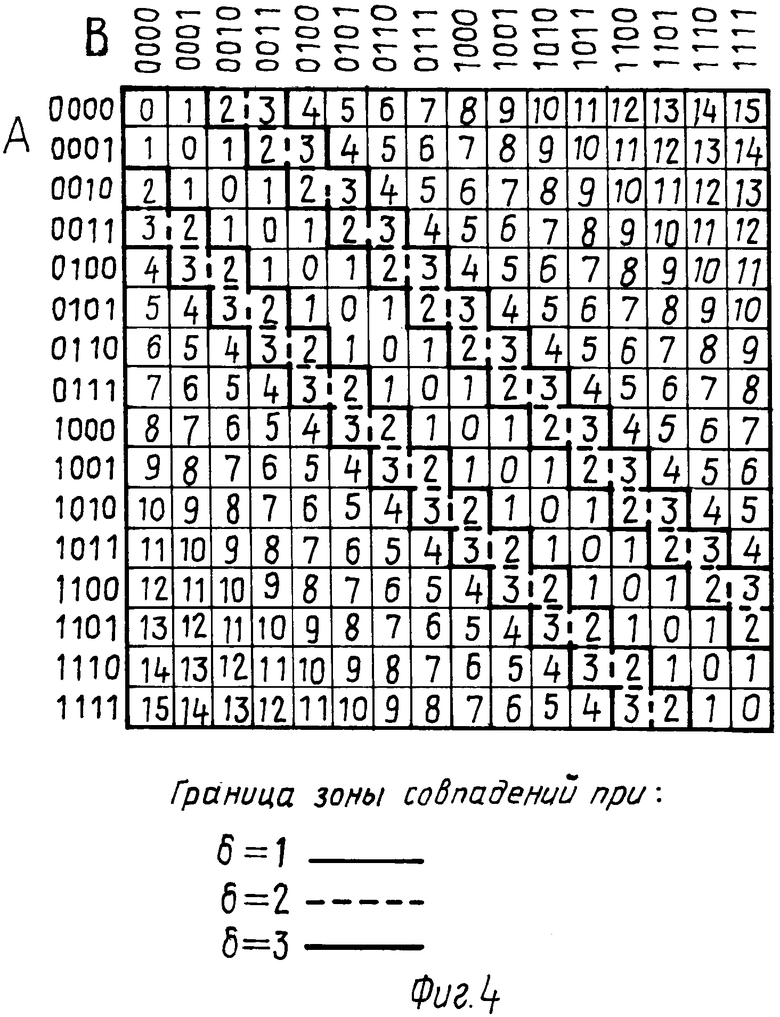

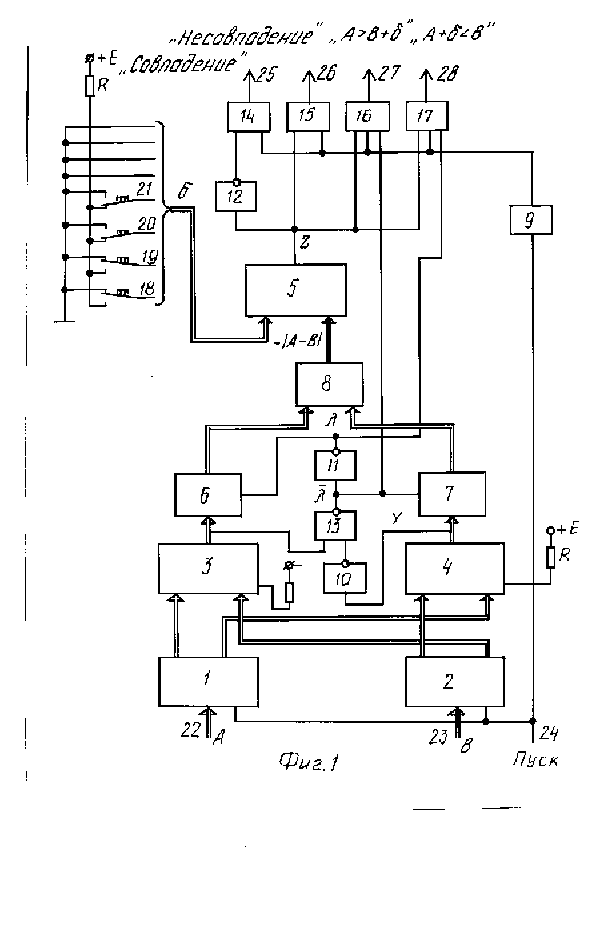

На фиг. 1 изображено устройство сравнения чисел, функциональная схема; на фиг. 2 - рабочая область устройства сравнения; на фиг. 3 - границы зоны совпадений устройства, принятого за прототип; на фиг. 4 - граница зоны совпадений предлагаемого устройства при n+1= 4.

Устройство для сравнения чисел (см. фиг. 1) содержит регистры 1,2 сумматоров 3,4,5, две группы элементов И 6,7, группы элементов ИЛИ 8, элемент задержки 9, элементы НЕ 10, 11, 12, элемент И-НЕ 13, элементы И 14-17.

Регистры 1 и 2 могут быть созданы на базе серийных микросхем К155ТМ8, сумматоры 3,4 и 5 на базе К155ИМЗ.

Работает устройство сравнения следующим образом. На входы 18 и 19 поступают сравниваемые коды А и В, а на входы 21 - потенциальный код, соответствующий допустимому расхождению кодов δ . Далее подается импульсный сигнал ПУСК на вход 20. В результате сравнения на выходах 22 и 23 появляются в противофазе два сигнала: "НЕСОВПАДЕНИЕ" и "СОВПАДЕНИЕ", один из которых равен "1", а другой "0". На выходе 24 появляется сигнал высокого уровня, если А > В + δ , а на выходе 25 - если А + δ < В.

Сравниваемые двоичные коды состоят из n+1 бита (старший бит - знаковый) и могут быть

- числами одного знака, не превышающими 2n-1, | А| ≅ 2n-1 и | В| ≅ 2n-1;

числами разных знаков, у которых сумма модулей превышает 2n-1, т. е.

| А| + | В| ≅ 2n-1

Величина допустимого расхождения δ ограничена

0 ≅ δ ≅ 2n-1.

На фиг. 1 и 2 для определенности принято n+1= 8, т. е. 2n-1= 127.

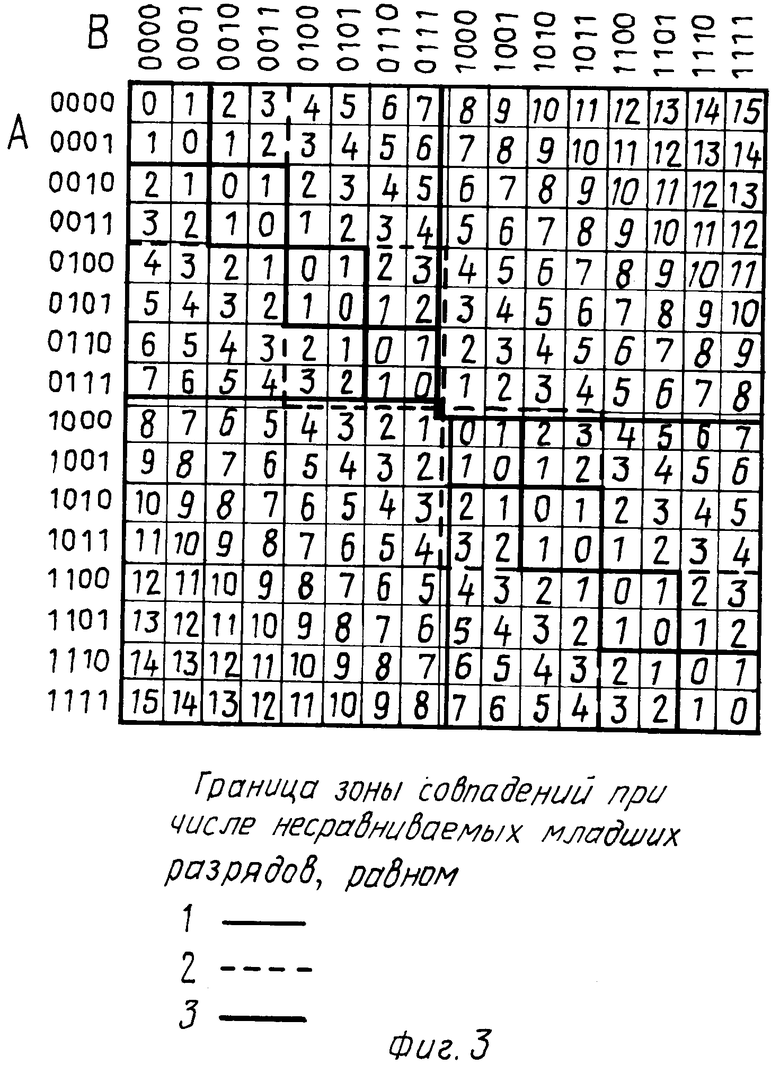

На фиг. 2 показана рабочая область устройства сравнения, которая имеет вид шестиугольника и для наглядности заштрихована.

Штриховой линией обозначена линия полного равенства, являющаяся геометрическим местом сочетаний значений А и В при δ = 0. Задание δ , отличного от нуля, выделяет в рабочий области полосу шириной в 2δ , которая является геометрическим местом сочетаний значений А и В при 0 ≅ δ ≅ 2n-1. Это зона совпадений, где | А-В| ≅ δ , для которой устройство сравнения выдает сигналы

СОВПАДЕНИЕ = 1 и

НЕСОВПАДЕНИЕ = 0.

Сочетания значений А и В, лежащие выше и ниже зоны совпадений, соответствуют несовпадению А и В, т. е. выполнению условия | А - В| > δ , при котором устройство сравнения выдает сигналы

СОВПАДЕНИЕ = 0 и

НЕСОВПАДЕНИЕ = 1.

Сигнал, равный "1", появляется на выходе 24 в случае, когда А-В > δ, а на выходе 25, когда В-А > δ.

Положительный числа подаются на входы 18 и 19 в прямом двоичном коде, а отрицательные - в обратном двоичном коде.

Если обозначить обратный код штрихом, то справедливы следующие соотношения:

А1 = 2n-А

В1 = 2n-В

Отсюда вытекает справедливость и обратных соотношений:

А= 2n-А1

В= 2n-В1.

В сумматоре 3 суммируется А+Воб+1, а в сумматоре 4 суммируются В+Аоб+1 и получаются соответственно разности: на выходе сумматора 3А-В, а на выходе сумматора 4В-А. Единицы, необходимые для превращения в сумматоре 3 обратного кода Воб в дополнительный Вl , а в сумматоре 4 обратного кода Аоб в дополнительный Аl , получаются со входов переноса, на которые поступают сигналы, соответствующие логическим "единицам".

При поступлении на вход 20 сигналы ПУСК коды А и В со входов 18 и 19 заносятся в регистры 1 и 2.

Рассмотрим случай, когда оба кода А и В прямые, т. е. соответствуют положительным числом. Тогда коды на инверсных выходах триггеров этих регистров будут обратными кодами Аоб и Воб. В сумматоре 3 выполняется операция

А+Воб+1

а в сумматоре 4 - операция

В+Аоб. +1,

где единицы возникают за счет сигнала переноса.

В результате на выходе сумматора 3 появляется код разности А-В, а на выходе сумматора 4 - код разности В-А.

Один из этих кодов будет отрицательным, т. е. содержать единицу в знаковом разряде, либо оба кода будут равны нулю, если А= В, и тогда в знаковых разрядах будут нули.

Обозначив знаковый разряд разности А-В через Х, а знаковый разряд разности В-А через λ , получим на выходе элемента НЕ 11 сигнал λ , равный

λ=  ˙ Y.

˙ Y.

Сигнал λ определяет, какая из разностей А-В или В-А меньше нуля. Если А-В<0, то λ = 1 ;  = 0. Группа элементов И 6 открывается и пропускает дополнительный код этой разности через блок элементов ИЛИ 8 на вход первого слагаемого сумматора 5. Если В-А ≅ 0, то λ = 0, а

= 0. Группа элементов И 6 открывается и пропускает дополнительный код этой разности через блок элементов ИЛИ 8 на вход первого слагаемого сумматора 5. Если В-А ≅ 0, то λ = 0, а  = 1 и дополнительный код (В-А) или нулевой код поступает через группу элементов ИЛИ 8 на вход первого слагаемого сумматора 5. Таким образом, логическая схема, состоящая из элементов 10, 13 и 11 и группы элементов 6 и 7 совместно с блоком логических элементов ИЛИ 8, выполняют операцию вычисления

= 1 и дополнительный код (В-А) или нулевой код поступает через группу элементов ИЛИ 8 на вход первого слагаемого сумматора 5. Таким образом, логическая схема, состоящая из элементов 10, 13 и 11 и группы элементов 6 и 7 совместно с блоком логических элементов ИЛИ 8, выполняют операцию вычисления

-| А-В |

На вход 21 может быть подан потенциальный прямой код желательного δ . Старшие разряды кода равны всегда нулю. Их число зависит от конкретного применения.

Отрицательный модуль разности А-В на входе сумматора 5 представлен в дополнительном коде. Поэтому сумматор выдает на выход разность

δ - | А-В| ,

из которой используется только знаковый разряд Z, который равен единице, в случае, если

δ- | А-В| < 0

Это возможно, когда

δ -(А-В) < 0

либо когда δ -(В-А) < 0.

Если δ -(А-В) < 0, то А-В > 0 и λ = 1, а если δ - (В-А) < 0, то В-А > 0 и λ = 0.

Когда λ -| А-В| ≥ 0, Z = 0 и на выходе элемента НЕ 12 сигнал равен единице. Это возможно в трех случаях

δ > А-В

δ> В-А

и А= В, т. е. δ > 0.

Сигнал ПУСК, задержанный на время, достаточное для завершения переходных процессов в элементах 1-8, 10-13, поступает на вторые входы логических элементов 14-17 в виде сигнала Т.

Логический элемент И 14 выдает сигнал

СОВПАДЕНИЕ =  ˙ T

˙ T

Логический элемент И 15 выдает сигнал

НЕСОВПАДЕНИЕ = Z ˙ T

Логический элемент 16 выдает сигнал

А > В + δ =  ˙ Z ˙ T

˙ Z ˙ T

Логический элемент 17 выдает сигнал

А+ δ< В= λ˙ Z˙ T

Если А и В меньше нуля, то они должны быть представлены на входах 18 и 19 в дополнительном коде. При этом на инверсных выходах триггеров регистров 1 и 2 возникнут коды обратные по отношению к входным кодам. В сумматорах 3 и 4 будут добавлены единицы и получены суммы прямых и дополнительных кодов.

Логика на элементах 10,13 и 11 выберет из двух сумм ту, которая будет представлена в дополнительном коде, и далее все произойдет, как описано выше для двух прямых кодов.

Если коды А и В представляют числа разных знаков, то один из кодов должен быть прямым, а другой - дополнительным. При этом в одном сумматоре (3 или 4) будут складываться прямые коды, а в другом (4 или 3) - дополнительные. Соответственно и на выходе одного сумматора появится результат в прямом коде, а на выходе другого - в дополнительном коде. Последний и будет использован в дальнейших операциях.

Поскольку при вычитании чисел разных знаков модуль разности больше уменьшаемого и больше вычитаемого, то возможно переполнение, из-за которого возникает ограничение на допустимые значения А и В. Необходимо, чтобы

| А| + | В| ≅ 2n-1

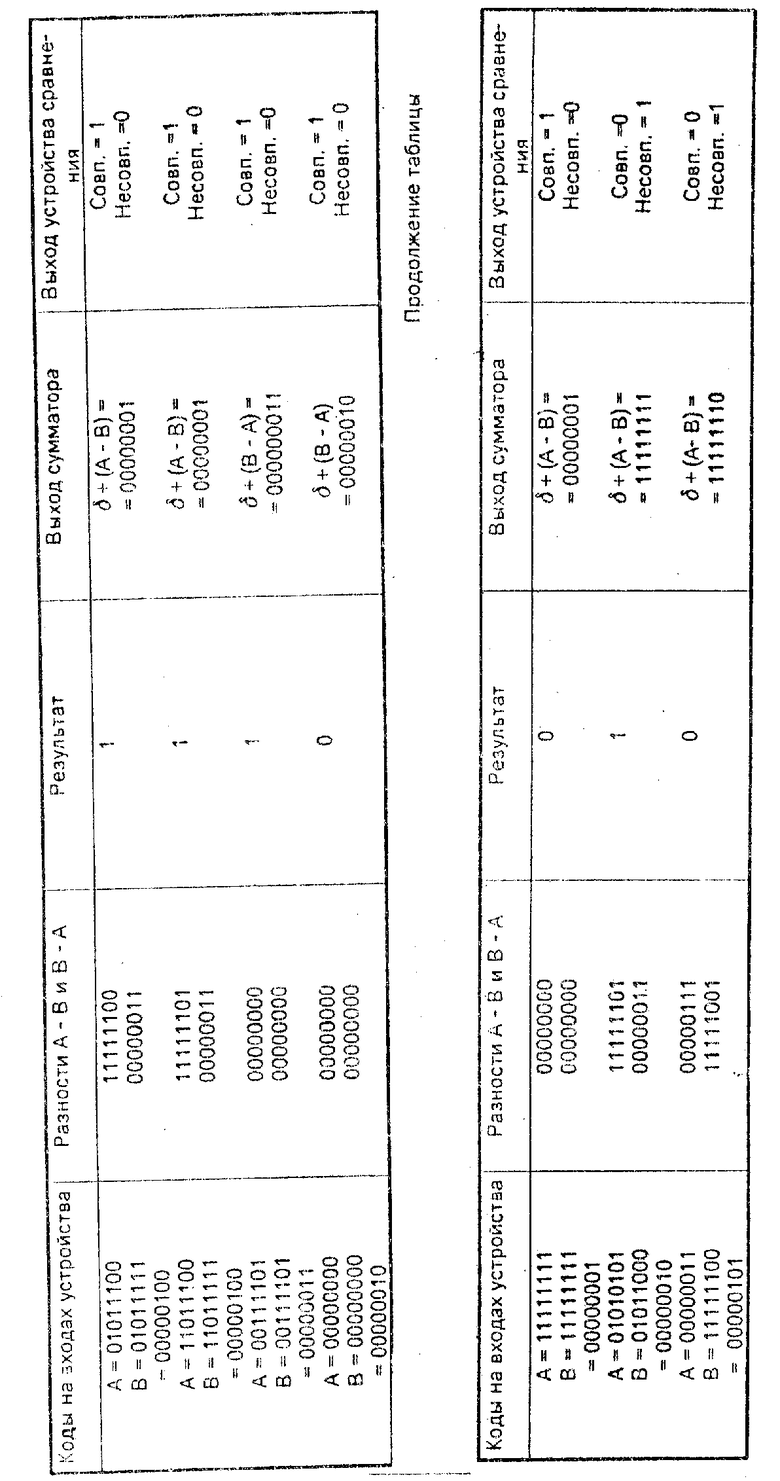

В таблице приведены примеры для различных А и В при n= 7.

Данное устройство сравнения имеет равномерную для любых сочетаний А и В зону допустимых значений, ширина которой, равная 2 δ, может задаваться с учетом конкретного применения. Выполняемая устройством операция сравнения требует двукратного определения дополнительного кода и двукратного суммирования. Первый раз дополнительный код получается добавлением переноса к обратному коду, второй раз выбирается из двух возможных результатов. Это повышает быстродействие.

На фиг. 4 показаны границы зоны совпадения в предлагаемом устройстве при n+1= 4 для различных значений. Видно, что в отличие от прототипа зона совпадений охватывает все заданные значения и может быть задана с дискретностью в одну единицу. Это является очевидным преимуществом.

Предлагаемое устройство сравнения может быть применено для оценки величины разброса результатов, выдаваемых аналого-цифровым преобразованием, на входе которой аналогичный сигнал остается постоянным. Другое применение состоит в контроле правльности вычислений, выполняемых параллельно несколькими ЭВМ по одинаковым программам, исходными данными у которых являются сигналы разных датчиков, измеряющих одни и те же параметры.

Очевидно возможны и другие применения, где необходимо сравнивать двоичные коды с заданной зоной допустимых расхождений.

(56) Авторское свидетельство СССР N 1363181, кл. G 06 F 7/02, 1987.

Авторское свидетельство СССР N 1221649, кл. G 06 F 7/02, 1986.

Изобретение относится к вычислительной технике. Оно обеспечивает повышение точности и быстродействия при сравнении целых чисел с одинаковыми или разными знаками, а также возможность сравнения с заданным допуском. Устройство содержит регистры 1,2, сумматоры 3,4,5, группы элементов И 6,7, ИЛИ 8, элемент задержки 9, элементы НЕ 10, 11, 12, элемент И - НЕ 13, элементы И 14 - 17. 4 ил.

УСТРОЙСТВО ДЛЯ СРАВНЕНИЯ чисел, содержащее сумматор, элемент задержки, три элемента НЕ, два элемента И, группу элементов ИЛИ, причем вход пуска устройства через элемент задержки соединен с первыми входами первого и второго элементов И, выходы которых являются выходами устройства, выходы элементов ИЛИ группы соединены с входами первого слагаемого первого сумматора, выход знакового разряда которого соединен с вторым входом первого элемента И и через первый элемент НЕ - с вторым входом второго элемента И, отличающееся тем, что устройство введены второй и третий сумматоры, третий и четвертый элементы И, два регистра, две группы элементов И и элемент И - НЕ, причем входы первого и второго сравниваемых чисел устройства соединены с информационными входами соответственно первого и второго регистров, управляющие входы которых соединены с входом пуска устройства, прямые выходы разрядов первого и второго регистров соединены с входами первых слагаемых соответственно второго и третьего сумматоров, входы вторых слагаемых которых соединены с инверсными выходами разрядов соответственно второго и первого регистров, входы переноса подключены к входу логической единицы устройства, выходы сумм второго и третьего сумматоров соединены с информационными входами элементов И соответственно первой и второй групп, а выходы знаковых разрядов соединены соответственно с первым входом элемента И - НЕ и через второй элемент НЕ с вторым входом элемента И - НЕ, выход которого соединен с управляющими входами элементов И второй группы, первым входом третьего элемента И и через третий элемент НЕ с управляющими входами элементов И первой группы и первым входом четвертого элемента И, выходы элементов И первой и второй групп соединены соответственно с первыми и вторыми входами элементов ИЛИ группы, входы кода допуска устройства подключены к входам второго слагаемого первого сумматора, выход переноса которого соединен с вторыми входами третьего и четвертого элементов И, третьи входы которых подключены через элемент задержки к входу пуска устройства, а выходы являются выходами соответственно A>>B+δиA+δ<B устройства, выходы второго и первого элементов И являются выходами "Совпадение" и "Несовпадение" устройства.

Авторы

Даты

1994-01-30—Публикация

1992-04-27—Подача