Изобретение относится к вычислительной технике и может быть использовано для защиты ячеек памяти при пропадании питания.

Известно устройство для защиты информации в оперативной памяти ЭВМ, содержащее первый блок сравнения, стабилизатор напряжения, резервный источник питания, коммутатор, блок нагрузки, одновибратор, второй блок сравнения.

Известно устройство защиты памяти, в котором даже небольшое уменьшение питающего напряжения приводит к срабатыванию защиты.

Цель изобретения - повышение помехоустойчивости устройства.

В предлагаемое устройство введен резистор, который образует с основным резистором делитель, который увеличивает помехозащищенность ключа по отношению к помехе со стороны управляющего сигнала. Кроме того, присутствие дополнительного резистора с соответствующим номиналом позволяет зафиксировать уровень срабатывания транзистора ("открыт"). В известном устройстве есть только разрешающий сигнал, позволяющий прохождение любой помехи.

Преимущества изобретения по сравнению с прототипом: упрощение устройства (отсутствие блока управления, использование дешифратора вместо операционного блока); уменьшение тока потребления с батареи питания (источник батарейного питания обеспечивает только микросхема ОЗУ); уменьшение вероятности несанкционированной записи в ОЗУ (сигнал с выхода ключа управляет выбором кристалла С).

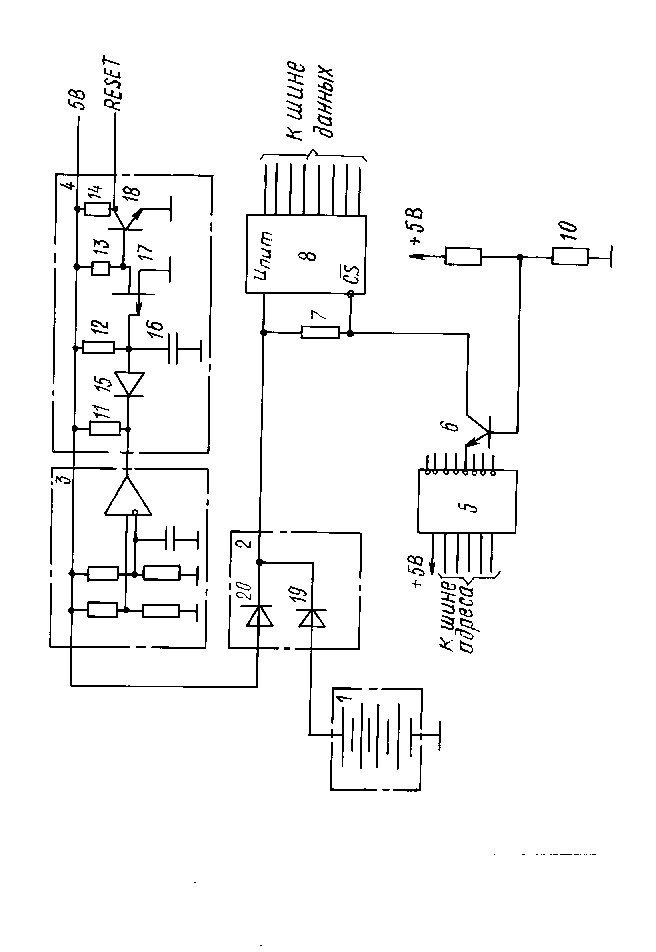

На чертеже приведена функциональная схема устройства защиты памяти.

Устройство содержит источник 1 питания, переключатель 2 питания, компаратор 3, блок 4 формирования сигнала сброса, дешифратор 5, ключ 6, резистор 7 и ЗУ 8, резисторы 9, 10. Блок 4 формирования сигнала сброса содержит резисторы 11-14, диод 15, конденсатор 16, полевой транзистор 17, ключевой транзистор 18. Переключатель 2 питания содержит первый и второй диоды 19 и 20.

В качестве дешифратора 5 может быть использована серийно выпускаемая в СССР микросхема К555ИД7, бКО. 348.289-02 ТУ, в качестве ключей 6, 18 - серийно выпускаемые транзисторы КТ343В, ЖК3.365.227 ТУ, в качестве делителя 9, 10 - резисторы МЛТ - 0,125 - 8,2 кОм ±10% , МЛТ - 0,125-2,4 кОм ±10% , ОЖО. 467.180 ТУ, соответственно, в качестве ключа 17 - полевой транзистор КП103К, ТФЗ. 365.000 ТУ1, в качестве резистора 12 - резистор МЛТ - 0,125-1,2 мОм ±10% , ОДО. 467.180 ТУ, конденсатора 16 - конденсатор КМ5А - 0,15 мкф ±10% , ОЖО. 460.043. ТУ.

Устройство работает следующим образом.

При включении питания напряжение питания + 5 В нарастает по экспоненте за время τ1. Постоянная времени τ2, определяемая резистором 12 и конденсатором 16, много больше τ1, и в течение всего этого времени установлен сигнал RES ET, который не позволяет работать процессору. Во время нарастания напряжения питания ключ 18 находится в закрытом состоянии за счет того, что ключ 17, выполненный на полевом транзисторе, имеет открытый канал до тех пор, пока конденсатор 16 не зарядится до напряжения отсечки. Неустойчивая работа компаратора 3 только подтверждает сигнал RES ET. При любом низком уровне на выходе компаратора 3 происходит разряд конденсатора 16 через диод 15, при установке нормального напряжения питания на выходе компаратора 3 устанавливается высокий уровень и диод 15 закрывается, постоянная времени заряда конденсатора 16 определяется только резистором 12. До тех пор, пока напряжение на базе ключа 6 не достигнет уровня срабатывания, определяемое делителем 9, 10 от напряжения + 5 В, дешифратор 5 находится в неустойчивом состоянии, сигнал с него не проходит на вход выбора ЗУ 8. Все это время ЗУ 8 находится под напряжением питания источника 1. Диод 20 закрыт этим напряжением. По достижении напряжения питания 5 В диод 20 открывается, а диод 19 закрывается. ЗУ 8 находится под напряжением источника питания. Дешифратор 5 и компаратор 3 находятся в устойчивом состоянии. Ключ 6 разрешен для работы. Через время τ2 сигнал RES ET снимается, процессор начинает работу и при обращении к ЗУ 8 на выходе дешифратора 5 появляется низкий уровень, ключ 6 открывается и сигнал обращения поступает на ЗУ 8.

При выключении питания напряжение + 5 В начинает уменьшаться. При напряжении питания, определяемом компаратором 3, конденсатор 16 разряжается через диод 15, и на выходе ключа 18 появляется сигнал RES ET, который останавливает работу процессора. Этот уровень срабатывания находится в пределах рабочих уровней напряжений для цифровых микросхем.

При дальнейшем уменьшении напряжения питания потенциал на базе ключа 6 выключает его, и ложные сигналы не проходят к ЗУ 8, а само ЗУ 8 подключается к источнику 1 питания. Далее схема защиты находится в ожидании включения питания.

Использование предложенной схемы защиты позволит значительно упростить устройство, что повысит его надежность. (56) Патент Японии 61-30304, кл. G 06 F 12/16, 1987.

Авторское свидетельство СССР N 1474657, кл. G 06 F 12/16, 1987.

| название | год | авторы | номер документа |

|---|---|---|---|

| КЛЮЧЕВОЕ УСТРОЙСТВО | 1996 |

|

RU2110884C1 |

| УСТРОЙСТВО ДЛЯ ПРОВЕРКИ АППАРАТОВ ТОКОВОЙ ЗАЩИТЫ | 1990 |

|

RU2024888C1 |

| УСТРОЙСТВО СТАБИЛИЗАЦИИ НАПРЯЖЕНИЯ ПИТАНИЯ УСТРОЙСТВ АВТОМАТИКИ ТРАНСПОРТНЫХ СРЕДСТВ | 2006 |

|

RU2307450C1 |

| Устройство для обнаружения межвитковых замыканий в обмотках трехфазных электрических машин | 1985 |

|

SU1328772A1 |

| УСТРОЙСТВО ЗАЩИТЫ ИНФОРМАЦИИ ОТ НЕСАНКЦИОНИРОВАННОГО ДОСТУПА | 2003 |

|

RU2263345C2 |

| МНОЖИТЕЛЬНОЕ УСТРОЙСТВО | 1993 |

|

RU2082996C1 |

| УСТРОЙСТВО ЭЛЕКТРОПИТАНИЯ КОРАБЕЛЬНОЙ АППАРАТУРЫ | 1998 |

|

RU2123225C1 |

| ЭЛЕКТРОННЫЙ ПРЕДОХРАНИТЕЛЬ С САМОВОССТАНОВЛЕНИЕМ | 2010 |

|

RU2432656C1 |

| СИСТЕМА ЭЛЕКТРОСНАБЖЕНИЯ ПОСТОЯННОГО ТОКА | 1990 |

|

RU2016465C1 |

| Устройство для управления электродвигателем воздуховсасывающего агрегата пылесоса | 1990 |

|

SU1734183A1 |

Изобретение относится к вычислительной технике и может быть использовано для защиты ячеек памяти при пропадании питания. Цель изобретения - повышение помехоустойчивости устройства. Устройство содержит источник 1 питания, переключатель 2 питания, компаратор 3, блок 4 формирования сигнала сброса, дешифратор 5, ключ 6, резистор 7, ЗУ 8, резисторы 9, 10. 1 з. п. ф-лы, 1 ил.

Авторы

Даты

1994-01-30—Публикация

1991-01-10—Подача