Изобретение относится к электроизмерительной технике и может быть использовано для выявления вйтковых замыканий в обмотках трехфазных электрических машин.

Целью изобретения является повышение производительности контроля путем снижения трудоемкости.

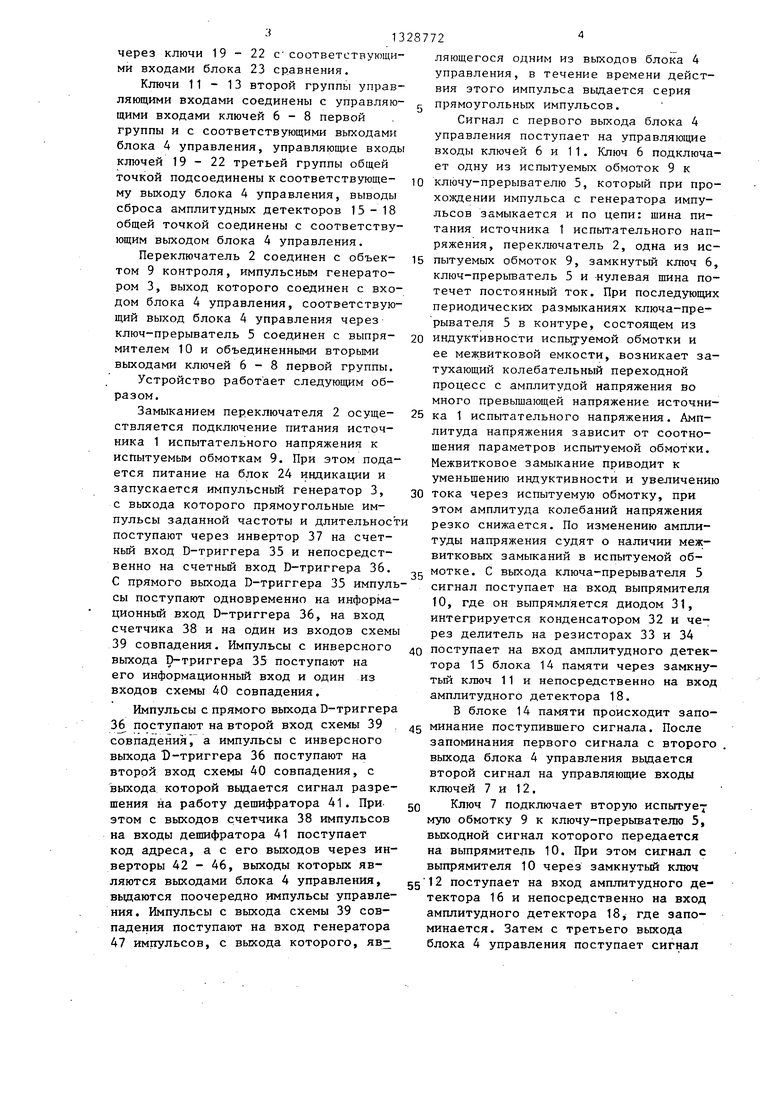

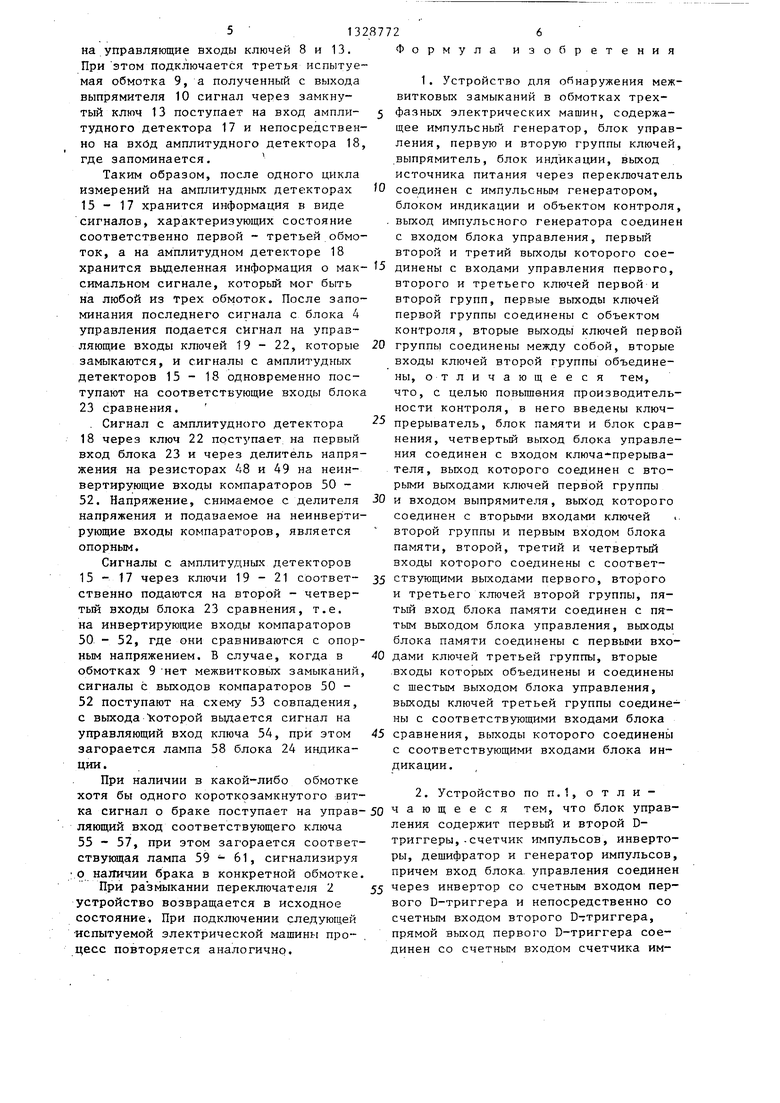

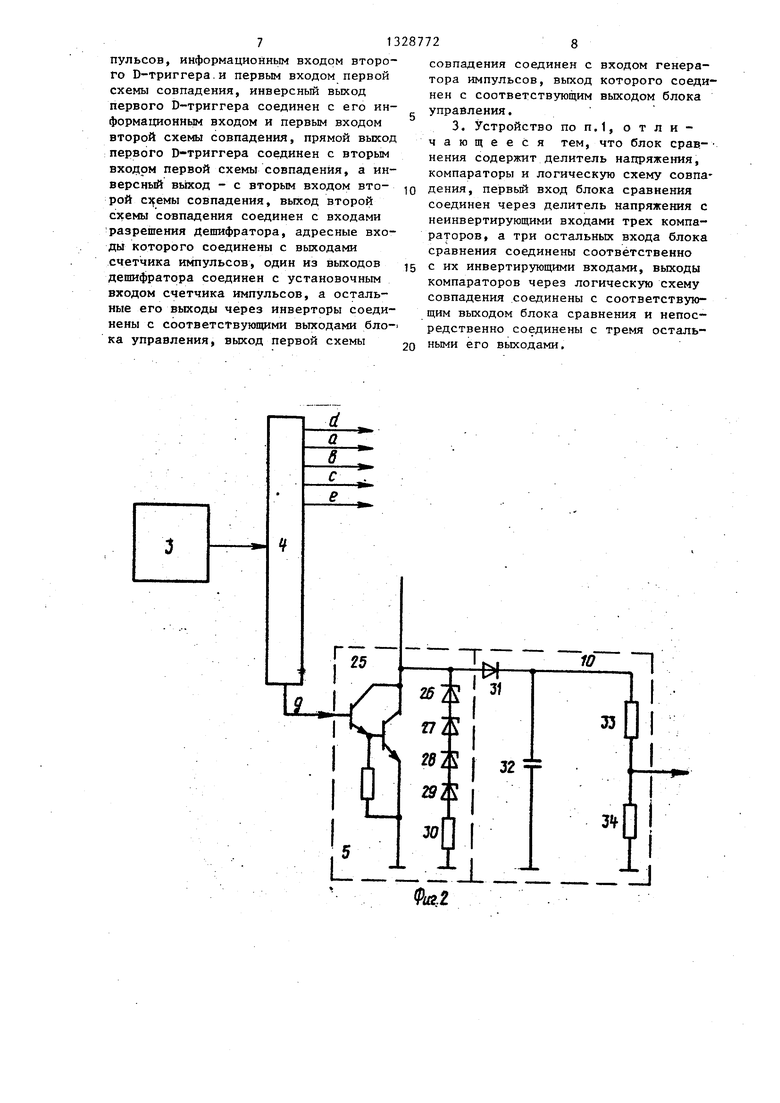

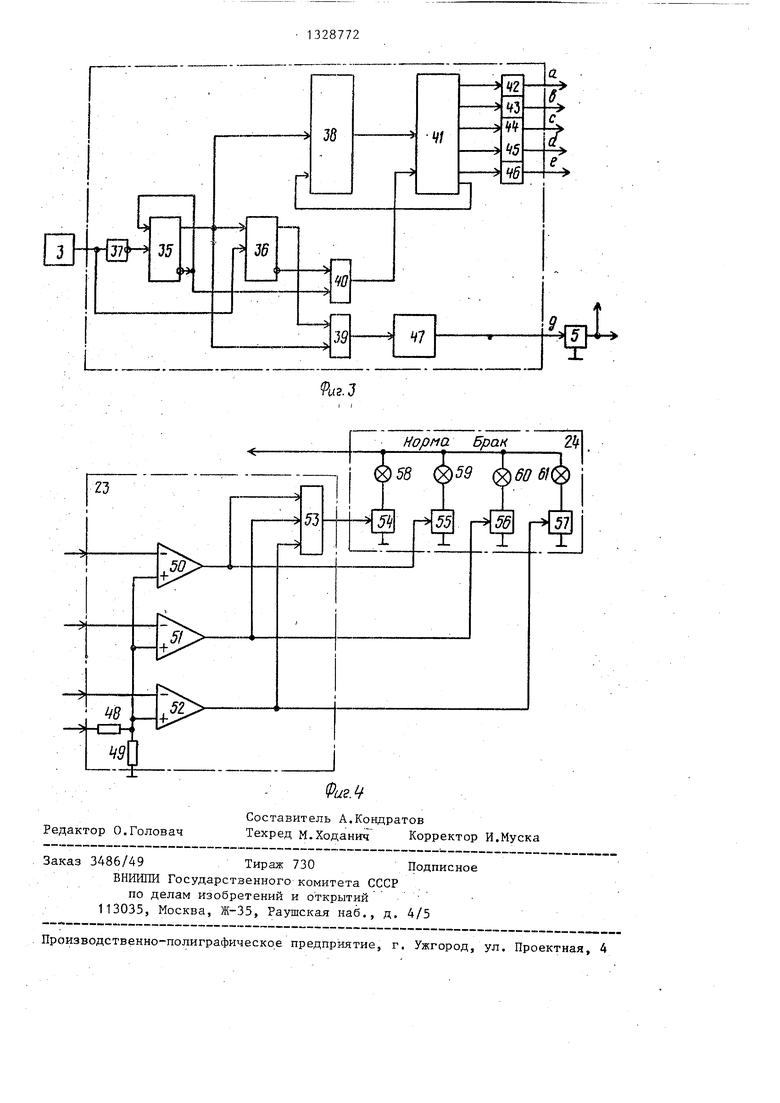

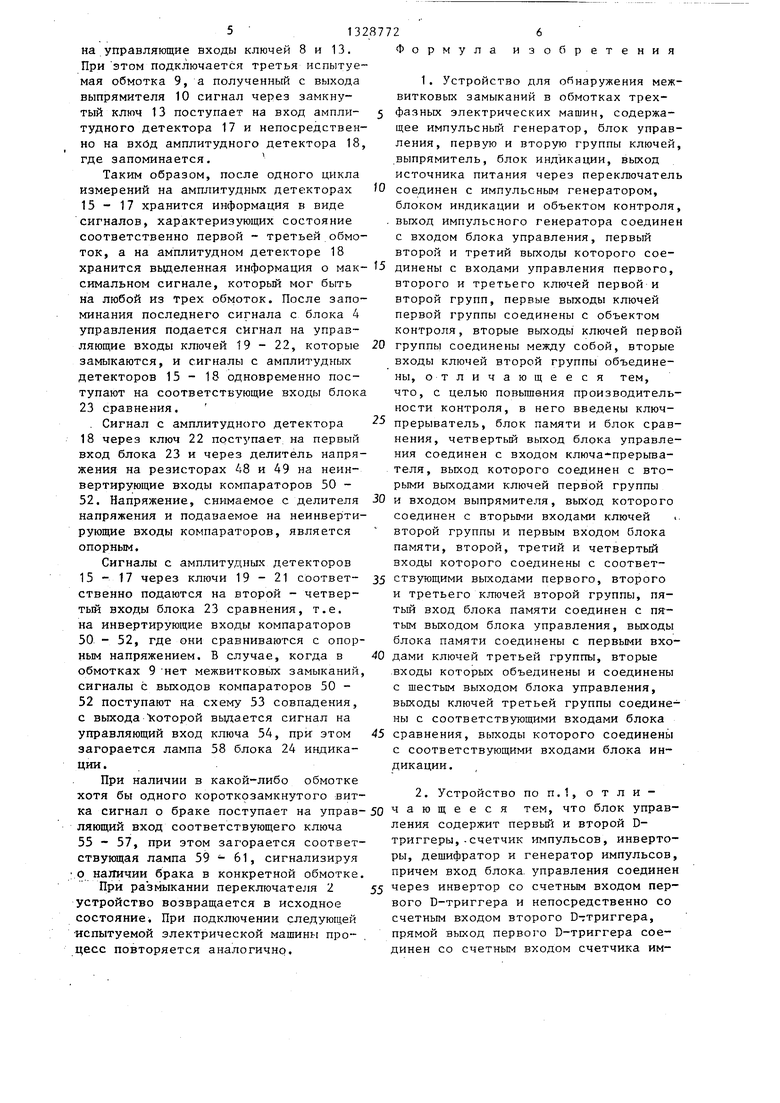

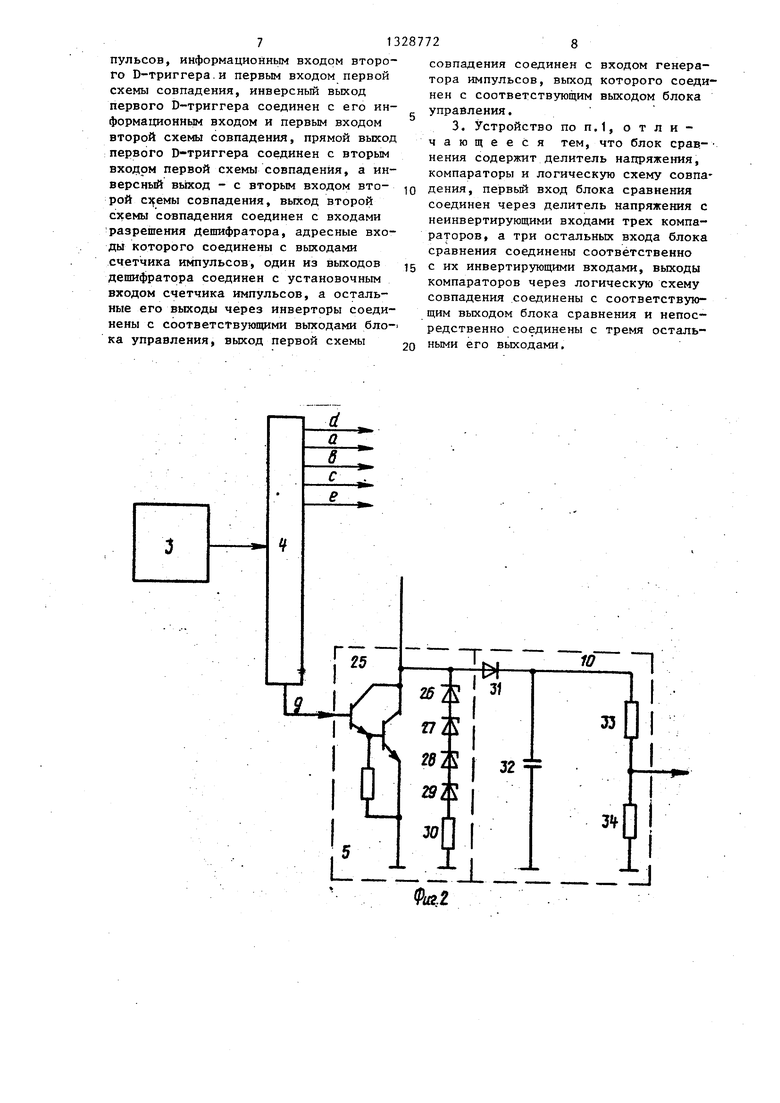

На фиг.1 изображена схема предлагаемого устройства; на фиг,2 - схема ключа-прерывателя испытательного тока и вьтрямителя; на фиг.3 - схема блока управления; на фиг,4 - схема блока сравнения.

Устройство содержит источник 1 испытательного напряжения, переключатель 2, импульсный генератор 3, блок 4 управления, ключ-прерьшатель 5 испытательного тока, первую группу клю- 2окоторого соединен с одним из выходов

чей 6-8 для подключения объекта 9блока 4 управления. кoнtpoля (соответствующей испытуемой Блок 23 сравнения .содержит делиобмотки), вторую группу ключей 11 -тель напряжения на резисторах 48 и

13, блок 14 памяти, состоящий из амп-49, общей точкой соединенных с неинлитудных цeтeктot oз 15 - 18, третью группу ключей 19 - 22,, блок 23 сравнения и 0ЛОК 24 индикации.

Ключ-прерыватель 5 испытательного тока выполнен на составном транзисторе 25. Между коллекторным выводом ключа 5 и нулевой шиной источника 1 испытательного напряжения установлена цепочка защиты транзисторов ключа от перенапряжений, которая состоит из стабилитронов 26 - 29 и резистора. 30.

Выпрямитель 10 состоит из диода 31, анодом подключенного к выходу .ключа 5, а катодом к первым вьгоодам . конденсатора 32 И резистора 33, второй вывод конденсатора 32 соединен с нулевой шиной непосредственно, а резистора 33 - через резистор 34, общая точка резисторов 33 и 34 является выходом вьтрямителя 10, а базовьй вывод составного транзистора 25 - входом ключа.

Блок управления содержит D-триг- геры 35 и 36, инвертор 37, счетчик 38 импульсов, схемы 39 и 40 совпадения, дешифратор 41, инверторы 42 - 46 и генератор 47 импульсов. : Вход блока 4 управления соединен через инвертор 37 со счетным входом В-триггера 35 и непосредственно со счетным входом D-триггера 36, прямой выход D-триггера 35 соединен со счетным входом счетчика 38 импульсов, информационным входом В-триггера 36 и одним из входов схемы 39 совпаде- :

25 вертирующими входами компараторов 50-52, резистор 48 вторым выводом соединен с Первым входом блока 23, а второй вывод резистора 49 соединен с нулевой шиной, инвертирующие входы

30 компараторов 50 - 52 соединены соответственно с вторым - четвертым входами блока 23, выходы компараторов 50 - 5JZ через логическую схему 53 совпадения соединены с первым выходом и непосредственно с тремя остальными

35

выходами блока 23.

40

45

Блок 24.индикации содержит ключи 54 - 57, одними выходами соединенные соответственно с лампами 58 - 61, . вторые выходы которых общей точкой соединены через переключатель 2 с источником 1 испытательного напряжения, вторые выходы ключей 54 - 57 соединены с нулевой шиной, управляющие входы ключей 54 - 57, являющиеся входами - блока 24, соединены с соответствующими выходами блока 23 сравнения.

Амплитудные детекторы 15 - 17 вхо- дами, которые являются входами блока

14памяти, соответственно через ключи 11 - 13 соединены с выходом выпрями теля 10, а амплитудный детектор 18 своим входом, которьй также являете; входом блока 14 памяти, соединен с выходом вьтрямителя 10 непосредственно, выходы амплитудных детекторов

15- 18, являющиеся выходами блока 14 памяти, соединены соответственно

55

ния. Инверсный выход D-триггера 35 соединен с его информационным входом и одним из входов схемы 40 совпадения, прямой выход D-триггера 36 соединен с вторым входом схемы 39 совпадения, а инверсный выход - с вторым входом схемы 40 совпадения, выход схемы 40 совпадения соединен с входами разрешения работы дешифратора 41, адресные входы которого соединены с выходами счетчика 38 импульсов, один из выходов дешифратора 41 соединен с установочным входом счетчика 38 импульсов, а остальные его выходы через инверторы 42 - 46 - соответственно с выходами блока 4 управления, выход схемы 39 совпадения соединен с входом генератора 47 импульсов, выход

25 вертирующими входами компараторов 50-52, резистор 48 вторым выводом соединен с Первым входом блока 23, а второй вывод резистора 49 соединен с нулевой шиной, инвертирующие входы

30 компараторов 50 - 52 соединены соответственно с вторым - четвертым входами блока 23, выходы компараторов 50 - 5JZ через логическую схему 53 совпадения соединены с первым выходо и непосредственно с тремя остальными

35

выходами блока 23.

0

5

Блок 24.индикации содержит ключи 54 - 57, одними выходами соединенные соответственно с лампами 58 - 61, . вторые выходы которых общей точкой соединены через переключатель 2 с источником 1 испытательного напряжения, вторые выходы ключей 54 - 57 соединены с нулевой шиной, управляющие входы: ключей 54 - 57, являющиеся входами - блока 24, соединены с соответствующими выходами блока 23 сравнения.

Амплитудные детекторы 15 - 17 вхо- дами, которые являются входами блока

14памяти, соответственно через ключи 11 - 13 соединены с выходом выпрями теля 10, а амплитудный детектор 18 своим входом, которьй также являете; входом блока 14 памяти, соединен с выходом вьтрямителя 10 непосредственно, выходы амплитудных детекторов

15- 18, являющиеся выходами блока 14 памяти, соединены соответственно

5

через ключи 19-22 с соответствующими входами блока 23 сравнения.

Ключи 11-13 второй группы управляющими входами соединены с управляющими входами ключей 6-8 первой группы и с соответствующими выходами блока 4 управления, управляющие входы ключей 19-22 третьей группы общей точкой подсоединены к соответствующему выходу блока 4 управления, выводы сброса амплитудных детекторов 15-18 общей точкой соединены с соответствующим выходом блока 4 управления.

Переключатель 2 соединен с объектом 9 контроля, импульсным генератором 3, выход которого соединен с входом блока 4 управления, соответствующий выход блока 4 управления через ключ-прерыватель 5 соединен с выпрямителем 10 и объединенными вторыми выходами ключей 6-8 первой группы.

Устройство работает следующим образом.

Замыканием переключателя 2 осуществляется подключение питания источника 1 испытательного напряжения к испытуемым обмоткам 9. При этом подается питание на блок 24 индикации и запускается импульсный генератор 3, с выхода которого прямоугольные импульсы заданной частоты и длительност поступают через инвертор 37 на счетный вход D-триггера 35 и непосредственно на счетный вход D-триггера 36. С прямого выхода D-триггера 35 импульсы поступают одновременно на информационный вход D-триггера 36, на вход счетчика 38 и на один из входов схемы 39 совпадения. Импульсы с инверсного выхода р-триггера 35 поступают на его информационный вход и один из входов схемы 40 совпадения.

Импульсы с прямого выхода D-триггера 3 поступают на второй вход схемы 39 совпадения, а импульсы с инверсного выхода 1)-триггера 36 поступают на второй вход схемы 40 совпадения, с выхода которой вьщается сигнал разрешения на работу дешифратора 41, При этом с выходов счетчика 38 импульсов на входы дешифратора 41 поступает код адреса, а с его выходов через инверторы 42 - 46, выходы которых являются выходами блока 4 управления, вьщаются поочередно импульсы управления. Импульсы с выхода схемы 39 совпадения поступают на вход генератора 47 импульсов, с выхода которого, яв

5

0

ляющегося одним из выходов блока 4 управления, в течение времени действия этого импульса выдается серия прямоугольных импульсов.

Сигнал с первого выхода блока 4 управления поступает на управляю1цие входы ключей 6 и 11, Ключ 6 подключает одну из испытуемых обмоток 9 к ключу-прерывателю 5, который при прохождении импульса с генератора импульсов замыкается и по цепи: шина питания источника 1 испытательного напряжения, переключатель 2, одна из ис5 пытуемых обмоток 9, замкнутьй ключ 6, ключ-прерыватель 5 и -нулевая шина потечет постоянный ток. При последующих периодических размыканиях ключа-прерывателя 5 в контуре, состоящем из

0 индуктивности испьгууемой обмотки и ее межвитковой емкости, возникает затухающий колебательный переходной процесс с амплитудой напряжения во много превышающей напряжение источника 1 испытательного напряжения. Амплитуда напряжения зависит от соотношения параметров испытуемой обмотки. Межвитковое замыкание приводит к уменьшению индуктивности и увеличению тока через испытуемую обмотку, при этом амплитуда колебаний напряжения резко снижается. По изменению амплитуды напряжения судят о наличии меж- витковых замыканий в испытуемой обмотке, С выхода ключа-прерывателя 5 сигнал поступает на вход выпрямителя 10, где он выпрямляется диодом 31, интегрируется конденсатором 32 и через делитель на резисторах 33 и 34 поступает на вход амплитудного детектора 15 блока 14 памяти через замкнутый ключ 11 и непосредственно на вход амплитудного детектора 18.

В блоке 14 памяти происходит запо-

5 минание поступившего сигнала. После запоминания первого сигнала с второго выхода блока 4 управления выдается второй сигнал на управляющие входы ключей 7 и 12.

Ключ 7 подключает вторую испытуе7 мую обмотку 9 к ключу-прерьшателю 5, выходной сигнал которого передается на выпрямитель 10, При этом сигнал с выпрямителя 10 через замкнутый ключ 12 поступает на вход амплитудного детектора 16 и непосредственно на вход амплитудного детектора 18, где запоминается. Затем с третьего выхода блока 4 управления поступает сигнал

5

0

0

5

1328772

на управляющие входы ключей 8 и 13. При этом подключается третья испытуемая обмотка 9, а полученный с выхода выпрямителя 10 сигнал через замкну- тьй ключ 13 поступает на вход ампли- 5 тудного детектора 17 и непосредственно на вхйд амплитудного детектора 18, где запоминается.

Таким образом, после одного цикла измерений на амплитудных детекторах JO 15-17 хранится информация в виде сигналов, характеризующих состояние соответственно первой - третьей обмоток, а на амплитудном детекторе 18 хранится вьвделенная информация о мак- 5 симальном сигнале, который мог быть на любой из Трех обмоток. После запоминания последнего сигнала с блока 4 управления подается сигнал на управляющие входы ключей 19 - 22, которые 20 замыкаются, и сигршлы с амплитуд гьгх детекторов 15 - 18 одновременно поступают на соответствующие входы блока 23 сравнения.

. Сигнал с амплитудного детектора 18 через ключ 22 поступает на первый вход блока 23 и через делитель напряжения на резисторах 48 и 49 на неинвертирующие входы компараторов 50 Формула

6 зоб

Р е т е н и я

1. Устройство для обнаружения меж- витковых замыканий в обмотках трехфазных электрических машин, содержащее импульсный генератор, блок управления, первую и вторую группы ключей, выпрямитель, блок индикации, выход источника питания через перекл очатель соединен с импульсным генератором, блоком индикации и объектом контроля, выход импульсного генератора соединен с входом блока управления, первьй второй и третий выходы которого соединены с входами управления первого, второго и третьего ключей первой и второй групп, первые выходы ключей первой группы соединены с объектом контроля, вторые выходы ключей первой группы соединены между собой, вторые входы ключей второй группы объединены, отличающееся тем, что, с целью повышения производительности контроля, в него введены ключ- прерыватель, блок памяти и блок сравнения, четвертый выход блока управления соединен с входом ключа-прерывателя, выход которого соединен с вторыми выходами ключей первой группы

52. Напряжение, снимаемое с делителя 30 и входом выпрямителя, выход которого

напряжения и подаваемое на неинвертирующие входы компараторов, является опорным.

Сигналы с амплитудных детекторов 15 - 17 через ключи 19-21 соответственно подаются на второй - четвертый входы блока 23 сравнения, т.е. на инвертирующие входы компараторов 50 - 52, где они сравниваются с опор НЬ1М напряжением. В случае, когда в обмотках 9 нет межвитковых замыканий сигналы с выходов компараторов 50 - 52 поступают на схему 53 совпадения, с выхода Которой выдается сигнал на ключа 54, при этом 58 блока 24 индикауправляющии вход загорается лампа ции.

При наличии в

какой-либо обмотке

хотя бы одного короткозамкнутого витка сигнал о браке поступает на управ ляющий вход соответствующего ключа 55 57, при этом загорается соответствующая лампа 59 - 61, сигнализируя о наличии брака в конкретной обмотке

При размыкании переключателя 2 устройство возвращается в исходное состояние. При подключении следующей

испытуемой электрической машины процесс повторяется аналогично.

ормула

6 зоб

Р е т е н и я

1. Устройство для обнаружения меж- витковых замыканий в обмотках трехфазных электрических машин, содержащее импульсный генератор, блок управления, первую и вторую группы ключей, выпрямитель, блок индикации, выход источника питания через перекл очатель соединен с импульсным генератором, блоком индикации и объектом контроля, выход импульсного генератора соединен с входом блока управления, первьй второй и третий выходы которого соединены с входами управления первого, второго и третьего ключей первой и второй групп, первые выходы ключей первой группы соединены с объектом контроля, вторые выходы ключей первой группы соединены между собой, вторые входы ключей второй группы объединены, отличающееся тем, что, с целью повышения производительности контроля, в него введены ключ- прерыватель, блок памяти и блок сравнения, четвертый выход блока управления соединен с входом ключа-прерывателя, выход которого соединен с вторыми выходами ключей первой группы

соединен с вторьЕми входами ключей . второй группы и первым входом блока памяти, второй, третий и четвертый входы которого соединены с соответ35 ствующими выходами первого, второго и третьего ключей второй группы, пя- тьм вход блока памяти соединен с пятым выходом блока управления, выходы блока памяти соединены с первыми вхо40 дами ключей третьей группы, вторые входы которых объединены и соединены с шестым выходом блока управления, выходы ключей третьей группы соединены с соответствующими входами блока

45 сравнения, выходы которого соединены с соответствующими входами блока ин

о т л и 2. Устройство по П.1 а ю щ е е с я тем, что блок управления содержит первьй и второй D- триггеры,- счетчик импульсов, инверторы, дешифратор и генератор импульсов, причем вход блока, управления соединен через инвертор со счетным входом первого D-триггера и непосредственно со счетным входом второго D-триггера, прямой выход первого D-триггера соединен со счетным входом счетчика им71

пульсов, информационным входом второго D-триггера.и первым входом первой схемы совпадения, инверсный выход первого D-триггера соединен с его информационным входом и первым входом второй схемы совпадения, прямой выход первого D-триггера соединен с вторым входом первой схемы совпадения, а ин- версньй вьЬсод - с вторым входом второй C5fемы совпадения, выход второй схемы совпадения соединен с входами разрешения дешифратора, адресные входы которого соединены с выходами счетчика импульсов, один из выходов дешифратора соединен с установочным входом счетчика импульсов, а остальные его выходы через инверторы соединены с соответствующими выходами блока управления, выход первой схемы

0

5

8

совпадения соединен с входом генератора импульсов, выход которого соединен с соответствующим выходом блока управления.

3. Устройство по П.1, о т л и 9

0

чающееся тем, что блок сравнения содержит делитель напряжения, компараторы и логическую схему совпадения, первьй вход блока сравнения соединен через делитель напряжения с неинвертирующими входами трех компараторов, а три остальных входа блока сравнения соединены соответственно с их инвертирующими входами, выходы компараторов через логическую схему совпадения соединены с соответствующим выходом блока сравнения и непосредственно соединены с тремя остальными его выходами.

38

k

42

t

H 5

46

С

rt

e

35

36

(

W

39

L..

1

roL

r5U-

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство контроля качества обмоток трехфазных электрических машин | 1989 |

|

SU1622853A1 |

| АНАЛИЗАТОР РАБОТЫ СИСТЕМ ДВИГАТЕЛЯ ВНУТРЕННЕГО СГОРАНИЯ | 2011 |

|

RU2532990C2 |

| АНАЛИЗАТОР РАБОТЫ СИСТЕМ ДВИГАТЕЛЯ ВНУТРЕННЕГО СГОРАНИЯ | 2015 |

|

RU2626282C2 |

| АНАЛИЗАТОР РАБОТЫ СИСТЕМ ДВИГАТЕЛЯ ВНУТРЕННЕГО СГОРАНИЯ | 2004 |

|

RU2292024C2 |

| Устройство для контроля операционных усилителей в электронных блоках | 1988 |

|

SU1674018A1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕННОГО НАПРЯЖЕНИЯ В ЦИФРОВОЙ КОД ОТКЛОНЕНИЯ | 1992 |

|

RU2074396C1 |

| Устройство для контроля восприимчивости радиоприемников по побочным каналам приема | 1987 |

|

SU1411986A2 |

| АНАЛИЗАТОР РАБОТЫ СИСТЕМ ДВИГАТЕЛЯ ВНУТРЕННЕГО СГОРАНИЯ | 2007 |

|

RU2347203C1 |

| Устройство для контроля чувствительности побочных каналов в радиоприемниках | 1985 |

|

SU1264357A1 |

| Устройство для дифференциально-фазной защиты электроустановки | 1988 |

|

SU1601684A1 |

Изобретение относится к электроизмерительной технике. Цель изобрете- .НИН - повышение производительности .контроля. Устройство содержит источник 1 испытательного напряжения, переключатель 2, импульсный генератор 3, блок 4 управления, три группы ключей 6-8, 11- 13и 19- 22 и блок 24 индикации. Для достижения цели .в устройство введены ключ-прерыватель 5, блок 14 памяти, включающий амплитудные детекторы 15 - .18, блок 23 сравнения и образованы новые функциональные связи. В описании представлены примеры выполнения блока 4 управления и блока 23 сравнения. 2 з.п. ф-лы, 4 ил. (Л фиг. /

гъ

53

W

-k

5Z

Hop flu Брак

гч

55 (X)I (5/

r457l i

IT

IT

1

ЦВ

Редактор 0.Головач

(.4

Составитель А.Кондратов

Техред М.Ходанич Корректор И.Муска

Заказ 3486/49Тираж 730Подписное

ВНИИ1Ш Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Устройство для обнаружения межвитковых замыканий в обмотках электрических машин | 1978 |

|

SU725047A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1987-08-07—Публикация

1985-01-02—Подача