Изобретение относится к системам цифровой обработки телевизионной информации, в частности к устройствам автоматического анализа изображений.

Известно устройство для обработки сигналов изображения [1] , которое содержит синхрогенератор, датчик сигналов изображения, видеоконтрольный блок, цифроаналоговый преобразователь, первый и второй блоки нормализации сигнала изображения, первый и второй блоки сопряжения, блок управления и вычисления.

Недостаток известного устройства - узкие функциональные возможности по обработке изображений.

Наиболее близкой по технической сущности к заявляемой является, система анализа изображения [2] , которая содержит соединенные последовательно телевизионную камеру, аналого-цифровой преобразователь, входную просмотровую таблицу, к выходу которой подключен блок памяти, соединенные последовательно от блока памяти выходную просмотровую таблицу, цифроаналоговый преобразователь и мониторы, а также арифметико-логическое устройтво, соединенное микропрограммным контроллером, а через магистральную шину блоком адресов, блоком памяти и контроллером интерфейса, который вязан с дисковой памятью и пультом управления.

Недостаток прототипа - отсутствие возможности выбора и обеспечения или исключения выполнения того или иного процесса обработки в реальном масштабе времени видеосигналов объектов или их фрагментов, выбранных для анализа из совокупности объектов, находящихся в поле зрения телевизионной камеры.

Цель изобретения - расширение функциональных возможностей за чет увеличения количества вариантов обработки, в том числе фрагментов изображений.

Цель достигается тем, что в систему, содержащую соединенные последовательно датчик видеосигнала, преобразователь видеосигнала и табличный процессор, арифметико-логический блок, соединенный с блоком памяти и блоком управления, второй выход которого соединен с вторыми входами преобразователя видеосигналов и табличного процессора, второй табличный процессор, первым и вторым входами соединенный с выходом арифметико-логического блока и третьим выходом блока управления, четвертый выход которого соединен с вторым входом блока памяти, формирователь, вход которого соединен с третьим выходом блока управления, а выход - с входом видеоконтрольного блока, и синхронизатор, соединенный с выходом датчика видеосигнала и входом синхронизации блока управления, введены последовательно соединенные формирователь сигнала, блок селекции и первый коммутатор, второй, третий и четвертый входы которого соединены с вторым выходом блока управления, с выходом преобразователя видеосигнала, с выходом табличного процессора, а выход - с входом арифметико-логического блока, а также второй коммутатор, первый, второй, третий и четвертый входы которого соединены с выходом блока селекции, выходом второго табличного процессора, третьим выходом блока управления и выходом арифметико-логического блока, а выход - с вторым входом формирователя, третий вход которого соединен с выходом формирователя сигнала, вход-выход которого соединен с блоком управления, другой выход-вход которого соединен с блоком селекции, второй вход которого соединен с вторым выходом второго табличного процессора.

Цель достигается и тем, что первый и второй коммутаторы каждый содержит дешифратор, к первым выходам которого подключены ключи, а к вторым выходам - элементы ИЛИ, выходы которых подключены к вторым входам отдельных групп ключей, выходы которых соединены с управляющими входами шинных формирователей, информационные входы и выходы которых соединены с соответствующими входами и объединенным выходом коммутатора.

Сопоставительный анализ с прототипом показывает, что заявляемая система отличается наличием совокупности новых блоков: первого и второго коммутаторов, блока селекции, формирователя сигналов и связей этих блоков, а также структурой коммутаторов. В связи с этим заявляемая система соответствует критерию изобретения "новизна".

При изучении других известных технических решений в данной области техники признаки в своей совокупности, отличающие изобретение от прототипа, не выявлены, поэтому обеспечивают заявляемому техническому решению соответствие критерию "существенные отличия".

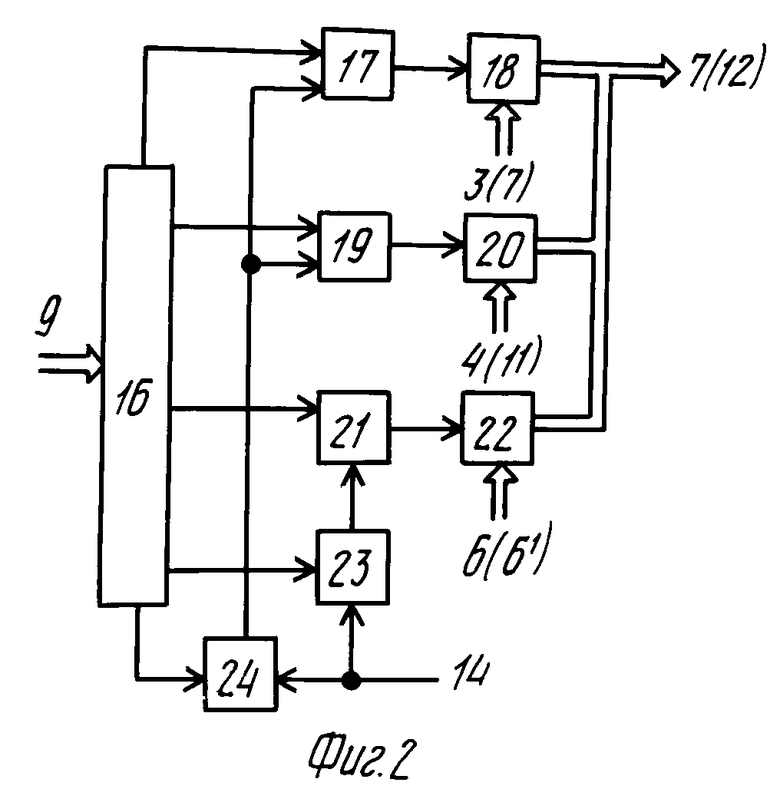

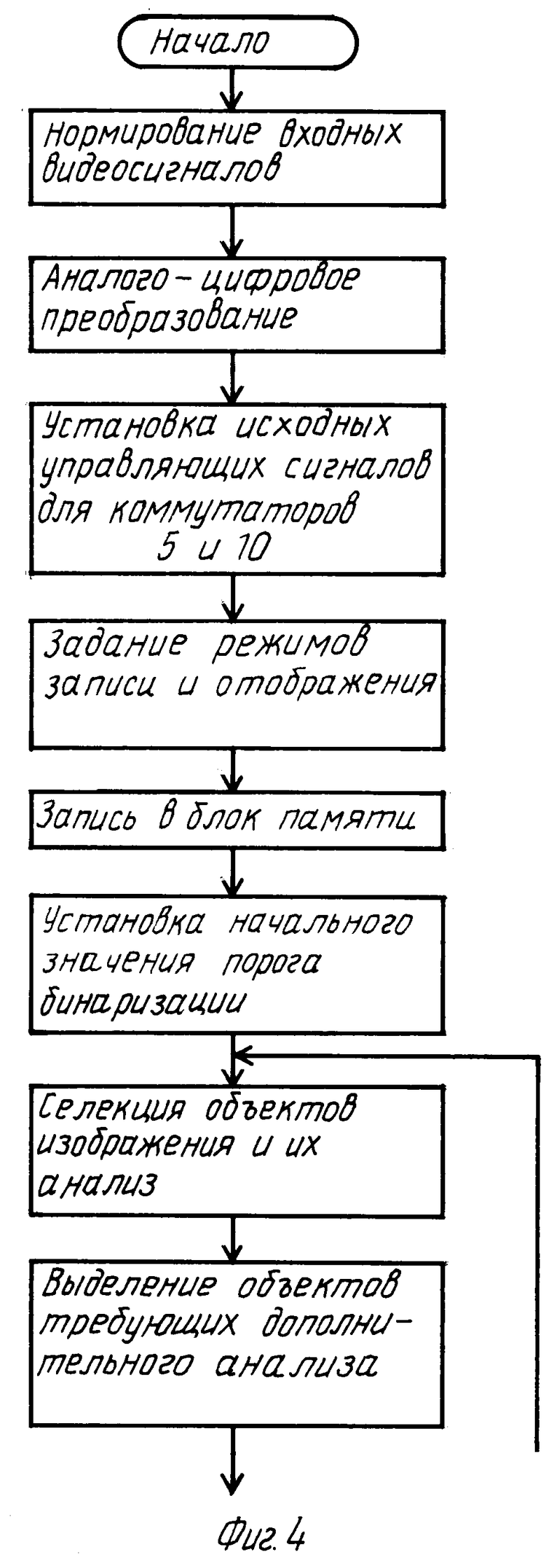

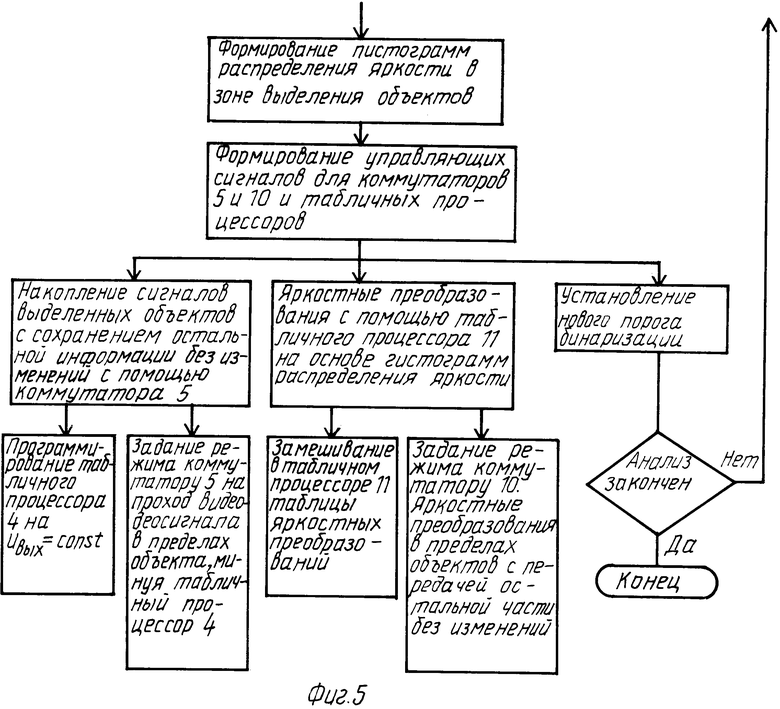

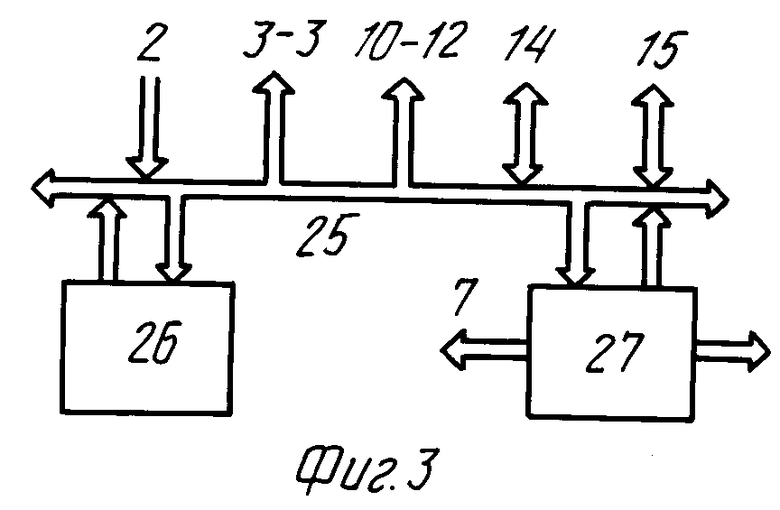

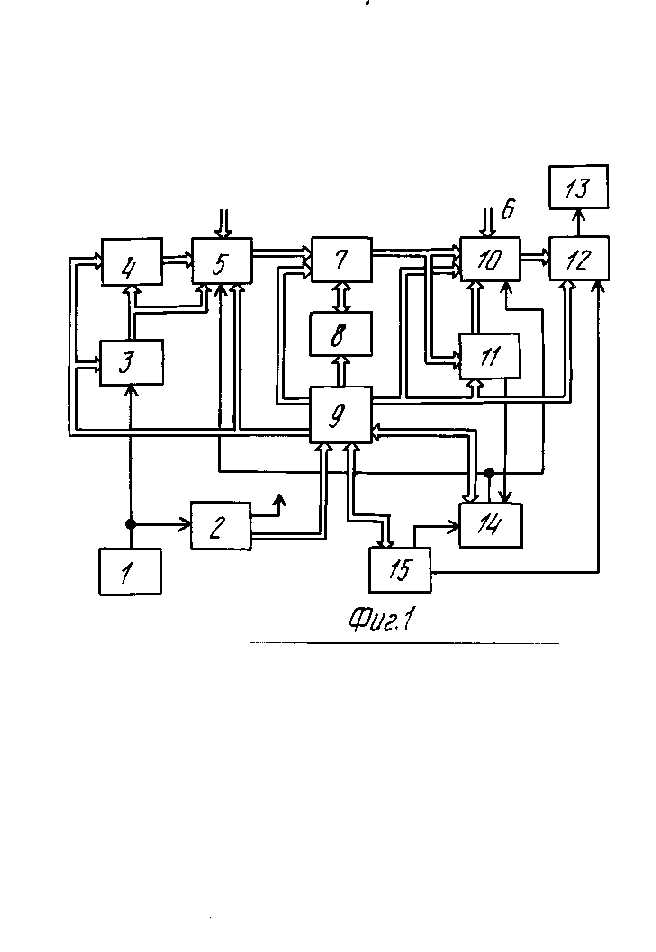

На фиг. 1 изображена структурная схема системы; на фиг. 2 - структурная схема коммутатора; на фиг. 3 - структурная схема блока микропрограммного управления; фиг. 4 и 5 - алгоритм работы системы.

Система для обработки изображений содержит датчик 1 видеосигнала, синхронизатор 2, преобразователь 3 видеосигнала, табличный процессор 4, коммутатор 5 с информационным входом 6 связи с внешними устройствами, арифметико-логический блок 7, блок 8 памяти, блок 9 микропрограммного управления, коммутатор входом 6, табличный процессор 11, формирователь 12 полного телевизионного сигнала, видеоконтрольный блок 13, блок 14 селекции, формирователь 15 сигнала контура и зоны анализа.

В качестве датчика 1 видеосигнала может быть использована передающая телевизионная камеры любого типа. Синхронизатор 2 обеспечивает систему сигналами тактовой частоты и синхронизации. Он содержит селектор сигналов синхронизации из полного телевизионного сигнала, который связан с входами узла формирования сигнала тактовой частоты и узла формирования сигнала синхронизации. Вход селектора является входом, а выходы формирователей - выходами синхронизатора.

Преобразователь 3 видеосигнала предназначен для нормирования амплитудных характеристик входного видеосигнала и преобразования видеосигнала в цифровой код. Он содержит включенные последовательно между входом и выходом преобразователя узел замеса уровня черного, узел регулировки размаха видеосигнала, усилитель, аналого-цифровой преобразователь и выходной регистр, а также дешифратор адреса, выход которого соединен с программным параллельным интерфейсом, выходы которого соединены с всеми узлами преобразователя 3.

Табличный процессор 4 обеспечивает поточечное амплитудное преобразование яркостного сигнала в цифровой форме табличным способом по программно-задаваемой характеристике преобразования. Он выполнен по известной схеме, содержит на входе блок интерфейса, соединенный выходами с оперативным запоминающим блоком, выход которого через регистр связан с выходами процессора, мультиплексором адреса, другой вход которого соединен через регистр данных с входом видеосигнала процессора и схемой управления режимами оперативного запоминающего блока.

Коммутатор 5 обеспечивает возможность передавать видеосигнал, поступающий либо от преобразователя 3, либо от процессора 4, либо через вход 6 от внешнего устройства - датчика видеосигнала. Внешнее устройство подключается к входу 6 коммутатора, например, через буферный запоминающий блок (на фигурах не показан), считывание кодов информации из которого синхронизировано сигналами синхронизатора 2.

Коммутатор 5 (фиг. 2) содержит дешифратор 16, ключи 17, 19, 21, шинные формирователи 18, 20, 22, элементы ИЛИ 23 и 24, выход и входы (обозначены цифрами блоков, с выходами и входом которых они связаны на фиг. 1).

Арифметико-логический блок 7 обеспечивает арифметические и логические операции над кодами, поступающими от коммутатора 5 и блока 8, а также мультиплексирование кодов результатов операций. Блок 7 выполнен на четырех арифметико-логических микросхемах типа КР531ТИП3, которые связаны входами и выходами со схемой ускоренного переноса на микросхеме типа КР531ИП4. Входы каждой микросхемы КР531ИП3 связаны с двумя восьмиразрядными шинами, которые являются входными-выходными со стороны блока 8 памяти и через шинные формирователи подключены к входу блока 7 со стороны коммутатора 5, а выходы микросхем объединены в общую 16-разрядную шину, к которой подключена схема выбора восьмиразрядного кода на микросхемах типа 555ИР23, выходы которых являются выходом блока 7. Входы управления всех узлов блока 7, кроме схемы ускоренного переноса, соединены с выходами дешифратора адреса.

Блок 9 микропрограммного управления (фиг. 3) содержит системную шину 25, с которой связаны через шины блоки 2, 3-5, 10-12, 14, 15 по фиг. 1, а также микроЭВМ 26 и блок 27 управления записью-считыванием, выходы которого соединены с входами арифметико-логического блока 7 и блока 8 памяти. Структура микроЭВМ 26 выполнена на основе БИС комплекта К1810.

Коммутатор 10 обеспечивает переключение видеосигналов, поступающих или от блока 7, или от табличного процессора 11, или от входа 6 для внешних устройств. Структура его аналогична коммутатору на фиг. 2 ( цифры в скобках на фиг. 2 показывают номера блоков по фиг. 1, к которым подключены входы и выход коммутатора 10).

Табличный процессор 11 идентичен табличному процессору 4, но дополнительно формирует сигнал бинаризованного изображения. Узел бинаризации содержит коммутатор яркостного сигнала, выход которого соединен с входом оперативного запоминающего блока, выход которого является выходом бинаризированного сигнала табличного процессора, причем второй вход оперативного запоминающего блока и первый вход коммутатора соединены с дополнительными выходами интерфейса, а второй вход коммутатора - с выходом табличного процессора.

Формирователь 12 формирует полный телевизионный сигнал и преобразует его в аналоговую форму. Он содержит включенные последовательно между входом и выходом смеситель сигналов и цифроаналоговый преобразователь. Смеситель имеет дополнительные входы для сигнала рамки и других сигналов для формирования полного телевизионного сигнала.

Блок 14 селекции решает задачу выделения изображений объектов из совокупности бинарных сигналов изображений объектов, наблюдаемых датчиком 1 и содержит первый и второй блоки памяти, блок выборки данных, блок сканирования, третий блок памяти, ключ, элемент И-НЕ, элемент НЕ, формирователь сигнала маски и элемент И, выход которого является выходом блока 14. Функции блока управления выполняет микроЭВМ 26 через шину связи между блоками 9 и 14. Кроме того, в структуру устройства добавлен дополнительный третий вход элемента И, который является входом блока 14, соединенным с выходом формирователь 15.

Формирователь 15 сигналов контура и зоны анализа обеспечивает формирование сигналов, например, рамки и зоны, которую она ограничивает, а также сигналов размеров и координат положения рамки на экране видеоконтрольного блока 13. Формирователь 15 содержит соединенные последовательно пульт управления, коммутатор сигналов счета, которые поступают от микроЭВМ блока 9, счетчики координат по Х и по У, счетчики развертки по Х и по У и триггерную схему для формирования сигнала рамки и зоны, два выхода которой являются выходами формирователя 15, а также подключенный к выходам счетчиков координат, коммутатор координат рамки, выход которого через буферный узел подключен к блоку 9 управления, и селектор адреса, связанный с пультом управления.

Система работает следующим образом.

Видеосигнал - полный телевизионный сигнал - с выхода датчика 1 поступает на входы синхронизатора 2 и преобразователя 3. Синхронизатор из видеосигнала селектирует строчный и кадровый синхроимпульсы и формирует совокупность синхронизирующих управляющих и тактовых сигналов синхронно выделенным синхроимпульсам. Преобразователь 3 аналоговый видеосигнадл датчика 1 нормирует по амплитуде, преобразует в цифровую форму и выделяет на своем выходе видеосигнал в виде восьмиразрядного параллельного двоичного кода. Двоичный код видеосигнала поступает на входы табличного процессора 4 и коммутатора 5. Процессор 4 преобразует поточечно амплитуду яркостного сигнала табличным способом по программе, заданной микроЭВМ блока 9.

Обработанный табличным процессором видеосигнал поступает на другой вход коммутатора 5. Состоянием коммутатора управляет код, поступающий на вход дешифратора 16 от микроЭВМ 26 блока 9 управления. Код дешифрируется и выделяет сигнал управления на входе ключа 17, если обработка видеосигнала табличным процессором 4 исключается, ключа 19, если эта обработка видеосигнала проводится, ключа 21, если видеосигнал поступает от внешнего устройства. Упомянутый сигнал управления от дешифратора 16 подготавливает один из ключей 17, 19, 21 к работе. На второй вход ключей через элементы ИЛИ 23 и 24 поступает либо бинарный сигнал от селектора 14, либо потенциал от дешифратора 16.

В первом случае подготовленный к работе ключ открывается на время длительности бинарного сигнала наблюдаемых объектов, во втором - в течение времени, пока к дешифратору приложен соответствующий код от блока 9. Коммутации этих кодов во время передачи изображения телевизионного кадра может обеспечить передачу нескольких фрагментов. В этом случае последовательная передача фрагментов, например, от датчика 1 и через вход 6 коммутатора 5 вызывает отображение на экране видеоконтрольного блока 13 одновременно двух фрагментов изображений. Параметры, координаты и количество фрагментов задаются через микроЭВМ блока 9 управления.

С выхода коммутатора 5 код видеосигнала поступает на вход арифметико-логического блока 7. Этот блок производит вычитание, сложение, логические операции, например, в процессе накопления зашумленных сигналов малоконтрастных изображений наблюдаемых объектов над кодами видеосигналов, которые поступают от коммутатора 5 и из блока 8 памяти, а также мультиплексирование 16-разрядного кода результата произведенных в блоке операций в восьмиразрядный код и выдачу его на выход блока 7.

Блок 8 памяти осуществляет пословную и побайтную запись, хранение и считывание массива 16-разрядных двоичных кодов яркости двух изображений размером 512 x 512 слов, сигналы которых поступают через блок 7. Операции записи и считывания кодов обеспечивают сигналы блока 27 управления записью-считыванием.

Работа всех блоков системы управляется кодами, которые формирует по программе обработки изображений микроЭВМ 26 блока 9 управления (фиг. 4 и 5). Код блока управления содержит адрес блока, которому направляется воздействие, и команду по управлению работой этого блока. Код адреса подготавливает конкретный блок для управления, а код команды обеспечивает проведение той или иной операции в блоке. Коды блока управления передаются по связям блока 9 с другими блоками системы через дешифраторы адреса. По связям блока 9 с другими блоками передаются также тактовые сигналы и сигналы синхронизации, которые формирует синхронизатор 2, они поступают через соответствующий вход блока 9.

С выхода арифметико-логического блока 7 видеосигнал поступает на входы табличного процессора 11 и коммутатора 10. Табличный процессор 11 обеспечивает преобразование яркостного видеосигнала в цифровой форме табличным способом, формирование сигнала бинаризованного изображения номинального уровня. Обработанные коды видеосигнала поступают на другой вход коммутатора 10. Коммутатор 10 в зависимости от команды блока 9 управления обеспечивает передачу на свой выход видеосигнала, который поступает либо от арифметико-логического блока 7, либо от табличного процессора 11, либо через вход 6. Видеосигнал, поступающий от арифметико-логического блока непосредственно через коммутатор 10 табличным процессором 11 не обрабатывается.

Формирователь 12 из цифрового кода и других необходимых сигналов, поступающих от блока 9, формирует на своем выходе аналоговый полный телевизионный сигнал, который поступает в видеоконтрольное устройство 13 для визуального отображения обработанного телевизионного изображения.

Бинарный сигнал изображения с выхода табличного процессора 11 поступает на вход блока 14 селекции. Под управлением микроЭВМ блок 14 выделяет бинарные сигналы объектов из совокупности тактовых в поле зрения датчика 1 видеосигналов. Бинарные видеосигналы объектов поступают на входы коммутаторов 5, 10 и участвуют в управлении их работой путем стробирования видеосигналов объектов, поступающих на входы коммутаторов.

Формирователь 15 в целях ограничения фрагмента изображения, выбранного на экране видеоконтрольного блока для анализа, вырабатывает сигналы рамки и зоны анализа, размеры и координаты которых выбирает оператор через пульт управления. Сигнал рамки замешивается в видеосигнал формирователем 12 и передается с ним для визуального отображения на видеоконтрольный блок 13. Сигнал зоны анализа поступает на вход блока 14 и обеспечивает стробирование сигналов объектов, ограниченных рамкой, на экране блоков 13. Данные о рамке и зоне анализа передаются через вход блока 9 в микроЭВМ и используются при обработке изображений, в частности, для управления работой коммутаторов 5 и 10 для стробирования выбранного оператором фрагмента изображения и подавления информации за пределами рамки.

Стробирование фрагментов изображения рамкой и бинарным сигналом объектов открывает возможность производить повторную обработку и более детальный анализ изображений, например малоконтрастных зашумленных частей объекта. В этом случае табличный процессор 11 формирует бинарный сигнал на уровне, превышающем амплитуды сигнала малоконтрастных объектов, и инвертирует его. Этот сигнал через блок 14 управляет работой коммутаторов 5 и 10, стробируя видеосигнал малоконтрастных изображений и подавляя видеосигнал выше уровня в процессоре 11. Дополнительное накапливание сигнала малоконтрастных неподвижных изображений в блоке памяти повышает информативность хранимого там изображения кадра.

По сравнению с прототипом заявляемая система имеет дополнительные функциональные возможности - это возможность выбора и обеспечения выполнения дополнительных процессов, например сложения, вычитания, табличного преобразования и других видов обработки видеосигналов объектов или их фрагментов, выбранных для анализа в результате первичной обработки изображения с целью получения дополнительной информации об объектах, а также возможность принимать и обрабатывать дополнительную телевизионную или другую информацию, поступающую по линии связи от внешних устройств, в реальном масштабе времени, обрабатывать информацию двух или более направлений с временным разделением каналов. (56) 1. Авторское свидетельство СССР N 1462360, кл. G 06 F 15/66, 1986.

2. Проспект фирмы IOICE-LOEBLE, аппаратура МАGISCAN.

| название | год | авторы | номер документа |

|---|---|---|---|

| СИСТЕМА ДЛЯ ОБРАБОТКИ ИЗОБРАЖЕНИЙ | 1990 |

|

RU2006942C1 |

| ТЕЛЕВИЗИОННЫЙ АНАЛИЗАТОР НА МАТРИЦЕ ПРИБОРОВ С ЗАРЯДОВОЙ СВЯЗЬЮ | 1993 |

|

RU2040862C1 |

| УСТРОЙСТВО ДЛЯ ВВОДА-ВЫВОДА ИЗОБРАЖЕНИЙ | 1993 |

|

RU2066928C1 |

| УСТРОЙСТВО ДЛЯ ВВОДА-ВЫВОДА ПОСЛЕДОВАТЕЛЬНОСТИ КАДРОВ ТЕЛЕВИЗИОННОГО ИЗОБРАЖЕНИЯ | 1993 |

|

RU2066929C1 |

| УСТРОЙСТВО ДЛЯ ВВОДА И СРАВНЕНИЯ ТЕЛЕВИЗИОННЫХ ИЗОБРАЖЕНИЙ | 1993 |

|

RU2096922C1 |

| УСТРОЙСТВО ВОСПРОИЗВЕДЕНИЯ ИЗОБРАЖЕНИЙ ИНТЕРФЕРОГРАММ | 1992 |

|

RU2030841C1 |

| ОХРАННАЯ ТЕЛЕВИЗИОННАЯ СИСТЕМА | 2000 |

|

RU2231123C2 |

| ТЕЛЕВИЗИОННАЯ КАМЕРА С СЕЛЕКТИВНЫМ МАСШТАБИРОВАНИЕМ | 1999 |

|

RU2171014C2 |

| УСТРОЙСТВО ДЛЯ ВВОДА И ВЫВОДА ИЗОБРАЖЕНИЙ ОБЪЕКТОВ | 1993 |

|

RU2065204C1 |

| ТЕЛЕВИЗИОННАЯ КАМЕРА С СЕЛЕКТИВНЫМ МАСШТАБИРОВАНИЕМ | 2000 |

|

RU2199828C2 |

Изобретение относится к системам цифровой обработки телевизионной информации, в частности к устройствам автоматического анализа изображений. Целью изобретения является расширение функциональных возможностей за счет увеличения количества вариантов обработки, в том числе фрагментов изображений. Цель достигается тем, что система содержит датчик 1 видеосигнала, синхронизатор 2, преобразователь 3 видеосигнала, табличный процессор 4, коммутатор 5 с информационным входом 6, арифметико-логический блок 7, блок 8 памяти, блок 9 микропрограммного управления, коммутатор 10, табличный процессор 11, формирователь 12 полного телевизионного сигнала, видеоконтрольный блок 13, блок 14 селекции, формирователь 15 сигнала контура и зоны анализа. 5 ил.

УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ИЗОБРАЖЕНИЙ, содержащее преобразователь видеосигнала в цифровой код, синхронизатор, первый и второй блоки амплитудного преобразования яркостного сигнала, арифметико-логический блок, преобразователь телевизионного сигнала в цифроаналоговый, блок памяти, блок микропрограммного управления и видеоконтрольный блок, причем вход видеосигнала устройства подключен к входу режима синхронизатора и к информационному входу преобразователя видеосигнала в цифровой код, выходы которого подключены соответственно к информационным входам первого блока амплитудного преобразования яркостного сигнала, выход синхронизатора подключен к входу режима блока микропрограммного управления, выходы первой группы которого подключены соответственно к управляющим входам преобразователя видеосигнала в цифровой код и соответственно к управляющим входам первого блока амплитудного преобразования, выходы второй, третьей и четвертой групп блока микропрограммного управления подключены соответственно к входам кода операции арифметико-логического блока, к управляющим и адресным входам блока памяти, информационные входы-выходы которого подключены соответственно к информационным входам-выходам арифметико-логического блока, выходы которого подключены соответственно к информационным входам второго блока амплитудного преобразования яркостного сигнала, выходы пятой группы блока микропрограммного управления подключены соответственно к управляющим входам второго блока амплитудного преобразования яркостного сигнала и к управляющим входам преобразователя телевизионного сигнала в цифроаналоговый, выход которого подключен к входу видеоконтрольного блока, отличающееся тем, что, с целью расширения функциональных возможностей путем увеличения числа вариантов обработки и фрагментов изображений, оно содержит блок селекции сигналов, формирователь сигнала контура и зоны анализа, первый и второй коммутаторы, при этом входы видеосигнала первой и второй групп устройства подключены соответственно к информационным входам первых групп первого и второго коммутаторов, выходы первого блока амплитудного преобразования яркостного сигнала, выходы преобразователя видеосигнала в цифровой код и выходы первой группы блока микропрограммного управления подключены соответственно к информационным входам второй и третьей групп и к управляющим входам группы первого коммутатора, выходы которого подключены соответственно к информационным входам арифметико-логического блока, выходы которого подключены соответственно к информационным входам второй группы второго коммутатора, выходы которого поключены к информационным входам группы преобразователя телевизионного сигнала в цифроаналоговый, информационный вход которого подключен к первому выходу формирователя сигнала контура и зоны анализа, выходы пятой группы блока микропрограммного управления подключены соответственно к управляющим входам группы второго коммутатора, входы-выходы первой и второй групп блока микропрограммного управления подключены соответственно к управляющим входам-выходам блока селекции сигналов и к информационным входам-выходам формирователя сигнала контура и зоны анализа, второй выход которого подключен к первому информационному входу блока селекции сигналов, выход которого подключен к управляющим входам первого и второго коммутаторов, выходы группы и выход второго блока амплитудного преобразования яркостного сигнала подключены соответственно к информационным входам третьей группы второго коммутатора и к второму информационному входу блока селекции сигналов, вход размера рамки и зоны анализа устройства подключен к информационному входу формирователя сигнала контура и зоны анализа.

Авторы

Даты

1994-01-30—Публикация

1990-05-17—Подача