Изобретение относится к системам цифровой обработки телевизионной информации и может быть использовано в устройствах автоматического анализа изображений.

Известно устройство для обработки изображений, которое содержит блок синхронизации, первый и второй блоки памяти, блок сдвига, мультиплексор, генератор тактовых импульсов, счетчики, сумматор и дешифратор.

Известно другое устройство для обработки сигналов изображения, которое содержит синхрогенератор, датчик сигналов изображений, видеоконтрольный блок, цифроаналоговый преобразователь, первый и второй блоки нормализации сигнала изображения, первый и второй блоки сопряжения, блок управления и вычисления.

Недостаток известных устройств - в узкие функциональные возможности по обработке изображений.

Наиболее близкой по технической сущности к заявляемой является выбранная в качестве прототипа система анализа изображений, которая содержит соединенные последовательно телевизионную камеру, аналого-цифровой преобразователь, входную просмотровую таблицу, к выходу которой подключен блок памяти, соединенные последовательно от блока памяти выходную просмотровую таблицу, цифроаналоговый преобразователь и мониторы, а также арифметико-логическое устройство, соединенное с микропрограммным контроллером, а через магистральную шину с блоком адресов, блоком памяти и контроллером интерфейса, который связан с дисковой памятью и пультом управления.

Недостаток прототипа заключается в недостаточности функциональных возможностей по обработке информации состояний объектов, например перемещающихся объектов, с подавлением изображений объектов, координаты которых не меняются, а также оценке параметров движения объектов (относительная скорость, направление движения и другие параметры).

Цель изобретения - расширение функциональных возможностей за счет учета анализа состояний объектов в динамике.

Цель достигается тем, что в систему, содержащую последовательно соединенные преобразователь видеосигнала, блок обработки изображений, блок управления, формирователь телевизионного сигнала и синхронизатор, введены блок селекции изображений, формирователь сигналов стробирования и контуров объектов, коммутатор, процессор, арифметико-логический узел и второй табличный процессор, включенный между входом и тремя выходами узла, второй вход которого соединен с входами управления первого, второго табличных процессоров и узла управления записью, первый и второй выходы которого соединены с вторым входом арифметико-логического узла и входом узла памяти, связанных между собой входом-выходом и выходом-входом.

Цель достигается также тем, что коммутатор содержит соединенные последовательно дешифратор, ключи и шинные формирователи, включенные между входом и информационными входами и выходом коммутатора, второй вход которого является входом элемента ИЛИ, второй вход которого соединен с дополнительным выходом дешифратора, а выход - с вторыми входами ключей.

Цель достигается также тем, что формирователь сигналов содержит узел управления, выход которого соединен с входами анализатора состояний объектов и связанного с ним селектора сигналов контуров, выходы которого являются выходами формирователя сигналов.

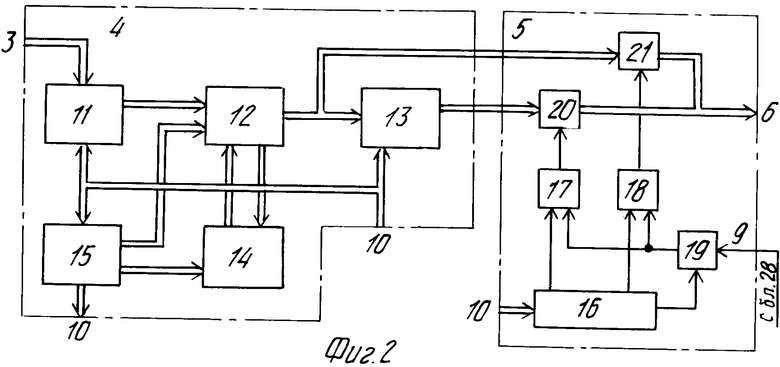

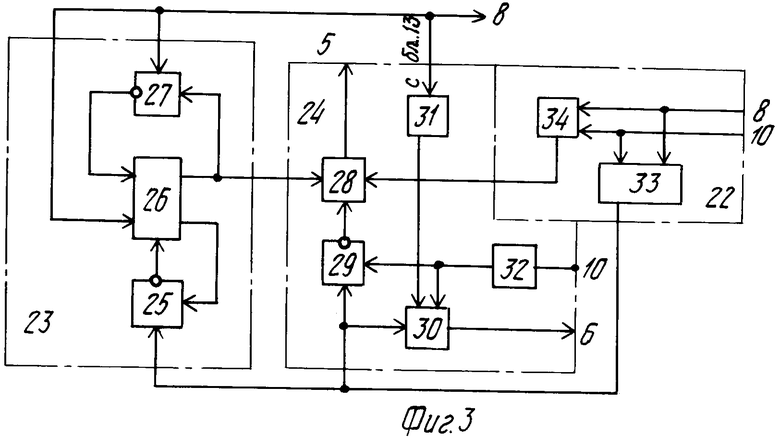

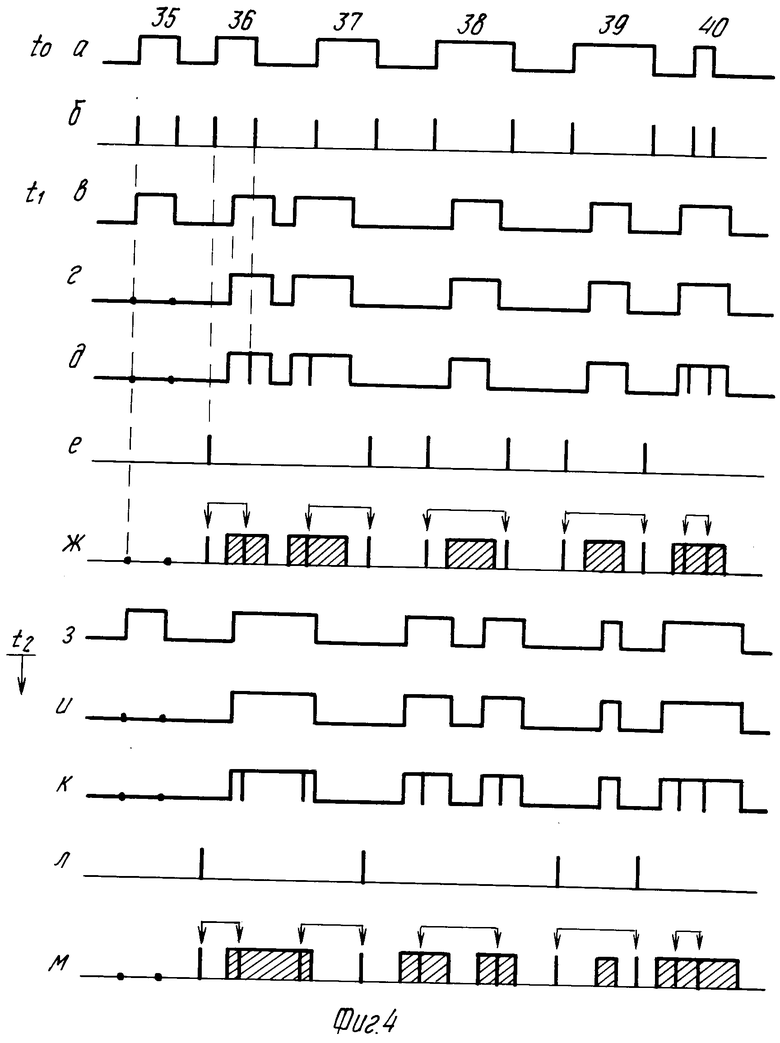

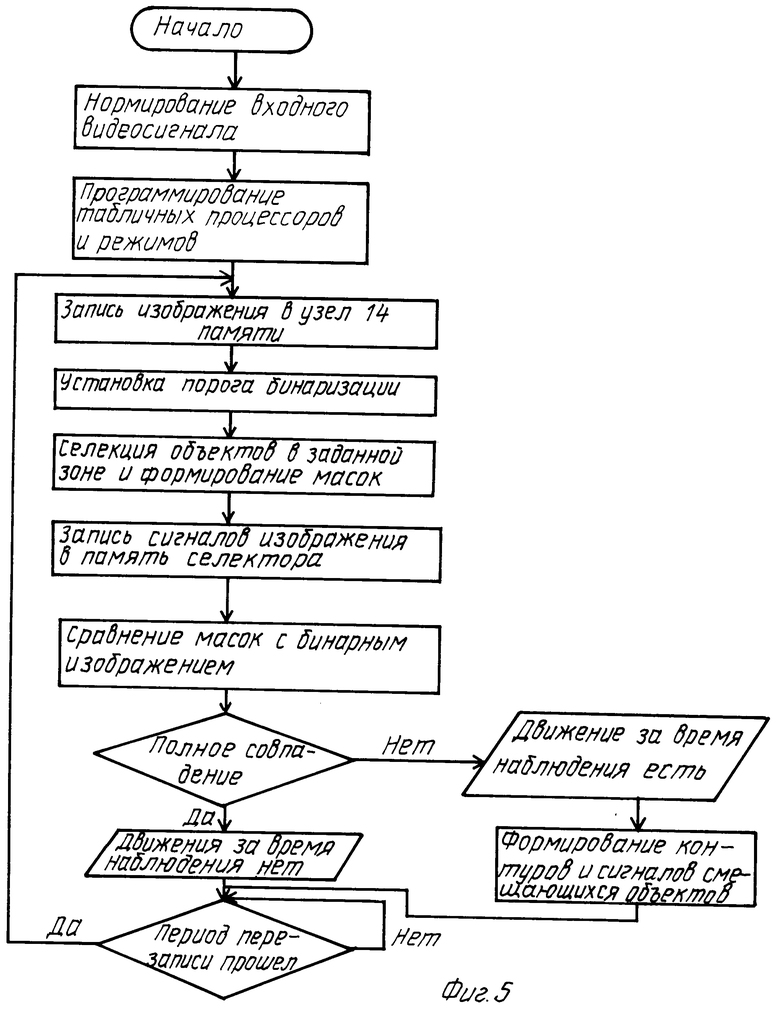

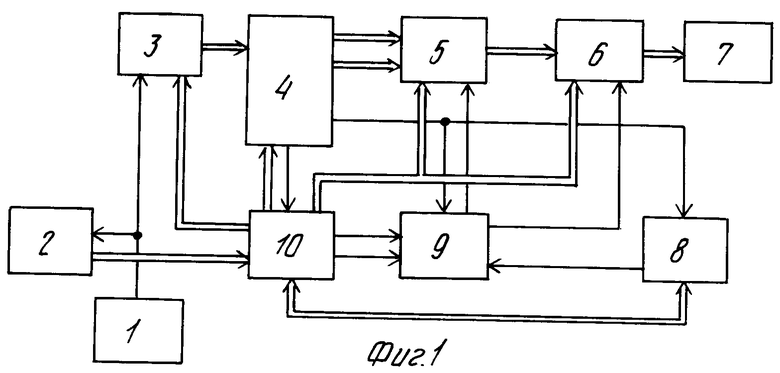

На фиг. 1 представлена блок-схема системы; на фиг. 2 - вариант выполнения блока обработки изображений и коммутатора; на фиг. 3 - вариант выполнения формирователя сигналов стробирования и контуров объектов; на фиг. 4 - временные диаграммы, поясняющие работу системы; на фиг. 5 - алгоритм работы системы.

Система для обработки изображений содержит датчик 1 телевизионного сигнала, синхронизатор 2, преобразователь 3 видеосигнала, блок 4 обработки изображений, коммутатор 5, формирователь 6 телевизионного сигнала, видеоконтрольный блок 7, блок 8 селекции изображений, формирователь 9 сигналов стробирования и контуров объектов, блок 10 управления.

В качестве датчика 1 может быть использована передающая телевизионная камера любого типа с вещательным стандартом. Синхронизатор 2 содержит селектор сигналов синхронизации из полного телевизионного сигнала, который связан с входом синхронизатора, а выходом с узлами формирования сигнала таковой частоты и сигнала синхронизации, выходы которых являются выходами синхронизатора.

Преобразователь 3 видеосигнала содержит включенные последовательно между информационными входом и выходом преобразователя узел замеса уровня черного, узел регулировки размаха видеосигнала, усилитель, аналого-цифровой преобразователь и выходной регистр, а также на управляющем входе дешифратор адреса, выход которого соединен с программным параллельным интерфейсом, выходы которого соединены с всеми узлами преобразователя 3.

Блок 4 обработки изображений (фиг. 2) содержит первый табличный процессор 11, арифметико-логический узел 12, второй табличный процессор 13, узел 14 памяти, узел 15 управления записью и считыванием. Табличный процессор 11 выполнен по известной схеме. Он содержит на входе узел интерфейса адреса, соединенный выходами с оперативным запоминающим узлом, выход которого через регистры связан с выходом процессора, мультиплексором адреса, другой вход которого соединен через регистр данных с входом видеосигнала процессора, и схемой управления режимами оперативного запоминающего узла. Второй табличный процессор 13 блока 4 отличается от первого тем, что дополнительно содержит коммутатор яркостного сигнала, выход которого соединен с входом второго оперативного запоминающего узла, выход которого является вторым выходом второго табличного процессора и блока 4 (выход бинарного сигнала), причем второй вход второго оперативного запоминающего узла и первый вход коммутатора соединены с дополнительными выходами узла интерфейса адреса процессора 13, а второй вход коммутатора соединен с первым выходом процессора 13 и блока 4.

Арифметико-логический узел 12 содержит четыре арифметико-логических микросхемы типа КР531ИП3, которые связаны входами и выходами со схемой ускоренного переноса на микросхеме типа КР531ИП4. Входы каждой микросхемы КР531ИП3 связаны с двумя восьмиразрядными шинами, которые являются входными со стороны узла 14 памяти и через шинные формирователи подключены к выходу первого табличного процессора 11, а выходы микросхем объединены в общую 16-разрядную шину, которая является выходной в сторону узла 14 памяти и к которой подключена схема выбора восьмиразрядного кода на микросхеме типа 555ИР23, выходы которой являются другим выходом арифметико-логического узла. Входы управления всех схем арифметико-логического узла, кроме схемы ускоренного переноса, соединены с выходами дешифратора адреса, вход которого соединен с выходом узла 15 управления записью и считыванием.

Узел 14 памяти имеет два листа памяти, каждый из которых через схему записи и считывания связан с входными шинами узла 12, общей выходной шиной узла 12 и выходом узла 15 управления записью и считыванием.

Коммутатор 5 (фиг. 2) содержит дешифратор 16, ключи 17 и 18, элемент ИЛИ 19 и шинные формирователи 20 и 21, информационные входы которых являются входами коммутатора, которые соединены с выходами блока 4, а информационные выходы объединены выходом коммутатора.

Формирователь 6 телевизионного сигнала содержит между входом и выходом включенные последовательно смеситель сигналов и цифроаналоговый преобразователь, причем смеситель имеет входы подачи сигналов для формирования полного телевизионного сигнала от блока 10 управления и дополнительных сигналов от формирователя 9.

Блок 8 селекции изображений выполнен по известной схеме 4 содержит первый, второй и третий блоки памяти, блок выборки данных, блок сканирования, ключ, элемент И-НЕ, элемент НЕ, формирователь сигналов маски, элемент И и блок управления. Функции блока управления выполняет блок 10 управления.

Формирователь 9 сигналов стробирования и контуров объектов (фиг. 3) содержит узел 22 управления, анализатор 23 состояний объектов и селектор 24 сигналов контуров объектов. Анализатор 23 содержит элемент И-НЕ 25, триггер 26 и элемент И-НЕ 27, селектор 24 - элемент И 28, элемент И-НЕ 29, элемент И 30, расширитель 31 импульсов и триггерный делитель 32 частоты, а узел 22 управления - генератор 33 коротких импульсов и элемент ИЛИ 34.

Блок 10 управления содержит системную шину, которая объединяет все выходы, входы блока 10 и связана с микроЭВМ, структура которой выполнена на основе БИС комплекта К1810. Работа микроЭВМ соответствует алгоритму, приведенному на фиг. 5.

Система работает следующим образом.

Полный телевизионный сигнал с выхода датчика 1 поступает на входы синхронизатора 2 и преобразователя 3. Синхронизатор выделяет синхросигналы строчной и кадровой частот и формирует синхронизирующие и тактовые сигналы синхронно выделенными. Эти сигналы поступают в блок 10 управления, где распределяются по блокам системы согласно алгоритму обработки изображений. Преобразователь 3 аналоговый видеосигнал датчика 1 нормализует по амплитуде до номинальной, преобразует в цифровую форму и выделяет на своем выходе видеосигнал в виде восьмиразрядного параллельного двоичного кода. Блок 4 обрабатывает видеосигналы изображения по программе, которая задается через микроЭВМ блока 10 управления.

Процессор 11 преобразует поточечно амплитуду яркостного сигнала в цифровой форме табличным способом по программно-задаваемой характеристике преобразования. Арифметико-логический узел 12 производит операции сложения, вычитания и логические операции над кодами видеосигнала, поступающими от процессора 11 и узла 14, например операции сложения кодов в процессе накопления малоконтрастных зашумленных сигналов и выдачи их суммы в узел 14 памяти, а также мультиплексирования 16-разрядного кода результата произведенных в узле 12 операций в восьмиразрядный код и выдачи его на выход блока 4 обработки и вход коммутатора 5.

Узел 14 под управлением узла 15 осуществляет пословную и побайтную запись 16-разрядных двоичных кодов яркости, хранение массива кодов яркости двух изображений на отдельных листах памяти и считывание кодов этих изображений для арифметико-логических операций в узле 12 в процессе их обработки. При этом возможен ряд программ по обработке изображений, например предварительная запись на первый лист памяти фона видеосигнал датчика 1 без наблюдаемых объектов, считывание из узла 14 и вычитание в узле 12 кодов этого фона из кодов текущего видеосигнала с изображением наблюдаемых объектов, поступающих от процессора 11.

Выходной сигнал узла 12 может быть обработан дополнительно процессором 13. Он обеспечивает преобразование яркостного видеосигнала табличным способом аналогично процессору 11 и дополнительно формирование сигнала бинаризованного изображения номинального уровня.

Коммутатор 5 в зависимости от команды управления обеспечивает передачу кодов видеосигнала на свой выход либо обработанных, либо необработанных в процессоре 13, а также стробирование выбираемой части этих кодов. Команда управления коммутатором поступает от блока 10 на дешифратор 16. Выделенный на выходе дешифратора сигнал совместно с сигналом через элемент ИЛИ 19 открывают один из ключей 17 или 18 и соответствующий ему шинный формирователь 20 или 21 для прохождения кодов видеосигнала через коммутатор. Для передачи коммутатором 5 всех кодов видеосигнала на свой выход на выход элемента ИЛИ 19 от дешифратора 16 поступает сигнал, который блокирует действие сигналов стробирования с входа 9.

Формирователь 6 формирует полный телевизионный сигнал и преобразует его в аналоговую форму для визуализации обработанных изображений на экране видеоконтрольного блока 7.

Бинарный сигнал изображений объектов с выхода процессора 13 блока 4 поступает на вход селектора 8, который по программе блока 10 обеспечивает последовательное или выборочное по порядковому номеру обработки выделение сигналов масок изображений объектов.

Формирователь 9 выделяет соответствующие маскам сигналы стробов, которые воздействуют на коммутатор 5. Стробы поступают на вход элемента ИЛИ 19 и стробируют цифровые коды сигналов объектов, выбранных для отображения на экране блока 7 (сигнал блокировки от дешифратора 16 на элемент ИЛИ 19 в этом случае не поступает).

Во время наблюдения за динамикой объектов бинарный сигнал изображений после записи его в запоминающий узел селектора 8 сохраняется там на время наблюдений. С момента записи to в течение времени t1, t2. . . tn наблюдений селектор 8 при каждом телевизионном кадре генерирует сигналы масок, например объектов 35-40, на момент их записи (фиг. 4а). Частота смены содержимого запоминающего узла селектора 8 задается программно через блок 10 управления.

Сигналы масок и сигнал-потенциал от блока 10 поступают на входы генератора 33 и элемента ИЛИ 34 формирователя 9. Генератор выделяет короткие импульсы (фиг. 4б), соответствующие фронтам сигнала масок, а элемент ИЛИ 34 удерживает элемент И 28 в открытом состоянии. Короткие импульсы через открытый элемент И-НЕ 25 воздействуют на установочный вход триггера 28.

Бинарный во время t1 или t2 сигнал от блока 4 поступает на первый вход триггера 26 (фиг. 4в и 4з). Если сигналы на установочном и первом входам триггера совпадают во времени (см. объект 3б), то триггер не переключается и на выходе 5 формирователя 9 сигнал строба отсутствует (фиг. 4г и 4и). Это свидетельствует о том, что объект 35 во время t1 и t2 относительно времени to своего состояния не изменяет. Коммутатор 5 объект 35 для отображения на экране блока 7 не стробирует.

Если сигналы на входах триггера не совпадают во времени (см. объекты 36-40), то триггер 26 переключается передним фронтом бинарного сигнала от блока 4 и возвращается в исходное состояние задним фронтом того же сигнала, прошедшего через элемент И-НЕ 27 на второй вход триггера. Выделенные триггером стробы через открытый элемент И 28 поступают на вход коммутатора 5 для стробирования сигналов объектов 36-40, которые находятся в состоянии движения относительно времени to.

Одновременно для расширения функциональных возможностей анализа изображений на экране блока 7, например определения относительных скорости, направления или траектории движения объектов, формирователь 9 выделяет сигналы контуров, соответствующих положениям объектов в момент to начала наблюдения. Для этого короткие импульсы генератора 33 поступают на элементы И-НЕ 29 и И 30. Элемент И-НЕ 29 совместно с элементом И 28 формирует часть сигнала каждого контура, которая налагается на сигнал строба (совпадает во времени), а элемент И 30 совместно с расширителем 31, который увеличивает длительность входных сигналов на время длительности импульсов генератора 33 и инвертирует их, формирует другую часть сигнала контура, которая не налагается на сигнал строба, формируемого триггером 26. В первом случае элемент И 28 выделяет стробы и врезанные в него сигналы контуров объектов (фиг. 4д и 4к), которые через коммутатор 5 на экране блока 7 формируют часть контуров, подсвеченную более темным цветом, чем изображения объектов. Во втором случае элемент И 30 выделяет сигналы контуров объектов (фиг. 4е и 4л), которые как дополнительные для формирователя 6 замешиваются в телевизионный сигнал и на экране блока 7 формируют вторую часть контуров, но подсвеченную белым цветом. Темная и светлая части контура обеспечивают более четкое и в динамике разделение изображений объектов.

Кроме того, элементы И-НЕ 29 и И 30 под воздействием сигналов кадровой частоты с входа 10 и через делитель 32 обеспечивают визуально наблюдаемое пульсирование контуров изображений объектов. Это создает дополнительные положительные наблюдения изображений объектов.

На фиг. 4ж и 4м показаны суммарные сигналы объектов (условно бинарные) и контуров в полном телевизионном сигнале, причем знаком  показаны сигналы контуров, а штриховкой - сигналы объектов, находящихся в движении. Видно, что объект 36 смещается вправо по фиг. 4, объект 37 - влево и во время t2 они накладываются друг на друга, объект 38 сужается во время t1 и раздваивается вo время t2, объекты 39 и 40 передвигаются вверх и вниз соответственно.

показаны сигналы контуров, а штриховкой - сигналы объектов, находящихся в движении. Видно, что объект 36 смещается вправо по фиг. 4, объект 37 - влево и во время t2 они накладываются друг на друга, объект 38 сужается во время t1 и раздваивается вo время t2, объекты 39 и 40 передвигаются вверх и вниз соответственно.

Для стробирования коммутатором 5 всех объектов, сигналы которых бинаризированы блоком 4, без подавления сигналов объектов, которые находятся в состоянии покоя, от блока 10 управления поступает сигнал на вход генератора 33 и элемент ИЛИ 34. Генератор прекращает формировать импульсы и тем самым обеспечивает работу триггера 26 по всем входным сигналам блока 4. Через элемент ИЛИ 34 в этом случае на вход элемента И 28 подается сигнал маски от блока 8 селекции с обеспечением возможностей этого блока. (56) Авторское свидетельство СССР N 1464176, кл. G 06 F 15/66, 1987.

Авторское свидетельство СССР N 1462360, кл. G 06 F 15/66, 1986.

Проспект фирмы Joice-Loebl, аппаратура MАCISCАN.

Гуднев А. Г. и др. Табличный процессор и его применение для цифровой обработки изображений. - Техника кино и телевидения, N 9, 1986, с. 29, рис. 1.

Изобретение относится к системам цифровой обработки телевизионной информации и может быть использовано в устройствах автоматического анализа изображений. С целью расширения функциональных возможностей в систему, содержащую синхронизатор, преобразователь видеосигнала, блок обработки изображений, формирователь телевизионного сигнала, блок управления, введены коммутатор, блок селекции изображений и формирователь сигналов стробирования и контуров объектов. 2 з. п. ф-лы, 5 ил.

Авторы

Даты

1994-01-30—Публикация

1990-05-14—Подача