Изобретение относится к технологии изготовления интегральных схем, преимущественно на основе базового матричного кристалла (БМК).

Известен способ изготовления ИС, по которому на стадии металлизации полупроводниковой пластины проверяют целостность металлизации путем сканирования электронным лучом и затем испытывают работоспособность транзистора тем же сканирующим лучом, и по изменению электрического тока луча судят об электрической целостности и наличии физических дефектов в транзисторе [1] .

По известному способу упомянутые испытания проводят уже на готовых пластинах (на стадии нанесения межсоединений), т. е. осуществляется простая диагностика пластин, их структур. Кроме того, невозможно использовать результаты испытаний для исправления состояния пластин, а можно лишь констатировать, исправлен или дефектен тот или иной активный элемент (транзистор).

Наиболее близким к изобретению является способ изготовления ИС, по которому на матрицу схем, содержащую избыточное количество активных элементов, наносят межсоединения по заранее разработанной топологии, затем контролируют каждую отдельную изолированную схему и, поскольку имеется доступ к каждой ячейке матрицы схем (схемы подключены к общей шине), изолируют непригодные к работе схемы и соединяют исправные схемы [2] .

Этот способ связан с большими затратами времени на тестирование схем. Применение способа возможно при резервировании достаточно крупных блоков схем, что связано с увеличением неиспользуемой площади матрицы, что, в свою очередь, приводит к увеличению материальных затрат на изготовление схем.

Целью изобретения является повышение выхода годных ИС.

Для достижения цели предлагается способ изготовления ИС, преимущественно на основе БМК, содержащих избыточное количество активных элементов (транзисторов), включающий контроль исправности отдельных элементов путем подачи управляющих сигналов и использование только исправных элементов. Сначала на ранней стадии изготовления ИС до изготовления межсоединений формируют контрольную металлизацию и одновременно с подачей необходимого напряжения питания и управляющих сигналов определяют состояние элементов, например, методом наведенного тока или потенциального контраста при сканировании БМК оптическим или электронным зондом. При этом фиксируют координаты неисправных элементов. Затем удаляют контрольную металлизацию и изготавливают межсоединения только исправных элементов, обычно методом бесшаблонной литографии.

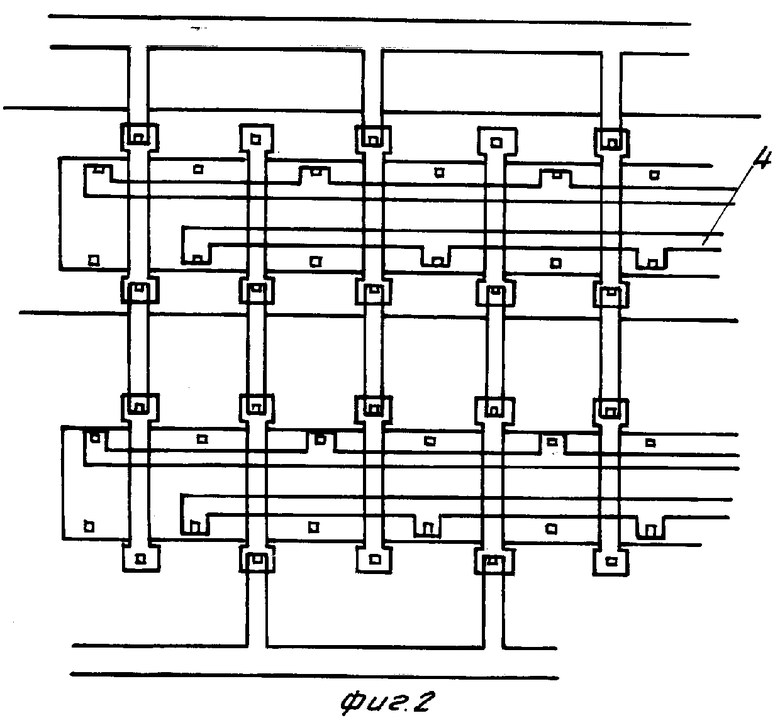

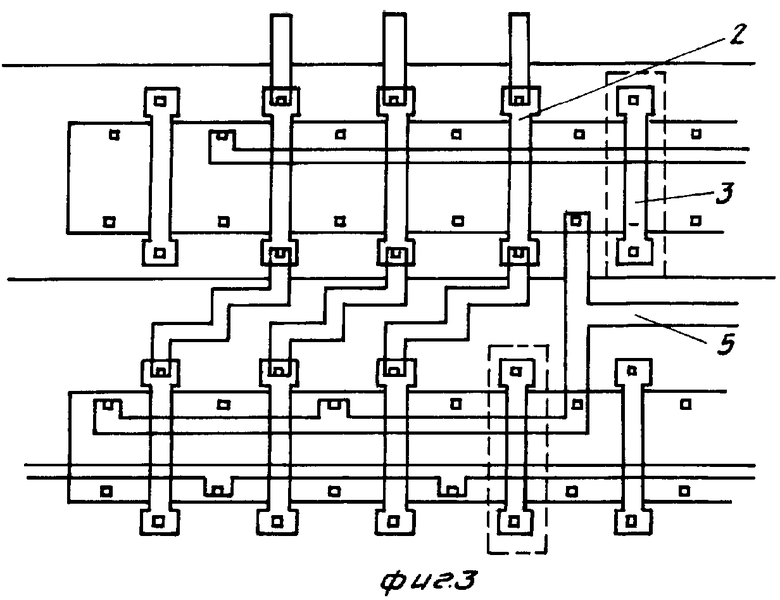

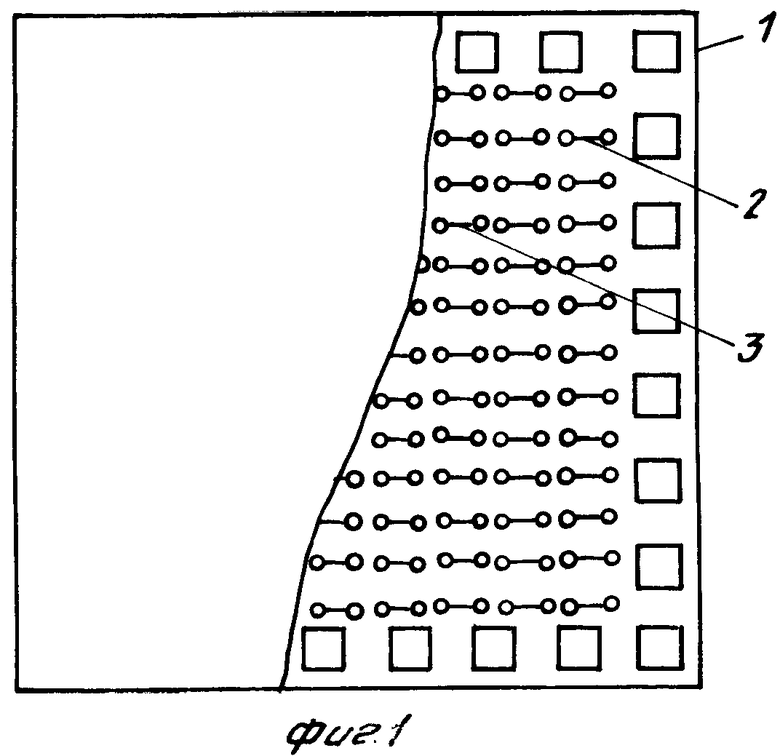

На фиг. 1 - ИС, например, базовый матричный кристалл (БМК) со случайно распределенными исправными и дефектными элементами; на фиг. 2 - фрагмент ИС с нанесенной контрольной металлизацией для поэлементного тестирования; на фиг. 3 - фрагмент ИС с нанесенными межсоединениями.

В соответствии с предложением авторов изготовление ИС, преимущественно на основе БМК, осуществляется с помощью следующих приемов и средств и в такой последовательности.

На ИС 1 (фиг. 1) со случайно распределенными исправными 2 и дефектными 3 активными элементами на ранней стадии изготовления наносится контрольная металлизация 4 (фиг. 2) для подачи напряжения питания и управляющих сигналов. Проводят тестирование ИС сканирующим электронным или оптическим лучом методом наведенного тока или потенциального контраста. В процессе контроля (тестирования) определяются и фиксируются координаты дефектных элементов 3. Удаляют контрольную металлизацию 4 и создают межсоединения 5 исправных элементов 2 методом бесшаблонной литографии.

Для осуществления способа в одном из конкретных примеров на ИС 1 со случайно распределенными и избыточными активными элементами на ранней стадии изготовления наносится контрольная металлизация из напыленного алюминия толщиной 0,5-0,6 мкм. Подается напряжение питания, соответствующее определенному типу ИС (5-24 В), и управляющие сигналы (например, для ТТЛ низкого уровня Vi - 0,4 В, высокого уровня Vн ≥ 2,4 В). Проводят тестирование сканирующим лучом (ток электронного луча ≈ 10 мА, ускоряющее напряжение 15 кВ). Измеряют и анализируют наведенный ток в каждом активном элементе 2,3. Устанавливают дефектные элементы 3, фиксируют их координаты путем определения положения луча при прохождении им дефектного элемента. Удаляют контрольную металлизацию методом травления. Создают межсоединения, например, из напыленного алюминия толщиной 1-1,5 мкм методом бесшаблонной литографии, используя информацию о координатах дефектных элементов. (56) 1. Патент Великобритании N 2185327, кл. Н 01 L 21/66, 1987.

2. Патент ФРГ N 3503433, кл. Н 01 L 21/88, 1985.

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ выявления дефектов в полевых транзисторах Шоттки, изготовленных на полупроводниковых материалах AB | 2022 |

|

RU2792259C1 |

| СПОСОБ ПРЕОБРАЗОВАНИЯ ИНФОРМАЦИИ ПРИ ПРОЕКТИРОВАНИИ И ТРАССИРОВКЕ БАЗОВЫХ МАТРИЧНЫХ КРИСТАЛЛОВ И БАЗОВЫЙ МАТЕРИЧНЫЙ КРИСТАЛЛ (ЕГО ВАРИАНТЫ) | 1991 |

|

RU2012099C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МОЩНОГО НИТРИД-ГАЛЛИЕВОГО ПОЛЕВОГО ТРАНЗИСТОРА | 2017 |

|

RU2668635C1 |

| Способ изготовления СВЧ полевого мощного псевдоморфного транзистора | 2016 |

|

RU2633724C1 |

| Способ формирования объемного рисунка межсоединений | 2015 |

|

RU2647879C2 |

| ВСТРАИВАЕМАЯ С СБИС ТЕХНОЛОГИИ КМОП/КНИ ПАМЯТЬ "MRAM" И СПОСОБ ЕЕ ИЗГОТОВЛЕНИЯ (ВАРИАНТЫ) | 2012 |

|

RU2532589C2 |

| ЭЦР-ПЛАЗМЕННЫЙ ИСТОЧНИК ДЛЯ ОБРАБОТКИ ПОЛУПРОВОДНИКОВЫХ СТРУКТУР, СПОСОБ ОБРАБОТКИ ПОЛУПРОВОДНИКОВЫХ СТРУКТУР, СПОСОБ ИЗГОТОВЛЕНИЯ ПОЛУПРОВОДНИКОВЫХ ПРИБОРОВ И ИНТЕГРАЛЬНЫХ СХЕМ (ВАРИАНТЫ), ПОЛУПРОВОДНИКОВЫЙ ПРИБОР ИЛИ ИНТЕГРАЛЬНАЯ СХЕМА (ВАРИАНТЫ) | 2003 |

|

RU2216818C1 |

| СПОСОБ ИССЛЕДОВАНИЯ ПРОСТРАНСТВЕННОГО РАСПРЕДЕЛЕНИЯ ХАРАКТЕРИСТИК ВОСПРИИМЧИВОСТИ ФОТОЭЛЕКТРИЧЕСКИХ ПРЕОБРАЗОВАТЕЛЕЙ В СОСТАВЕ СОЛНЕЧНЫХ БАТАРЕЙ К ОПТИЧЕСКОМУ ИЗЛУЧЕНИЮ | 2013 |

|

RU2565331C2 |

| СПОСОБ КОРРЕКЦИИ ТОПОЛОГИИ БИС | 2014 |

|

RU2560967C1 |

| СПОСОБ УВЕЛИЧЕНИЯ ВЫХОДА ГОДНЫХ ПРИ ИЗГОТОВЛЕНИИ ВЫСОКОПЛОТНЫХ ЭЛЕКТРОННЫХ МОДУЛЕЙ | 2012 |

|

RU2511007C2 |

Использование: способ включает следующие операции: изготовление активных элементов интегральной схемы; нанесение на них слоя контрольной металлизации; определение исправных элементов, удаление контрольной металлизации; соединение межсоединений исправных элементов методом бесшаблонной литографии. 3 ил.

СПОСОБ ИЗГОТОВЛЕНИЯ ИНТЕГРАЛЬНЫХ СХЕМ, включающий изготовление активных элементов, подачу на элементы управляющих сигналов, определение исправных элементов и создание межсоединений между ними, отличающийся тем, что, с целью повышения выхода годных, перед определением исправности элементов формируют на интегральной схеме контрольную металлизацию, по которой проводят определение исправности элементов методом потенциального контраста при сканировании электронным зондом, фиксируют координаты дефектных элементов, а межсоединения создают методом бесшаблонной литографии.

Авторы

Даты

1994-01-30—Публикация

1991-03-18—Подача