Область техники

Изобретение относится к электронике, а точнее к микроэлектронике.

Что такое выход годных в данном случае?

Выход годных - характеристика «качества технологического процесса, показывающая долю годных (недефектных) изделий в изготовленной партии (либо по групповой заготовке).

Выход годных, как правило, определяют как отношение количества годных изделий к общему объему партии (количеству изделий на групповой заготовке) и выражают в процентах. Обычно при этом учитываются т.н. годные изделия с первого прохода, т.е. не подвергавшиеся ремонту и восстановлению, однако в некоторых случаях выход годных с первого прохода выделяют как отдельную характеристику» (http:/www.elinform.ru/dictionary_262.htm).

Фактически увеличение выхода годных означает снижение стоимости электронных модулей.

Техническим результатом изобретения является расширение арсенала способов снижения стоимости изготовления высокоплотных электронных модулей.

Уровень техники

Обратимся к аналогам.

Один из путей снижения стоимости изготовления электронных модулей предложен в российском патенте 2133522 «Способ изготовления и контроля электронных компонентов».

«Способ изготовления и контроля электронных компонентов заключается в том, что множество кристаллов располагают в пресс-форме, ориентируясь на контактные площадки кристаллов и базовые элементы пресс-формы, изолируют все незащищенные поверхности кристаллов, кроме контактных площадок. Специфика способа заключается в том, что при расположении в пресс-форме кристаллы фиксируют между собой с образованием группового носителя, обеспечивая расположение лицевых поверхностей кристаллов в единой плоскости с одной из поверхностей группового носителя, при этом на эту плоскость наносят одновременно все проводники, необходимые для электротермотренировки и контроля, а также внешний разъем носителя. Одновременно с кристаллами в пресс-форму помещают групповую металлическую рамку, рамку фиксируют одновременно с кристаллами. Групповой носитель может быть также образован гибкой печатной платой, соединенной с жестким основанием. Техническим результатом изобретения является удешевление процессов электротермотренировки и финишного контроля, сокращение длительности технологического процесса сборки и контроля электронного компонента».

Другой путь - увеличение выхода годных за счет высокой надежности межсоединений (российский патент 2193259).

Также предлагается проектирование тестопригодности схем при их разработке.

«Проектирование тестопригодности схем при их разработке (Design-For-Testability, DFT) является ключевой и интегральной составляющей современного проектирования электронных схем и печатных плат. Ожидаемый уровень тестопригодности (в процентах покрытия тех или иных, заранее планируемых к тестированию, дефектов) обычно закладывается в технические требования новых разработок и подтверждается компьютерным моделированием тестопригодности еще до того, как начинается изготовление и монтаж печатных плат, узлов и систем. Правила тестопригодного проектирования <…> предполагают видоизменение топологии и/или связей между элементами схемы или даже добавление дополнительных элементов (внутрисхемных или наружных), которые могут никак не быть связаны с функционированием схемы и предназначены только лишь для обеспечения ее тестируемости» (http://www.jtag-test.ru/Solutions/DFT.php).

Этот способ и выбран за прототип.

Раскрытие изобретения

Выход годных при изготовлении электронных модулей является важнейшей характеристикой производства. При изготовлении высокоплотных, функционально и физически насыщенных электронных модулей (ВПЭМ) их работоспособность зависит от большого количества причин. Наиболее существенное влияние на увеличение выхода годных оказывает работоспособность пассивных элементов после их формирования и активных элементов после их монтажа. Традиционно применяют входной контроль работоспособности активных элементов в ограниченных условиях функционирования, промежуточный технологический контроль пассивных элементов и выходной контроль функционирования готового модуля вместе с испытаниями в рабочем диапазоне температур и других заданных условий. В результате на этапе выходного контроля лишь фиксируется неработоспособность ВПЭМ, обусловленная невозможностью предшествующего полноценного контроля элементов в диапазоне рабочих температур и других условий. Отсутствует возможность заранее, на начальных стадиях изготовления ВПЭМ, существенно повлиять на выход годных, обусловленный указанной проблемой.

Для решения проблемы предлагается изменить состав и последовательность операций изготовления ВПЭМ таким образом, чтобы работоспособность активных и пассивных элементов в рабочем диапазоне условий могла быть проконтролирована на начальной стадии изготовления. Тогда проведение остальных менее критичных операций изготовления ВПЭМ несущественно повлияет на выход годных. В результате выход годных ВПЭМ в основном будет определяться контролем на начальной стадии изготовления.

Для достижения цели предлагается в технологическом маршруте после формирования пассивных элементов и прямого монтажа активных элементов провести их герметизацию изоляционным компаундом, позволяющим защитить их от внешнего воздействия в диапазоне рабочих условий. Затем сформировать известными способами (фотолитографией, лазерной обработкой, металлизацией, планаризацией и др.) контактные выводы и перед последующим послойным формированием межсоединений проводить известными способами полнофункциональный зондовый контроль работоспособности каждого элемента в рабочем диапазоне температур и других внешних условий.

Чтобы это было возможным, проводят последовательно следующие технологические операции, иллюстрируемые фиг.1-7:

1. Несущественные операции.

2. Подготовка поверхности подложки.

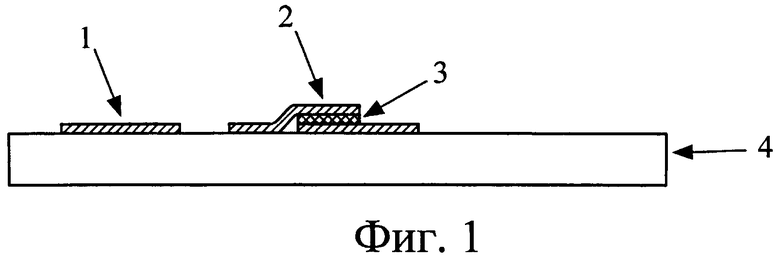

3. Формирование встроеннных тонкопленочных элементов R, С, L, микрополосковых элементов и др. На фиг.1 в качестве примера показано сопротивление 1 и конденсатор 2 с диэлектриком 3 на подложке 4.

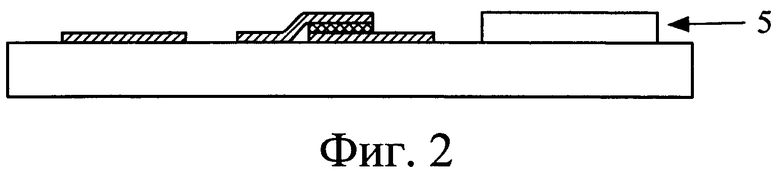

4. Выполнение прямого монтажа кристаллов интегральных схем (чипов) различных типов (СВЧ монолитные интегральные схемы, СБИС, микроэлектромеханические системы, системы на кристалле, силовые сборки, единичные полупроводниковые элементы, фотоприемники, пассивные элементы в «чип»-исполнении и др.). На фиг.2 к изображенному на фиг.1 добавлен чип 5.

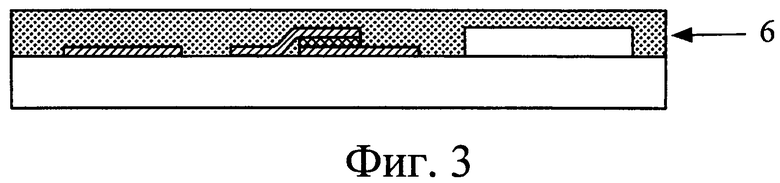

5. Заливка сформированного на подложке набора элементов слоем изоляционного полимера выше уровня самого высокого элемента на величину технологического запаса, например известного фотополимера SU-8 на 5-50 мкм выше уровня поверхности кристаллов (полимер 6 на фиг.3).

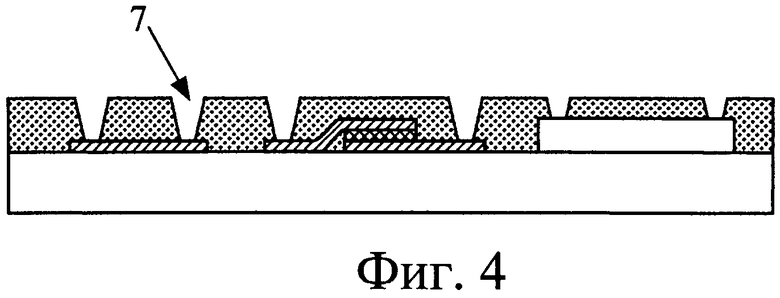

6. Вскрытие областей контактов к залитым элементам, например, методом фотолитографии (область контакта 7 на фиг.4).

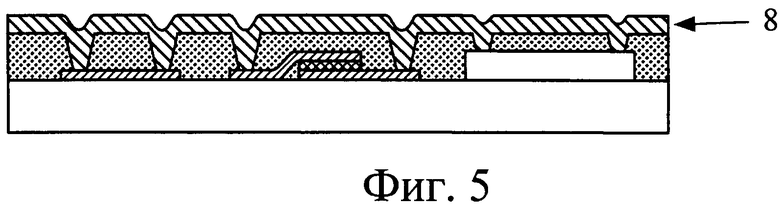

7. Заполнение металлизацией вскрытых окон в полимерном слое, например, вакуумным напылением и гальваническим доращиванием слоя меди на всю глубину вскрытых окон (металлизация 8 на фиг.5).

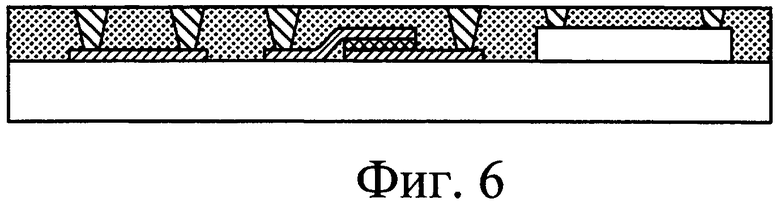

8. Планаризация (например, плоское шлифование и химико-механическое полирование) поверхности сформированного слоя до полного разделения всех контактов (фиг.6).

9. Очистка поверхности контактов для обеспечения их минимального омического сопротивления и электрических зондов на последующих операциях (фиг.6).

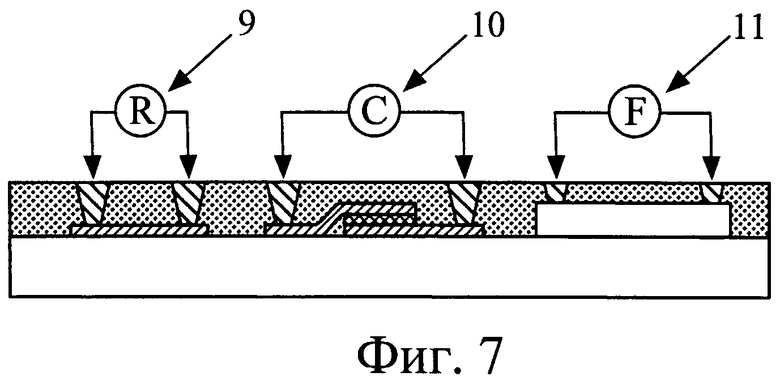

10. Выполнение полнофункционального контроля всех элементов путем помещения подложки на специализированный термозадающий держатель, последовательного присоединения измерительных зондов к контактам элементов и проведения комплекса требуемых измерений (на фиг.7 показаны измеритель сопротивления 9, измеритель емкости 10 и функциональный тестер 11).

11. Направление технологических модулей, успешно прошедших контроль, на последующие технологические операции и снятие с маршрута не прошедших контроль.

12. Несущественные операции.

Краткое описание чертежей

Фиг.1 иллюстрирует формирование встроенных тонкопленочных элементов.

Фиг.2 иллюстрирует выполнение прямого монтажа кристаллов интегральных схем (чипов) различных типов.

Фиг.3 иллюстрирует заливку сформированного на подложке набора элементов слоем изоляционного полимера.

Фиг.4 иллюстрирует вскрытие областей контактов к залитым элементам.

Фиг.5 иллюстрирует заполнение металлизацией вскрытых окон в полимерном слое.

Фиг.6 иллюстрирует планаризацию поверхности сформированного слоя до полного разделения всех контактов и очистку поверхности контактов.

Фиг.7 иллюстрирует выполнение полнофункционального контроля всех элементов.

Осуществление изобретения

На предприятии в течение 2 лет проводят зондовый контроль тестовых образцов в соответствии с описываемым способом на установке Sammit 12000 фирмы Agilent Technologies (USA). Это позволило повысить количество годных изделий после формирования многослойной коммутационной разводки в среднем на 27% за счет своевременной отбраковки полуфабрикатов на начальном этапе изготовления.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ИЗГОТОВЛЕНИЯ ТРЕХМЕРНОГО ПОЛИМЕРНОГО ЭЛЕКТРОННОГО МОДУЛЯ | 2001 |

|

RU2193259C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МНОГОКОМПОНЕНТНОГО ТРЕХМЕРНОГО ЭЛЕКТРОННОГО МОДУЛЯ | 2001 |

|

RU2193260C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ТРЕХМЕРНОГО ЭЛЕКТРОННОГО ПРИБОРА | 2012 |

|

RU2498453C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ПОЛИМЕРНОГО ЭЛЕКТРОННОГО МОДУЛЯ | 2006 |

|

RU2314598C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ГИБРИДНОГО ЭЛЕКТРОННОГО МОДУЛЯ | 2002 |

|

RU2222074C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ МНОГОУРОВНЕВОЙ МЕТАЛЛИЗАЦИИ ИНТЕГРАЛЬНЫХ МИКРОСХЕМ С ПОРИСТЫМ ДИЭЛЕКТРИЧЕСКИМ СЛОЕМ В ЗАЗОРАХ МЕЖДУ ПРОВОДНИКАМИ | 2011 |

|

RU2459313C1 |

| СПОСОБ ФОРМИРОВАНИЯ КАНАЛА ДЛЯ ПЕРЕДАЧИ ОПТИЧЕСКОГО СИГНАЛА МЕЖДУ КОМПОНЕНТАМИ ЭЛЕКТРОННОГО МОДУЛЯ | 2013 |

|

RU2561202C2 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ТРЕХМЕРНОГО ЭЛЕКТРОННОГО МОДУЛЯ | 2002 |

|

RU2221312C1 |

| СПОСОБ ПОЛУЧЕНИЯ МЕЖСОЕДИНЕНИЙ В ВЫСОКОПЛОТНЫХ ЭЛЕКТРОННЫХ МОДУЛЯХ | 2012 |

|

RU2504046C1 |

| СПОСОБ ФОРМИРОВАНИЯ ШАРИКОВЫХ ВЫВОДОВ НА АЛЮМИНИЕВОЙ МЕТАЛЛИЗАЦИИ КОНТАКТНЫХ ПЛОЩАДОК КРИСТАЛЛА | 2017 |

|

RU2671383C1 |

Изобретение относится к микроэлектронике и может быть использовано для увеличения выхода годных при изготовлении высокоплотных электронных модулей. Сущность способа заключается в том, что при изготовлении высокоплотных электронных модулей на основе формирования встроенных пассивных элементов, прямого монтажа активных элементов (чипов) и послойного формирования межсоединений до изготовления и монтажа электронных модулей разрабатывают видоизменение схемы, которое предназначено только для ее тестируемости, а за счет технологических операций после формирования пассивных и монтажа активных элементов и перед формированием межсоединений проводят многофункциональный зондовый контроль работоспособности каждого элемента. Технический результат: расширение арсенала способов снижения стоимости изготовления высокоплотных электронных модулей, увеличение выхода годных. 7 ил.

Способ увеличения выхода годных при изготовлении высокоплотных электронных модулей на основе формирования встроенных пассивных элементов, прямого монтажа активных элементов (чипов) и послойного формирования межсоединений, заключающийся в том, что еще до изготовления и монтажа электронных модулей разрабатывают видоизменение схемы, которое предназначено только для ее тестируемости, отличающийся тем, что позволяет за счет технологических операций после формирования пассивных и монтажа активных элементов и перед формированием межсоединений провести многофункциональный зондовый контроль работоспособности каждого элемента.

| "Анализ тестопригодности схем", URL:http://www.jtag-test.ru/Solutions/DFT.php | |||

| СПОСОБ ИЗГОТОВЛЕНИЯ МНОГОКОМПОНЕНТНОГО ТРЕХМЕРНОГО ЭЛЕКТРОННОГО МОДУЛЯ | 2001 |

|

RU2193260C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ И КОНТРОЛЯ ЭЛЕКТРОННЫХ КОМПОНЕНТОВ | 1997 |

|

RU2133522C1 |

| СПОСОБ ЗАЩИТЫ ПОЛУПРОВОДНИКОВЫХ ПРИБОРОВ ПЕРЕД ГЕРМЕТИЗАЦИЕЙ | 1990 |

|

RU2036538C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ТРЕХМЕРНОГО ПОЛИМЕРНОГО ЭЛЕКТРОННОГО МОДУЛЯ | 2001 |

|

RU2193259C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ТРЕХМЕРНОГО ЭЛЕКТРОННОГО МОДУЛЯ | 2002 |

|

RU2221312C1 |

| US 20090028491 A1, 29.01.2009 | |||

Авторы

Даты

2014-04-10—Публикация

2012-06-20—Подача