Изобретение относится к радиотехнике и может использоваться для повышения помехоустойчивости цифровых средств радиосвязи с псевдослучайной перестройкой рабочей частоты (ППРЧ).

Цель изобретения - повышение помехоустойчивости при воздействии сосредоточенных помех.

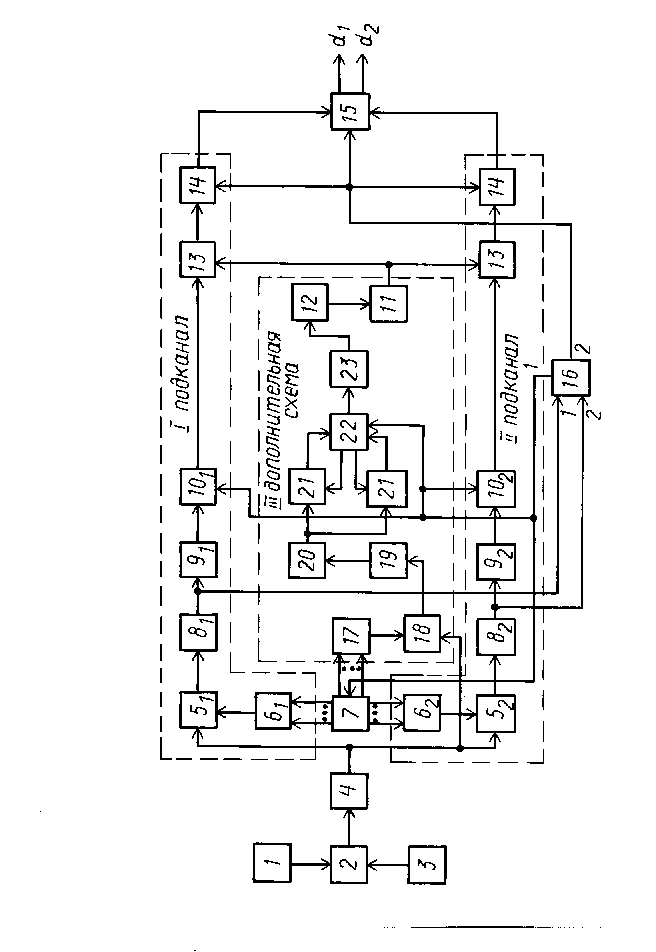

На чертеже изображена структурная электрическая схема предложенного приемного устройства.

Приемное устройство содержит антенну 1, смеситель 2 высокой частоты, высокочастотный генератор, широкополосной усилитель 4, первый, второй смесители 51 и 52 промежуточной частоты, первый, второй синтезаторы 61, 62 частот, генератор 7 псевдослучайного кода, первый, второй полосовые фильтры 81, 82, первый, второй квадратичные детекторы 91, 92, первый, второй интеграторы 101, 102, ограничитель 11, делитель 12 напряжения, первый, второй перемножители 131, 132, первый, второй сумматоры 141, 142, блок 15 сравнения, блок 16 поиска и синхронизации, третий синтезатор 17 частоты, третий смеситель 18 промежуточной частоты, третий полосовой фильтр 19, квадратор 20, третий, четвертый интеграторы 211, 212, блок 22 управления, формирователь 23 напряжения.

Устройство работает следующим образом.

Для формирования нелинейных весовых множителей вида μ кн= 1/(Pпк)3/2 в предлагаемом устройстве измерение мощности помехи осуществляется в свободных от элементов сигнала с внутрибитовой ППРЧ частотных каналах в периоды времени, предшествующие появлению на входе приемного устройства элементов сигналов на той или иной рабочей частоте. Предположим, что ожидается появление элемента сигнала по частоте fк в течение времени (K - 1)To ≅t ≅KTo, тогда измерение мощности помехи Рпк должно производиться на частоте fк, но в течение времени (К - 2)То ≅t ≅(К - 1)То.

Для выработки напряжения, пропорционального мощности помехи Рпк, имеется синтезатор 17, на который с выхода генератора 7 подаются команды о включении той частоты, которая будет иметь место в следующем скачке частоты в соответствии с известным действующим кодом. Предположим, что в течение времени (К - 2)То ≅t ≅(К - 1)То с выхода дополнительного синтезатора 17 на вход смесителя 18 поступило напряжение частотой

(fп + Δfпр) , где Δfпр - промежуточная частота.

На второй вход смесителя 18 в течение этого же отрезка времени поступает смесь сигнала и помехи на частоте fп и помехи на частоте fк. В результате на выходе полосового фильтра 19, настроенного на частоту Δfпр, действует напряжение помехи в виде квазигармонического колебания. Далее это напряжение подается на вход квадратора 20 и затем на входы двух параллельно включенных интеграторов 211, 212, работающих поочередно друг с другом. В то время, как один из интеграторов 21, например интегратор 211, в течение времени (К - 2)То≅t≅(К - 1)То находится в режиме накопления подаваемого на его вход напряжения, второй интегратор 212 находится в режиме запоминания проинтегрированного ранее напряжения в течение времени (К - 3)То≅t≅(К - 2)То. Полосовой фильтр 19, квадратор 20 и интеграторы 211, 212 составляют классическую схему измерения мощности помехи, на выходе которой формируется напряжение, пропорциональное мощности помехи Рпк на входе устройства. Поочередную и согласованную работу интеграторов 211, 212 осуществляет блок 22, вход которого для этой цели соединен с первым выходом блока 16. В момент подачи (t = КТо) на управляющий вход блока 22 с первого выхода блока 16 синхроимпульсов с периодом То, равным длительности работы на одной рабочей частоте, с одного из интеграторов 211 происходит сброс напряжения, пропорционального мощности помехи Рпк, на вход формирователя 23, обнуление этого интегратора и переход в режим интегрирования помехи для следующего элемента сигнала.

В этот же момент времени интегратор 212 переходит в режим запоминания на время То, накопленное ранее напряжения. Для момента времени (К - 1)То интегратор 211 перешел в режим запоминания накопленного напряжения, пропорционального Рпк, а второй интегратор 212 сбросил напряжение и приступил к интегрированию поступающего на его вход напряжения. Через период То в момент времени КТо интегратор 211 сбросит накопленное ранее напряжение, а интегратор 212 переходит в режим запоминания накопленного напряжения. В результате такой очередности работы интеграторов 211, 212 на входе формирователя 23 для каждого принимаемого элемента сигнала формируется напряжение, пропорциональное Рпк. Это напряжение с выхода блока 22 передается на вход формирователя 23. Формирователь 23 имеет нелинейность вида Uвыхнэ = ( Uвхнэ)3/2 и обеспечивает получение напряжения на его выходе, пропорционального Uвыхнэ = (Рпк)3/2. Далее это напряжение с выхода формирователя 23 подается на вход делителя 24 с характеристикой Uвыхд.н = 1/Uвхд.н. В результате на выходе делителя 12 формируется напряжение, соответствующее нелинейному весовому множителю.

Напряжение, пропорциональное μнк , через ограничитель подается на вторые входы умножителей 131, 132. В соответствии со значениями весовых множителей μнк в умножителях обеспечивается адаптивная регулировка напряжением каждого К-го элемента сигнала с внутрибитовой ППРЧ, поступающего на другие входы умножителей 13 с выходов интеграторов 101, 102.

Из описания принципа работы устройства следует, что чем меньше элементное отношение сигнал/помеха, тем с меньшим весовым множителем μнк это отношение будет участвовать в формировании результирующих отношений сигнал/помеха на выходе сумматоров 14. Ограничитель 25 с режимом мягкого ограничения обеспечивает работоспособность устройства при отсутствии помехи (или очень малом ее значении) в том или ином частотном канале. В этом случае при превышении весовым множителем μнк некоторого выбранного заранее, значения на входы умножителей 131, 132 с ограничителя подается постоянное напряжение, пропорциональное уровню порога ограничения. (56) IEEE Тrans. on Communications VOL, COM 34, N 7, 1986, p. 669-675.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ПРИЕМА СИГНАЛОВ С ПСЕВДОСЛУЧАЙНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 2002 |

|

RU2219656C2 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА СИГНАЛОВ С ПСЕВДОСЛУЧАЙНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 2002 |

|

RU2210861C1 |

| УСТРОЙСТВО ПОИСКА ПО ЗАДЕРЖКЕ СИГНАЛОВ С ПСЕВДОСЛУЧАЙНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 2001 |

|

RU2210187C2 |

| УСТРОЙСТВО ПОИСКА ПО ЗАДЕРЖКЕ СИГНАЛОВ С ПСЕВДОСЛУЧАЙНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 2001 |

|

RU2208295C2 |

| УСТРОЙСТВО ПОИСКА ПО ЗАДЕРЖКЕ СИГНАЛОВ СО СКАЧКООБРАЗНЫМ ИЗМЕНЕНИЕМ ЧАСТОТЫ | 2001 |

|

RU2207721C2 |

| ЛИНИЯ РАДИОСВЯЗИ | 2000 |

|

RU2173025C1 |

| ПРИЕМОПЕРЕДАЮЩЕЕ УСТРОЙСТВО | 2001 |

|

RU2205508C2 |

| УСТРОЙСТВО ПОИСКА ПО ЗАДЕРЖКЕ СИГНАЛОВ С ПСЕВДОСЛУЧАЙНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 2001 |

|

RU2194362C1 |

| АППАРАТУРА ПЕРЕДАЧИ ДИСКРЕТНОЙ И АНАЛОГОВОЙ ИНФОРМАЦИИ | 2001 |

|

RU2205509C2 |

| ЛИНИЯ РАДИОСВЯЗИ | 1999 |

|

RU2161865C2 |

Изобретение относится к радиотехнике и может быть использовано для повышения помехоустойчивости цифровых средств радиосвязи. Цель изобретения - повышение помехоустойчивости при воздействии сосредоточенных помех. Поставленная цель достигается за счет того, что в приемное устройство, содержащее высокочастотную часть, два симметричных и разнесенных по частоте подканала I и II, генератор псевдослучайного кода 7, блок сравнения 15, блок поиска и синхронизации 16, введены дополнительные блоки, обеспечивающие измерение мощности помех в периоды времени, свободные от присутствия элементов сигналов в данном частотном канале, и последующее формирование нелинейных весовых множителей, вход синтезатора частоты 17 соединен с вторым выходом генератора псевдослучайного кода 7, а выход подсоединен к одному из входов смесителя промежуточной частоты 18, второй вход которого подключен к выходу широкополосного фильтра 4, выход смесителя промежуточной частоты 18 через полосовой фильтр 19 подключен к входу квадратора 20, выход которого соединен с входами двух параллельно включенных интеграторов 21, 22, управляющие входы которых соединены с выходами блока управления 22, управляющий вход которой подключен к первому выходу блока поиска и синхронизации 16, выход каждого интегратора 21 через блок управления 22 соединен с входом формирователя 23, выход которого подключен к делителю выход которого через ограничитель соединен с умножителями. 1 ил.

ПРИЕМНОЕ УСТРОЙСТВО АДАПТИВНОГО РАЗЛИЧЕНИЯ ДИСКРЕТНЫХ СИГНАЛОВ, содержащее антенну, высокочастотный генератор, выходы которых соединены с входами смесителя высокой частоты, выход которого через широкополосный усилитель соединен с первыми входами первого и второго смесителей промежуточной частоты, вторые входы которых соединены соответственно с выходами первого и второго синтезаторов частоты, входы которых соединены с соответственно первыми и вторыми выходами генератора псевдослучайного кода, выход первого смесителя промежуточной частоты через последовательно соединенные первые полосовой фильтр, квадратичный детектор, интегратор, перемножитель и сумматор соединен с первым входом блока сравнения, выход второго смесителя промежуточной частоты через последовательно соединенные вторые полосовой фильтр, квадратичный детектор, интегратор, перемножитель и сумматор соединен с вторым входом блока сравнения, делитель напряжения, блок поиска и синхронизации, входы которого соединены с выходами первого и второго полосовых фильтров, первый выход блока поиска и синхронизации соединен с входом генератора псевдослучайного кода и вторыми входами интеграторов, а второй выход - с вторыми входами первого и второго сумматоров и третьим входом блока сравнения, выходы которого являются выходами приемного устройства, отличающееся тем, что, с целью повышения помехоустойчивости при воздействии сосредоточенных помех, введены последовательно соединенные третий синтезатор частот, третий смеситель промежуточной частоты, третий полосовой фильтр, квадратор, третий интегратор, блок управления и формирователь напряжения, а также четвертый интегратор и ограничитель, входы третьего синтезатора частоты соединены с третьими выходами генератора псевдослучайного кода, выход широкополосного фильтра соединен с вторым входом третьего смесителя промежуточной частоты, выход квадратора через четвертый интегратор соединен с вторым входом блока управления, третий вход которого соединен с первым выходом блока поиска и синхронизации, а выходы - с вторыми входами третьего и четвертого интеграторов, выход формирователя напряжения через последовательно соединенные делитель напряжения и ограничитель соединен с вторыми входами перемножителей.

Авторы

Даты

1994-01-30—Публикация

1990-12-19—Подача