Устройство относится к области радиотехники и может найти применение в системах связи с псевдослучайной перестройкой рабочей частоты.

Известны устройства поиска по задержке сигналов с псевдослучайной (скачкообразной) перестройкой рабочей частоты, описанные в монографии Диксона Р.К. "Широкополосные системы", М., "Связь", 1979г., стр.191-192, в монографии Борисова В. И. и др. "Помехозащищенность системы радиосвязи с расширением сигналов методом псевдослучайной перестройки рабочей частоты", М., "Радио и связь", 2000г., стр.219, недостатком которых является большая вероятность ложной синхронизации.

Наиболее близким по технической сущности к предлагаемому устройству является устройство поиска сложных сигналов по задержке, описанное в монографии Тузова Г.И. "Статистические теории приема сложных сигналов", М., "Сов. радио", 1977г., стр.326, рис.7.2б, представленный на фиг.1, где обозначено:

1 - смеситель (перемножитель);

2 - полосовой фильтр;

3 - амплитудный детектор;

4 - решающий блок;

5 - генератор тактовой частоты;

6 - перестраиваемый синтезатор частот (генератор кода).

Устройство-прототип содержит последовательно соединенные смеситель 1, первый, сигнальный вход которого является входом устройства, полосовой фильтр 2, амплитудный детектор 3, решающий блок 4, генератор тактовой частоты 5 и перестраиваемый синтезатор частот 6, выход которого соединен с вторым, опорным входом смесителя 1.

Устройство-прототип работает следующим образом.

В режиме поиска тактовую частоту блока 5 (fтч) устанавливают равной: fтч= fт±Δf; Δfт<<fт, при этом опорный сигнал с псевдослучайной перестройкой частоты, формируемый блоком 6, отстает или опережает по задержке входной сигнал.

В блоке 1 осуществляется перемножение входного и опорного сигналов. Результат перемножения на разностной (промежуточной) частоте фильтруется в блоке 2, детектируется блоком 3, выделенная огибающая напряжения сравнивается с порогом в блоке 4.

При превышении порога блок 4 формирует команду "1", подаваемую на блок 5, который при ее поступлении формирует тактовую частоту fт, равную тактовой частоте передатчика, используемую при формировании сигнала с псевдослучайной перестройкой рабочей частоты. При этом обеспечивается синхронность входного и опорного сигналов.

Недостатком прототипа является большая вероятность ложной синхронизации при воздействии узкополосных помех.

Для устранения указанного недостатка в устройство поиска по задержке сигналов с псевдослучайной перестройкой рабочей частоты, содержащее последовательно соединенные смеситель и полосовой фильтр, а также амплитудный детектор, первый решающий блок, генератор тактовой частоты и перестраиваемый синтезатор частот, выход которого соединен с вторым, опорным входом смесителя, введены последовательно соединенные второй коммутатор и ограничитель, последовательно соединенные второй ключ и второй решающий блок, а также первый ключ, накопитель, выход которого соединен с первыми, сигнальными входами первого и второго ключей, инвертор, делитель, элемент задержки, первый коммутатор и усилитель высокой частоты, вход которого является входом устройства, а выход соединен с первым, сигнальным входом смесителя. При этом выход первого решающего блока соединен с первым управляющим входом первого коммутатора, второй управляющий вход которого соединен с выходом второго решающего блока и с вторым, управляющим входом второго коммутатора, первый, сигнальный вход которого соединен с выходом полосового фильтра; второй, управляющий вход второго ключа соединен с выходом инвертора, вход которого соединен с вторым, управляющим входом первого ключа, с выходом делителя, с вторым сигнальным входом первого коммутатора и через элемент задержки - с первым сигнальным входом первого коммутатора, третий сигнальный вход которого соединен с входом делителя и с выходом генератора тактовой частоты, а выход первого коммутатора соединен с входом перестраиваемого синтезатора частот. Кроме того, выход ограничителя через амплитудный детектор соединен с входом накопителя, а второй выход второго коммутатора является выходом устройства.

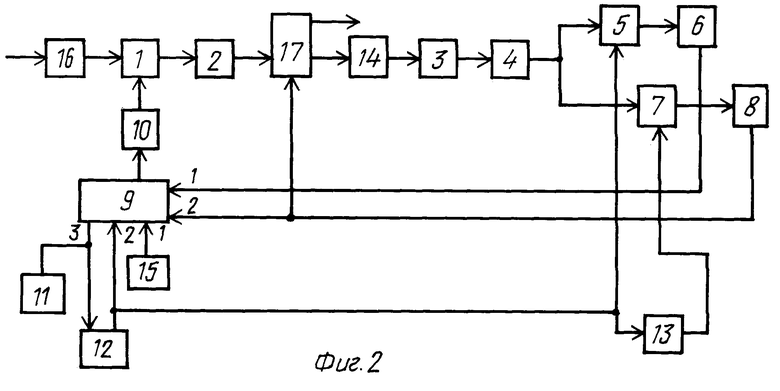

Структурная схема предлагаемого устройства приведена на фиг.2, где обозначено:

1 - смеситель;

2 - полосовой фильтр;

3 - амплитудный детектор;

4 - накопитель;

5 и 7 - первый и второй ключи;

6 и 8 - первый и второй решающие блоки;

9 и 17 - первый и второй коммутаторы;

10 - перестраиваемый синтезатор частот (генератор кода);

11 - генератор тактовой частоты;

12 - делитель;

13 - инвертор;

14 - ограничитель;

15 - элемент задержки;

16 - усилитель высокой частоты (УВЧ).

Заявляемое устройство содержит последовательно соединенные усилитель высокой частоты 16, вход которого является входом устройства, смеситель 1, полосовой фильтр 2, второй коммутатор 17, ограничитель 14, амплитудный детектор 3 и накопитель 4, выход которого соединен с первыми, сигнальными входами первого 5 и второго 7 ключей, при этом выход первого ключа 5 через первый решающий блок 6 соединен с первым, управляющим входом первого коммутатора 9, а выход второго ключа 7 через второй решающий блок 8 соединен с вторыми, управляющими входами первого 9 и второго 17 коммутаторов; второй, управляющий вход первого ключа 5 через инвертор 13 соединен с вторым, управляющим входом второго ключа 7, а также соединен с входом делителя 12, с вторым, сигнальным входом первого коммутатора 9 и через элемент задержки 15 соединен с первым, сигнальным входом первого коммутатора 9, третий, сигнальный вход которого соединен с первым выходом делителя 12 и с выходом генератора тактовой частоты 11, а выход первого коммутатора 9 через перестраиваемый синтезатор частот 10 соединен с вторым, опорным входом смесителя 1, второй выход второго коммутатора 17 является выходом устройства.

Предлагаемое устройство работает следующим образом.

Входная смесь, содержащая сигнал с псевдослучайной перестройкой рабочей частоты и узкополосные помехи, частоты которых попадают в полосу пропускания блока 16, поступает с входа устройства через блок 16 (где осуществляется его усиление и фильтрация) на первый, сигнальный вход блока 1.

В блоке 1 входная смесь перемножается с опорным сигналом, формируемым блоком 10.

Опорный сигнал, формируемый блоком 10, представляет собой сигнал с псевдослучайной перестройкой рабочей частоты, отличающийся от входного сигнала сдвигом всех частот программы перестройки на величину fпр, равную промежуточной частоте приемника. Результат перемножения входного и опорного сигналов с выхода блока 1 подается на блок 2, где он фильтруется. С выхода блока 2 напряжение через блок 17 подается на блок 14, где за счет его амплитудного ограничения оно нормируется по уровню. С выхода блока 14 напряжение подается на блок 3, где производится его амплитудное детектирование. Выделенные в блоке 3 видеоимпульсы полезного сигнала накапливаются в блоке 4. Накопленное в блоке 4 напряжение сравнивается с первым и вторым порогами в блоках 6 и 8 соответственно, куда оно поступает через блоки 5 и 7 соответственно.

Второй выход блока 17 является выходом устройства и его сигнал используется для дальнейшей обработки в приемнике (демодуляции, декодирование и т. д.).

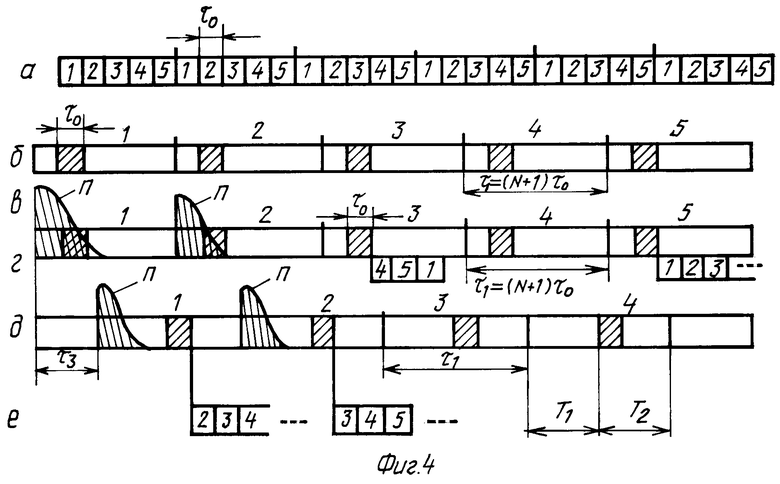

В исходном режиме работы при отсутствии синхронизации между входным и опорным сигналами тактовая частота на блок 10 подается от блока 12, где она формируется путем деления тактовой частоты fт, формируемой блоком 11, в (N+1) раз, где N - число частот во входном и опорном сигналах, при этом тактовая частота fт, формируемая блоком 11, равна тактовой частоте fт, используемой при формировании сигнала с псевдослучайной перестройкой рабочей частоты в передатчике.

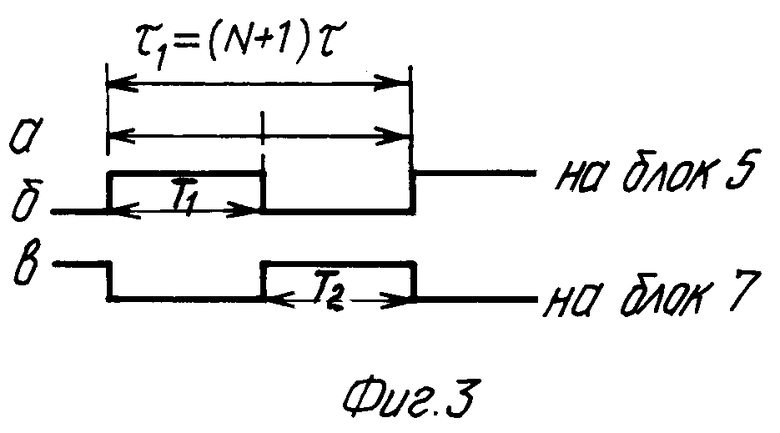

При тактовой частоте блока 12, равной fт/(N+1) длительность стояния на одной частоте блока 10 на каждой из частот программы перестройки τ1 в режиме сканирования по задержке определяется соотношением τ1 = (N+1)τ0, где τ0 = 1/fт. За время стояния блока 10 на каждой из частот программы перестройки в течение временного интервала τ1 передатчик успевает перестроиться по всем N частотам, и на временном интервале τ1 обязательно выделяется импульс полезного сигнала полной длительности τ0, временное положение которого на интервале τ1 определяется фазой (задержкой) входного сигнала относительно опорного.

Таким образом, временное положение импульса τ0 на интервале τ1 несет информацию о начальной фазе входного сигнала.

В момент скачка частоты (скачкообразной замены одной частоты на другую) в приемнике возникают коммутационные помехи, обусловленные переходными процессами в нем. Уровень коммутационных помех, носящий импульсный характер, возрастает при наличии в полосе пропускания блока 16 узкополосных помех, частоты которых не совпадают с той частотой, на которую перестраивается в данный момент приемник.

Этот эффект описан в монографии Винницкого А,С. "Модулированные фильтры и следящий прием ЧМ", М., "Сов. радио", 1969г., стр.248 (первый абзац снизу), где показано, что гармоническая помеха, воздействующая на перестраиваемый по частоте приемник, воспринимается им как спектр, то есть как импульсная помеха.

Механизм появления коммутационных помех может быть объяснен как значительное мгновенное расширение спектра опорного сигнала в момент скачка частоты, обеспечивающее кратковременное прохождение узкополосных помех на выход блока 1. Появление коммутационных помех на начальном участке интервала τ1 может привести к ложной синхронизации приемника.

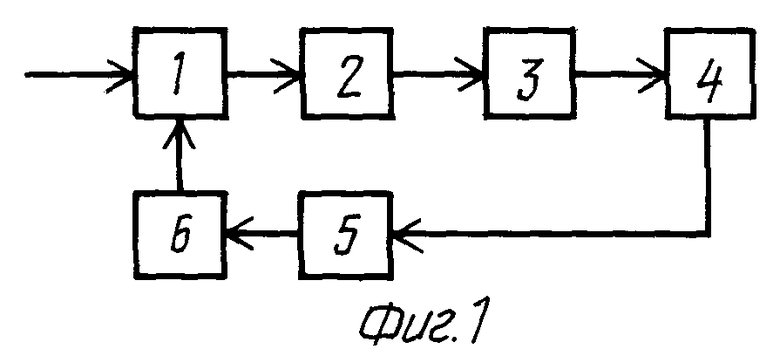

Для исключения ложной синхронизации по коммутационным помехам в устройстве используются два решающих блока (6 и 8), при этом блок 6 анализирует первую половину временного интервала τ1, равную T1 = τ1/2, а блок 8 - вторую его половину  Такой режим работы достигается за счет подачи тактовых импульсов блока 12 на второй, управляющий вход блока 5 непосредственно, а на второй, управляющий вход блока 7 - через блок 13, где они инвертируются. Сказанное поясняется фиг.3, где на фиг.3а показан временной интервал τ1, на фиг.3б - тактовые импульсы блока 12, на фиг.3в - инвертируемые тактовые импульсы блока 12 на выходе блока 13.

Такой режим работы достигается за счет подачи тактовых импульсов блока 12 на второй, управляющий вход блока 5 непосредственно, а на второй, управляющий вход блока 7 - через блок 13, где они инвертируются. Сказанное поясняется фиг.3, где на фиг.3а показан временной интервал τ1, на фиг.3б - тактовые импульсы блока 12, на фиг.3в - инвертируемые тактовые импульсы блока 12 на выходе блока 13.

Из фиг. 3 и фиг.2 видно, что в течение временного интервала Т1 команда "1" подается на второй управляющий блок 5, отпирая его. В это же время на второй, управляющий блок 7 подается команда "0" с выхода блока 13, запирая его. На временном интервале T2 на второй, управляющий блок 5 подается команда "0", запирая его, а на второй, управляющий блок 7 подается команда "1", отпирая его.

В тех случаях, когда на выходах блоков 6 и 8 формируются команды "0", соответствующие отсутствию в них превышения порога, тактовая частота равна fт/(N+1) выхода блока 12 через блок 9 подается на вход блока 10, обеспечивая его программную перестройку с длительностью стояния на каждой из частот программы перестройки τ1 = (N+1)τ0. Входная смесь через блок 16, где происходит ее усиление и фильтрация в полосе частот Δf, равной полосе частот, в которой осуществляется перестройка сигнала, подается на первый, сигнальный вход блока 1, на второй, опорный вход которого подается опорный сигнал с выхода блока 10.

Результат перемножения входного и опорного сигналов фильтруется на разностной (промежуточной) частоте fпр в блоке 2, нормируется по уровню в блоке 14 за счет его ограничения, детектируется в блоке 3, видеоимпульсы с выхода блока 3 подаются на блок 4, где производится их накопление. Накопленное напряжение через блок 5 подается на блок 6, а через блок 7 - на блок 8.

В блоках 6 и 8 происходит сравнение накопленного напряжения с порогом.

Появление коммутационных помех может привести к ложному превышению порога в блоке 6, анализирующем первый (от момента скачка частоты) временной интервал T1 = τ1/2. Для исключения ложной синхронизации по коммутационным помехам в случае превышения порога в блоке 6 в устройстве осуществляется сдвиг опорного сигнала блока 10 на время τ3 = τ1/2, что достигается за счет подачи тактовых импульсов блока 12 на блок 10 через блоки 15 и 9.

При задержке опорного сигнала на время τ3 = τ1/2, обеспечиваемого блоком 15, импульс полярного сигнала из временного интервала Т1 должен переместиться на временной интервал Т2, свободный от влияния коммутационных помех (фиг. 3д). Решение о синхронизации по полезному сигналу выносится только в том случае, если превышение порога фиксируется блоком 6 на втором временном интервале Т2. При этом блок 10 переходит на работу с тактовой частотой fт, формируемой блоком 11.

Указанные режимы работы реализуются следующим образом.

Команды о превышении (не превышении) порогов с выходов блоков 6 и 8 подаются соответственно на первый и второй управляющие входы блока 9, на первый, второй и третий сигнальные входы которого подаются тактовые импульсы от блоков 11, 12 и 15 соответственно.

Блок 9 работает следующим образом.

Если на выходах блоков 6 и 8 формируются команды "0", то блок 9 подключает к входу блока 10 вход блока 12. Устройство в этом случае находится в режиме сканирования по задержке. Если на выходе блока 8 формируется команда "0", а на выходе блока 6 команда "1", то блок 9 подключает к входу блока 10 выход блока 15, за счет чего осуществляется сдвиг опорного сигнала на время τ3.

Наличие команды "1" на выходе блока 8 при любом значении команды на выходе блока 6 обеспечивает подключение блоком 9 выхода блока 11 к входу блока 10, при этом устройство переходит в режим работы на тактовой частоте fт, синхронной с входным сигналом.

Момент перехода в режим работы на тактовой частоте fт определяется моментом превышения порога в блоке 8, при этом, если превышение порога в блоке 8 произошло после накопления N импульсов полезного сигнала в режиме поиска, когда τ1 = (N+1)τ0, то первый поступивший тактовый импульс с тактовой частотой fт переводит блок 10 на первую его частоту f1 с временем стояния на ней τ0. Если порог превышен после накопления (N-1)-го импульса полезного сигнала, то первый тактовый импульс тактовой частоты fт переведет блок 10 на N-ю частоту с временем стояния на ней τ0.

Одновременно команда "1", формируемая блоком 8, подается на второй, управляющий вход блока 17, который по этой команде отключает выход блока 2 от входа блока 14 и подключает выход блока 2 на выход устройства. При этом режим поиска задержки завершается.

Блок 17 является типовым коммутатором, при наличии на его управляющем входе команды "0" он подключает выход блока 2 к входу блока 14, а при появлении команды "1" на его втором, управляющем входе он подключает выход блока 2 к выходу устройства.

Работа заявляемого устройства поясняется фиг.4, где на фиг.4а показан входной сигнал с псевдослучайной перестройкой рабочей частоты, цифрами обозначены порядковые номера частот в программе перестройки входного сигнала, которая состоит из N=5 частот.

На фиг. 4б каждый опорный сигнал с псевдослучайной перестройкой рабочей частоты с длительностью стояния на каждой из частот, равной τ1 = (N+1)τ0. где τ0 - длительность излучения на каждой из частот во входном сигнале. Здесь же штриховкой (право) обозначены импульсы совпадения программ перестройки входного и опорного сигналов.

На фиг.4в показаны импульсы полезного сигнала на выходе блока 1, их временное положение на интервале τ1, а также коммутационные помехи, обозначенные штриховкой (влево) и буквой "П", поражающие начальный участок временного интервала τ1, следующий за моментом смены (скачка) частоты.

На фиг.4д показаны импульсы полезного сигнала и коммутационные помехи на выходе блока 1 при сдвиге опорного сигнала на величину τ3. На фиг.4д видно, что при сдвиге опорного сигнала на величину τ3 импульс полезного сигнала смещается в область, свободную от влияния коммутационных помех.

На фиг.4г, 4е видно, что временное положение импульса полезного сигнала на интервале τ1 определяет начальную фазу (задержку) входного сигнала относительно опорного.

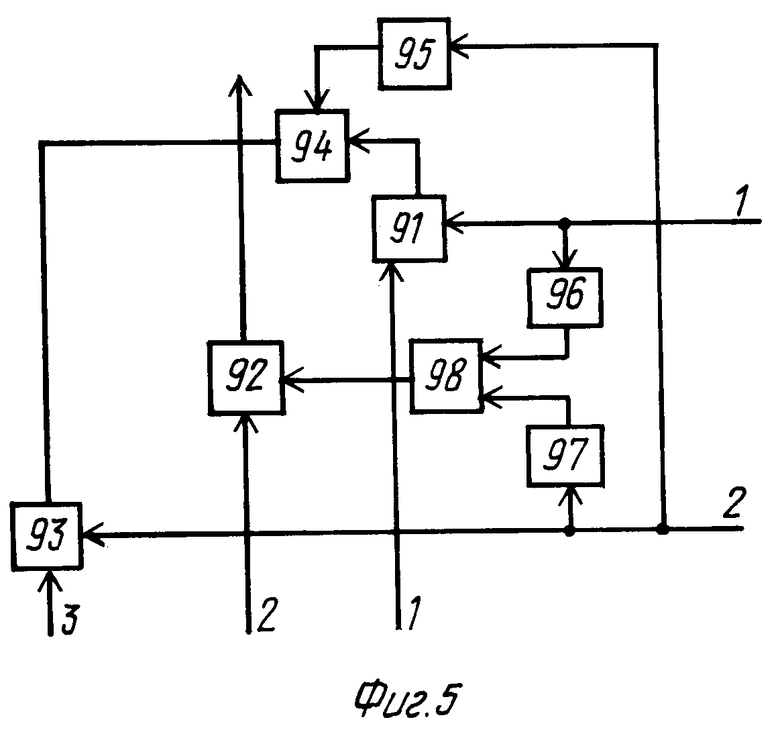

Структурная схема блока 9 приведена на фиг.5, где обозначено:

91, 92, 93 и 94 - первый, второй, третий и четвертый ключи;

95, 96 и 97 - первый, второй и третий инверторы;

98 - элемент "И".

Блок 9 содержит последовательно соединенные первый ключ 91 и четвертый ключ 94, второй ключ 92, третий ключ 93, при этом выходы блоков 92, 93 и 94 объединены и являются выходом блока 9; входы блоков 91, 92 и 93 являются соответственно первым, вторым и третьим сигнальными входами блока 9. Блок 9 содержит также элемент "И" 98, а также первый 95, второй 96 и третий 97 инверторы, при этом первый управляющий вход блока 9 соединен с управляющим входом блока 91 и с входом блока 96, второй управляющий вход блока 9 соединен с управляющим входом блока 93 и со входом блока 97; выходы блоков 96 и 97 соединены с первым и вторым входами блока 98 соответственно, выход которого соединен с управляющим входом блока 92.

Блок 9 работает следующим образом.

На первый управляющий вход блока 9 поступает команда о превышении (не превышении порога) с выхода блока 6, а на второй управляющий вход блока 9 поступает команда о превышении (не превышении) порога от блока 8. Эти команды инвертируются соответственно в блоках 96 и 97 и подаются соответственно на первый и второй входы блока 98, который формирует управляющее напряжение, подаваемое на блок 92.

Если на выходах блоков 6 и 8 формируются команды "1", то на выходах блоков 96 и 97 они инвертируются в команды "0", поэтому на выходе блока 98 формируется также команда "0", которая запирает ключ 92, запрещая прохождение на выход блока 9 тактовых импульсов блока 12. В то же время команда "1" от блока 8 подается на блок 93, отпирая его и обеспечивая прохождение на выход блока 9 тактовых импульсов блока 11. Одновременно команда "1" от блока 8 подается на блок 95, где, инвертируясь, превращается в команду "0", запирающую блок 94.

Таким образом, в этом режиме работы ключи 92 и 94 закрыты, а ключ 93 открыт, поэтому на выходе блока 9 подаемся тактовая частота fт от блока 11.

Если на выходах блоков 6 и 8 формируются команды "0", то запирается ключ 93, на выходе блока 98 формируемся команда "1", которая отпирает блок 92, обеспечивая прохождение на выход блока 9 тактовой частоты блока 12. Одновременно командой "0" блока 6 запирается блок 91.

Если на выходе блока 8 формируется команда "1", а на выходе блока 6 команда "0", то блок 93 отпирается, одновременно запираются блоки 92 и 94, при этом на выход блока 9 пропускается тактовая частота fт от блока 11.

Если на выходе блока 8 формируется команда "1", а на выходе блока 6 команда "0", то блок 93 отпирается, одновременно запираются блоки 92 и 94, при этом на выход блока 9 пропускается тактовая частота fт от блока 11.

Если на выходе блока 8 формируется команда "0", а на выходе блока 6 команда "1", то блоки 93 и 94 запираются, а блоки 91 и 94 отпираются, при этом на выход блока 9 проходит тактовая частота от блока 15.

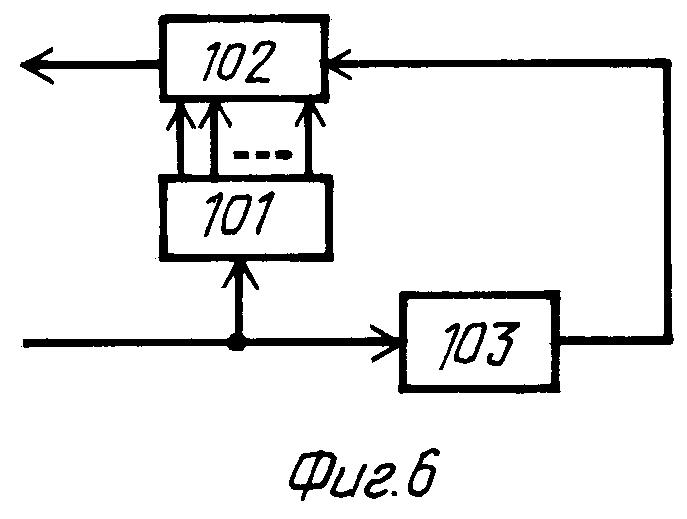

Структурная схема блока 10 приведена на фиг.6, где обозначено:

101 - генератор сетки частот;

102 - цифровой коммутатор;

103 - генератор числовой последовательности.

Блок 10 содержит последовательно соединенные генератор сетки частот 101 и цифровой коммутатор 102, выход которого является выходом блока 10, а также генератор числовой последовательности 103, вход которого, объединенный с входом блока 101, является входом блока 10, а выход блока 103 соединен с управляющим входом блока 102.

Блок 10 работает следующим образом.

Тактовые импульсы со входа блока 10 подаются одновременно на блоки 101 и l03. В блоке 101 с их использованием формируются N частот, каждая из которых подается на один из N входов блока 102.

В блоке 103 с использованием тактовых импульсов формируются N двоичных чисел, которые поступают последовательно во времени на (N+1)-й управляющий вход блока 102. Блок 102 ставит в соответствие каждому двоичному числу один из N сигналов сетки частот и только этот сигнал пропускает на свой выход.

Таким образом, на выходе блока 102 формируется последовательность из N частот, каждая из которых существует в течение длительности одного такта, после чего заменяется на другую частоту в соответствии с псевдослучайным законом, определяемым блоком 103.

Блок 4 может быть выполнен в виде согласованного фильтра, выполненного на линии задержки с задержкой между ее отводами, равной τ1 = (N+1)τ0, отводы линии задержки объединены в сумматоре, выход которого является выходом блока 4.

В устройстве-прототипе наличие узкополосных помех в полосе пропускания входного тракта приводит к появлению коммутационных помех, возникающих в момент смены одной частоты на другую. Наличие коммутационных помех приводит к резкому возрастанию вероятности ложной синхронизации.

В заявляемом устройстве обеспечивается обнаружение коммутационных помех по превышению первого порога на первом (относительно момента скачка частоты) временном интервале Т1, сдвиг программы перестройки опорного сигнала на время τ3 = τ1/2. За счет этого импульс полезного сигнала перемещается на второй (относительно момента скачка частоты) временной интервал T2, свободный от воздействия коммутационных помех. Решение о переходе в режим работы, синхронный с входным сигналом, принимается только в том случае, если фиксируется превышение второго порога на временном интервале T2, за счет чего исключается возможность ложной синхронизации по коммутационным помехам.

Устройство относится к радиотехнике и может найти применение в системах связи с псевдослучайной перестройкой рабочей частоты. За счет изменения способа сканирования по задержке и введения процедуры, позволяющей обнаружить коммутационные помехи, снижено их влияние при вынесении решения с синхронизации, снижена вероятность ложной синхронизации. Устройство содержит смеситель, полосовой фильтр, амплитудный детектор, накопитель, два ключа, два решающих блока, два коммутатора, перестраиваемый синтезатор частот, генератор тактовой частоты, делитель, инвертор, ограничитель, элемент задержки, усилитель высокой частоты. 6 ил.

Устройство поиска по задержке сигналов с псевдослучайной перестройкой рабочей частоты, содержащее последовательно соединенные смеситель и полосовой фильтр, а также амплитудный детектор, первый решающий блок, генератор тактовой частоты и перестраиваемый синтезатор частот, выход которого соединен с вторым опорным входом смесителя, отличающееся тем, что введены последовательно соединенные второй коммутатор и ограничитель, последовательно соединенные второй ключ и второй решающий блок, а также первый ключ, накопитель, выход которого соединен с первыми сигнальными входами первого и второго ключей, инвертор, делитель, элемент задержки, первый коммутатор и усилитель высокой частоты, вход которого является входом устройства, а выход соединен с первым сигнальным входом смесителя; при этом выход первого ключа через первый решающий блок соединен с первым управляющим входом первого коммутатора, второй управляющий вход которого соединен с выходом второго решающего блока, и с вторым управляющим входом второго коммутатора, первый сигнальный вход которого соединен с выходом полосового фильтра; второй управляющий вход второго ключа соединен с выходом инвертора, вход которого соединен с вторым управляющим входом первого ключа, с выходом делителя, с вторым сигнальным входом первого коммутатора и через элемент задержки - с первым сигнальным входом первого коммутатора, третий сигнальный вход которого соединен с входом делителя и с выходом генератора тактовой частоты, а выход первого коммутатора соединен с входом перестраиваемого синтезатора частот; кроме того, выход ограничителя через амплитудный детектор соединен с входом накопителя, а второй выход второго коммутатора является выходом устройства.

| ТУЗОВ Г.И | |||

| Статистическая теория приема сложных сигналов | |||

| - М.: Советское радио, 1977, с.326, рис | |||

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| УСТРОЙСТВО ПОИСКА ШИРОКОПОЛОСНЫХ СИГНАЛОВ ПО ЗАДЕРЖКЕ | 2000 |

|

RU2166230C1 |

| УСТРОЙСТВО ПОИСКА ШИРОКОПОЛОСНЫХ СИГНАЛОВ ПО ЗАДЕРЖКЕ | 1999 |

|

RU2165129C2 |

| US 4627080, 02.12.1986 | |||

| US 4726043, 16.02.1988. | |||

Авторы

Даты

2003-07-10—Публикация

2001-10-08—Подача