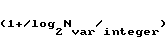

FIELD: computer engineering. SUBSTANCE: multiplier is built around single-layer converter of Nvar-bit code into (1+/log2Nvar/integer)-integer-bit code and  -integer-input multibit parallel adder with simultaneous-cascaded carry. Converter has multi-input single-bit adders of different types. Multibit carry is propagated between bits of both converter and parallel adder. EFFECT: improved speed. 8 dwg

-integer-input multibit parallel adder with simultaneous-cascaded carry. Converter has multi-input single-bit adders of different types. Multibit carry is propagated between bits of both converter and parallel adder. EFFECT: improved speed. 8 dwg

| Title | Year | Author | Number |

|---|---|---|---|

| MULTIPLE-INPUT PARALLEL ADDER | 0 |

|

SU1531090A1 |

| DATA CODING-DECODING DEVICE | 1994 |

|

RU2115231C1 |

| PROGRAMMING DIGITAL FILTER | 1992 |

|

RU2057364C1 |

| VARIABLE-MODULE ADDER | 2000 |

|

RU2183347C2 |

| SINGLE-CYCLE SHIFT REGISTER | 1990 |

|

RU2047922C1 |

| SESSION COMMUNICATION SYSTEM | 1992 |

|

RU2027312C1 |

| FREQUENCY DIVIDER WITH VARYING FRACTIONAL FACTOR | 1992 |

|

RU2041563C1 |

| PROGRAMMABLE DIGITAL FILTER | 1991 |

|

RU2006936C1 |

| METHOD FOR MESSAGE TRANSMISSION IN HALF-DUPLEX COMMUNICATION CHANNEL | 1996 |

|

RU2127953C1 |

| DRIVEN PULSE SHAPER | 1993 |

|

RU2047939C1 |

Authors

Dates

1994-04-30—Published

1988-12-06—Filed