Изобретение относится к вычислительной технике и может быть использовано в высокопроизводительных специализированных вычислительных машинах и устройствах обработки сигналов для решения систем линейных алгебраических уравнений.

Целью изобретения является повышение точности вычисления за счет выбора ведущего элемента по столбцам матрицы.

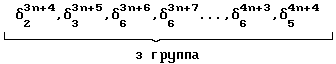

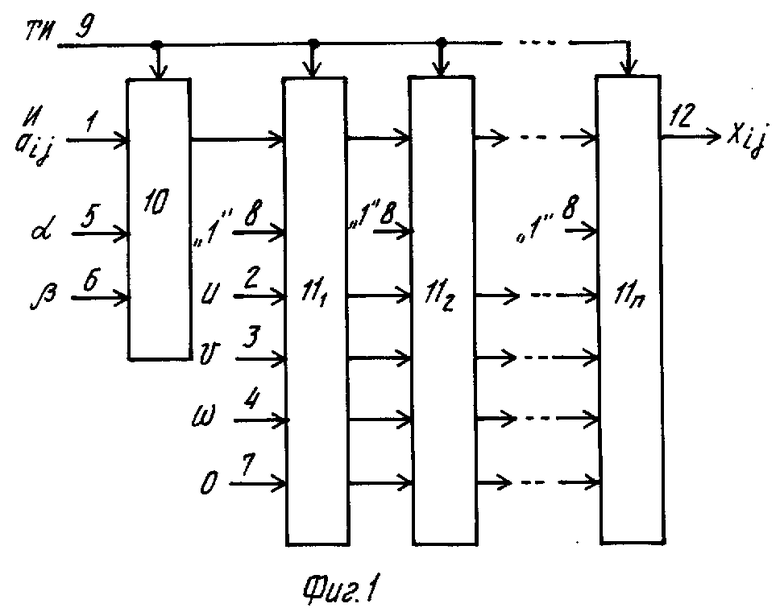

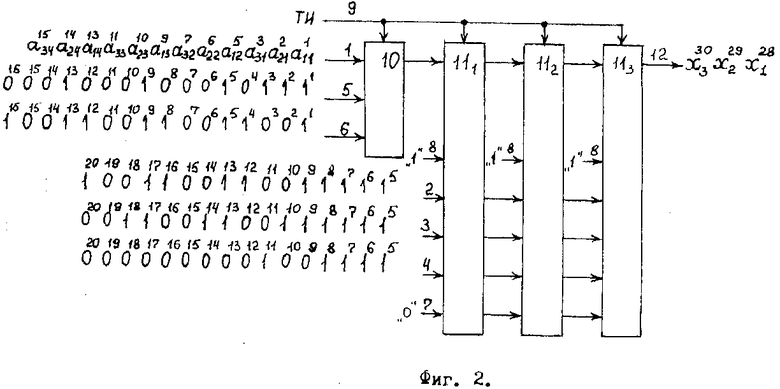

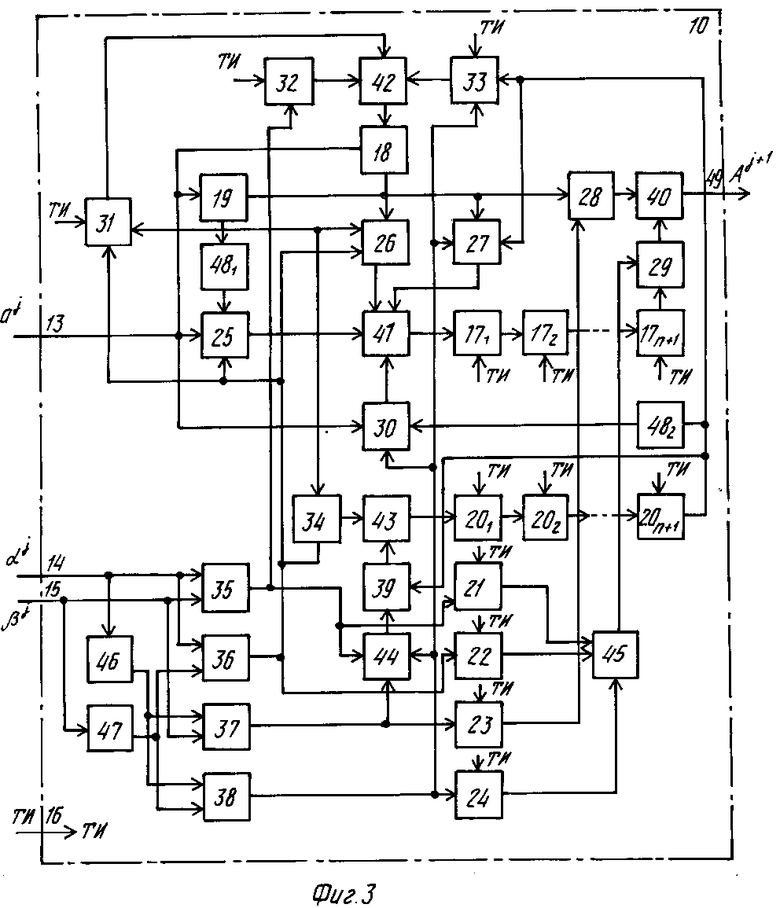

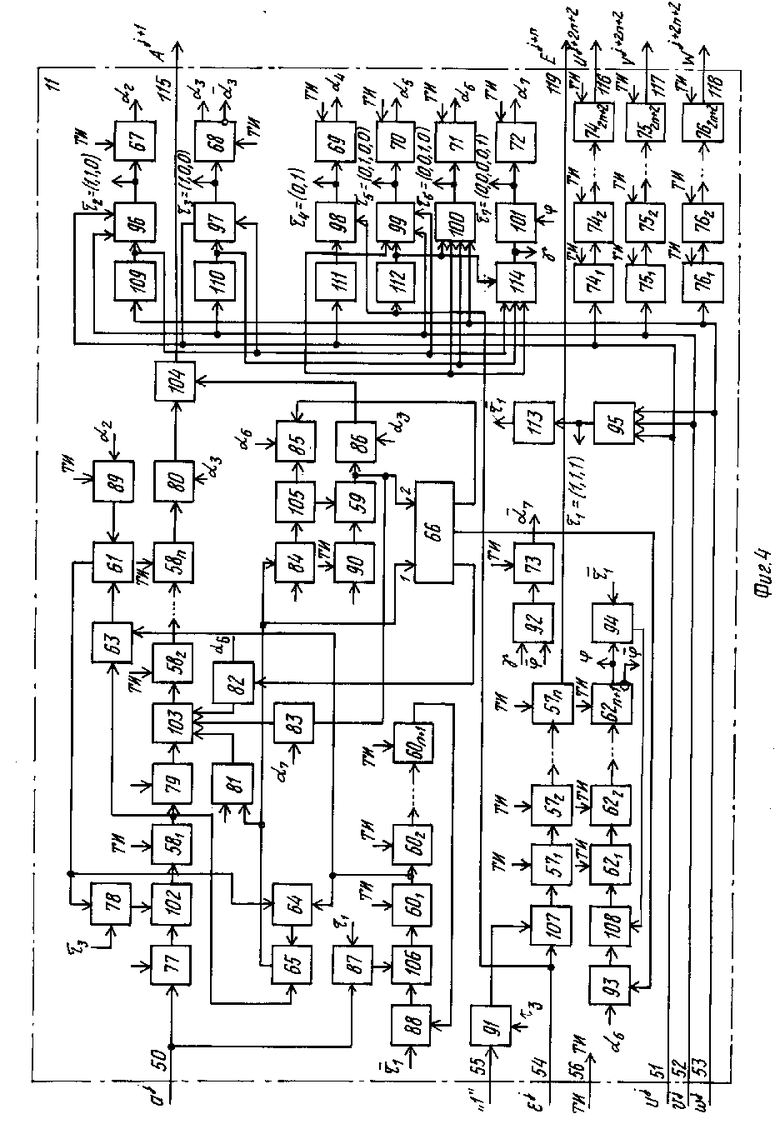

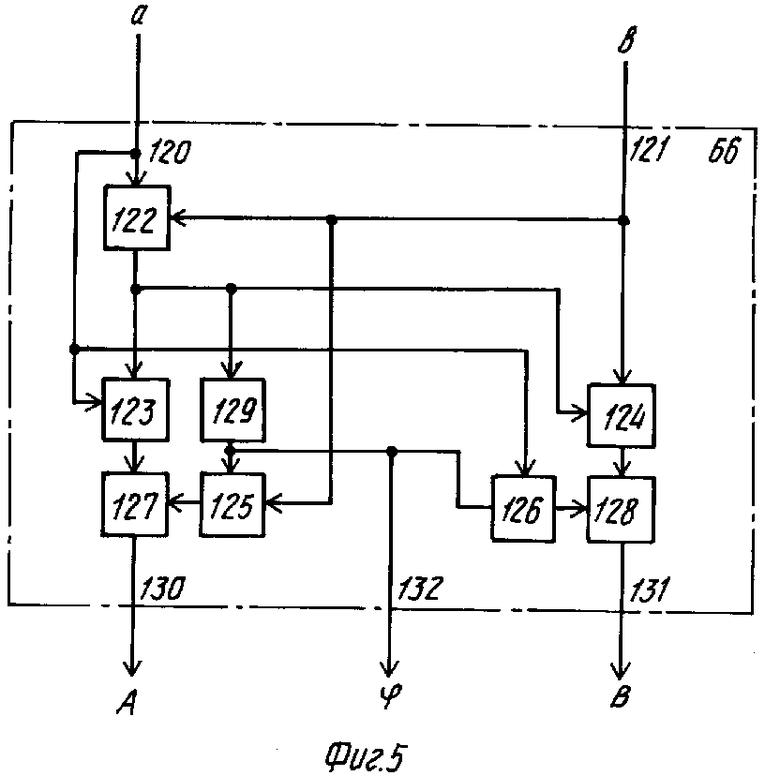

На фиг. 1 представлена структурная схема устройства; на фиг. 2 - структурная схема устройства для случая n= 3 и m= 1; на фиг. 3 - схема вычислительного модуля второго типа; на фиг. 4 - схема вычислительного модуля первого типа; на фиг 5 - схема коммутатора.

Устройство для решения систем линейных алгебраических уравнений (фиг. 1) содержит информационный вход 1, настроеные входы 2-8, синхровход 9, вычислительный модуль 10 второго типа, вычислительные модули 11i (i=  ) первого типа и выход 12.

) первого типа и выход 12.

Вычислительный модуль 10 второго типа (фиг. 3) содержит информационный вход 13, первый 14 и второй 15 настроечные входы, синхровход 16, первый узел 17 задержки, регистр 18, узел 19 сравнения, второй узел 20 задержки, триггеры 21-24, группы 25-30 элементов И, элементы И 31-39, группы 40 и 41 элементов ИЛИ, элементы ИЛИ 42-45, элементы НЕ 46, 47, 481 и 482 и выход 49.

Вычислительный модуль 11 первого типа (фиг. 4) содержит информационный вход 50, первый 51, второй 52, третий 53, четвертый 54 и пятый 55 настроечные входы, синхровход 56, четвертый 57 и первый 58 узлы задержки, регистр 59, второй узел 60 задержки, регистр 61, третий узел 62 задержки, делитель 63, умножитель 64, вычитатель 65, коммутатор 66, триггеры 67-73, пятый 74, шестой 75, седьмой 76 узел задержки, группы 77-88 элементов И, элементы И 89-101, группы 102-106 элементов ИЛИ, элементы ИЛИ 107 и 108, элементы НЕ 109-113, элемент 114, информационный выход 115, первый 116, второй 117, третий 118 и четвертый 119 настроечные выходы.

Коммутатор 66 (фиг. 5) содержит первый 120 и второй 121 входы, узел 122 сравнения, группы элементов И 123-126, группы элементов ИЛИ 127 и 128, элемент НЕ 129, первый 130, второй 131 и третий 132 выходы.

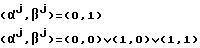

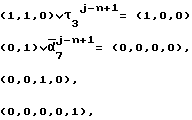

Вычислительный модуль 10 второго типа обладает возможностью реализации следующих функций:

Aj+1=

, где bj= aj-1, если ( αj-1, βj-1 )= (1, 1)V

, где bj= aj-1, если ( αj-1, βj-1 )= (1, 1)V

( αj-1, βj-1, γj-1 )= (1, 0, 1)V

( αj-1, βj-1, γj-n-2 )= (0, 0, 1),

γj=

,

,

где aj - значение на информационном входе на j-м такте вычислительного модуля;

где aj - значение на информационном входе на j-м такте вычислительного модуля;

αjиβj - значения соответственно на первом и втором настроечных входах на j-м такте вычислительного модуля;

Aj+1 - значение на выходе на (j+1)-м такте вычислительного модуля.

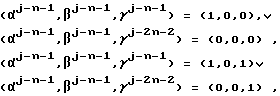

Вычислительный модуль первого типа обладаети возможностью реализации функций

Uj+2n+2= Uj ;

Vj+2n+2= Vj;

Wj+2n+2= ωj;

(

(

где Uj, Vj, ωj и εj - значение соответственно на первом, втором, третьем и четвертом настроечных входах на j-м такте вычислительного модуля, Uj, Vj, Wj и Ej - значения соответственно на первом, втором, третьем и четвертом настроечных выходах на j-м такте вычислительного модуля,

где Uj, Vj, ωj и εj - значение соответственно на первом, втором, третьем и четвертом настроечных входах на j-м такте вычислительного модуля, Uj, Vj, Wj и Ej - значения соответственно на первом, втором, третьем и четвертом настроечных выходах на j-м такте вычислительного модуля,

где fj= dj-1-bj-1 cj-1, если α5j-1= (0, 1, 0, 0)V

где fj= dj-1-bj-1 cj-1, если α5j-1= (0, 1, 0, 0)V

α6j-1 = (0, 0, 1, 0) V α7j-1 = (0, 0, 0, 0, 1),

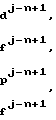

bj-1= dj-2/dj-n-4, если α2j-2= (1, 1, 0),

,

,  и

и

0

0

,

,

Pj = ,

,

где

где

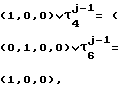

τ

τ

τ

τ

τ

τ

τ

Aj+1 - значение на информационном выходе на (j+1)-м такте вычислительного модуля.

Рассмотрим работу вычислительных модулей второго и первого типа.

Вычислительный модуль 10 второго типа работает в четырех режимах, которые задаются комбинацией управляющих сигналов αиβ , подаваемых соответственно на входы 14 и1 5.

В первом режиме ( α, β )= (1, 1), на выходе элемента И 35 формируется единичный сигнал, который открывает элемент И 32. При этом через элементы И 32 и ИЛИ 42 тактовый импульс подается на синхровод регистра 18, что обеспечивает запись в регистр 18 элемента а, подаваемого на вход 13. Узел 17 задержки содержит n+1 последовательно соединенных регистров. Информация из регистров 17i(i=  ) записывается в регистры 17i+1. Триггер 21 устанавливается в единичное состояние, единичный сигнал с выхода которого через элемент ИЛИ 45 открывает элементы И группы 29. Содержимое регистра 17n через элементы И группы 29 и ИЛИ группы 40 выдается на выход 49 вычислительного модуля 10. В триггерах 20j (j=

) записывается в регистры 17i+1. Триггер 21 устанавливается в единичное состояние, единичный сигнал с выхода которого через элемент ИЛИ 45 открывает элементы И группы 29. Содержимое регистра 17n через элементы И группы 29 и ИЛИ группы 40 выдается на выход 49 вычислительного модуля 10. В триггерах 20j (j=  ) происходит циклическая перезапись информации (элемент И 39 открыт).

) происходит циклическая перезапись информации (элемент И 39 открыт).

Во втором режиме ( α, β )= (1, 0), на выходе элемента И 36 формируетя единичный сигнал, который открывает элементы И 31, 34 и подается на входы элементов И группы 26. Входной элемент а, подаваемый на вход 13, сравнивается по модулю с содержимым регистра 18 в узле 19 сравнения. Если  < Рег. 18 >

< Рег. 18 > ≥

≥  a

a , то на выходе узла 19 сравнения формируется нулевой сигнал, который открывает элементы И группы 25.

, то на выходе узла 19 сравнения формируется нулевой сигнал, который открывает элементы И группы 25.

Входной элемент а через элементы И группы 25 и или группы 41 записывается в регистр 171. Содержимое регистров 17i (i=  ) записывается в регистры 17i+1. Кроме того, нулевой сигнал с выхода узла 19 сравнения через элементы И 34 и ИЛИ 43 записывается в триггер 201. Содержимое триггеров 20i (i=

) записывается в регистры 17i+1. Кроме того, нулевой сигнал с выхода узла 19 сравнения через элементы И 34 и ИЛИ 43 записывается в триггер 201. Содержимое триггеров 20i (i=  ) записывается в триггеры 20i+1.

) записывается в триггеры 20i+1.

Если  < Рег. 18 >

< Рег. 18 > <

<  a

a , то на выходе узла 19 сравнения формируется единичный сигнал, который подается на входы элементов И 31 и 34 и элементов И группы 26. Содержимое регистра 18 через элементы И группы 26 и ИЛИ группы 41 записывается в регистр 171. Входное данное а записывается в регистр 18 (тактовый импульс через элементы И 31 и ИЛИ 42 подается на синхровход регистра 18). Единичный сигнал с выхода узла 19 сравнения через элементы И 34 и ИЛИ 43 записывается в триггер 201. Триггер 22 устанавливается в единичное состояние, что обеспечивает выдачу содержимого регистра 17n+1 на выход 49.

, то на выходе узла 19 сравнения формируется единичный сигнал, который подается на входы элементов И 31 и 34 и элементов И группы 26. Содержимое регистра 18 через элементы И группы 26 и ИЛИ группы 41 записывается в регистр 171. Входное данное а записывается в регистр 18 (тактовый импульс через элементы И 31 и ИЛИ 42 подается на синхровход регистра 18). Единичный сигнал с выхода узла 19 сравнения через элементы И 34 и ИЛИ 43 записывается в триггер 201. Триггер 22 устанавливается в единичное состояние, что обеспечивает выдачу содержимого регистра 17n+1 на выход 49.

В третьем режиме ( α, β )= (0, 0). На выходе элемента И 38 формируется единичный сигнал, который подается на вход элемента И 33 и на входы элементов И групп 27 и 30. Если триггер 20n+1 находится в единичном состоянии, то элемент И 33 открывается и разрешается запись входного данного а в регистр 18. Кроме того, открываются элементы И группы 27 и через элементы И группы 27 и ИЛИ группы 41 содержимое регистра 18 записывается в регистр 171. Информация из регистров 17i(i=  ) записывается в регистры 17i+1. Если триггер 20n+1 находится в нулевом состоянии, то на выходе элемента НЕ 482 формируется единичный сигнал, который открывает элементы И группы 30. Входное данное записывается в регистр 171 через элементы И групп 30 и ИЛИ группы 41. На выход 49 вычислительного модуля 10 выдается содержимое регистра 17n+1.

) записывается в регистры 17i+1. Если триггер 20n+1 находится в нулевом состоянии, то на выходе элемента НЕ 482 формируется единичный сигнал, который открывает элементы И группы 30. Входное данное записывается в регистр 171 через элементы И групп 30 и ИЛИ группы 41. На выход 49 вычислительного модуля 10 выдается содержимое регистра 17n+1.

В четвертом режиме ( α, β )= (0, 1). При этом на выходе элемента И 37 формируется единичный сигнал, который через элемент ИЛИ 44 открывает элемент И 39, что обеспечивает циклическую запись информации в триггерах 20i (i=  ). Информация из регистров 17i (i=

). Информация из регистров 17i (i=  ) записывается в регистры 17i+1. Триггер 23 устанавливается в единичное состояние и открываются элементы И группы 28. Содержимое регистра 18 выдается через элементы И группы 28 и ИЛИ группы 40 на выход 49 вычислительного модуля.

) записывается в регистры 17i+1. Триггер 23 устанавливается в единичное состояние и открываются элементы И группы 28. Содержимое регистра 18 выдается через элементы И группы 28 и ИЛИ группы 40 на выход 49 вычислительного модуля.

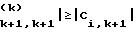

Вычислительный модуль 11 первого типа работает в семи режимах, которые задаются комбинацией внешних управляющих сигналов u, v, ω, ε и внутреннего управляющего сигнала ϕ , который формируется только в седьмом режиме работы в результате сравнения чисел по модулю на выходе 132 узла сравнения в коммутаторе 66 (фиг. 5). Соответствующие значения управляющих сигналов uj, vj, ωj, εj и ϕj на j-м такте определяют управляющие сигналы αij+1= τij= (uj, vj, ωj, εj, ϕj), (i= 1,7), где i - номер режима работы, которые подаются на соответствующие логические элементы вычислительного модуля 11. Причем управляющий сигнал τij обеспечивает запись данных в регистр или триггер на j-м такте, а управляющий сигнал αij+1 - на (j+1)-м такте. На вход 55 постоянно подается единичный сигнал.

Управляющие сигналы u, v, ω и ε подаются соответственно на входы 51, 52, 53 и 54 и выдаются соответственно на выходы 116, 117, 118 и 119. Причем сигналы u, v и ωзадерживаются на 2n+2 тактов соответственно триггерами 74i, 75i, 76i (i=  ) соответствующих узлов 74, 75 и 76 задержки, а сигнл εзадерживается на n тактов триггерами 57i (i=

) соответствующих узлов 74, 75 и 76 задержки, а сигнл εзадерживается на n тактов триггерами 57i (i=  ) узла 57 задержки.

) узла 57 задержки.

Первый режим работы вычислительного модуля 11 задается управляющими сигналами τ1j= (uj, vj, ωj)= (1, 1, 1) (значение управляющего сигнала ε на режим работы не влияет). На выходе элемента И 95 формируется единичный сигнал τ1, на выходе элемента НЕ 111 - нулевой сигнал  , которые подаются соответственно на входы элементов И групп 87, 88 и элемента И 94. При этом входной элемент aj, подаваемый на вход 50, записывается в регистр 601 узла 60 задержки на n+1 тактов через элементы И группы 87 и ИЛИ группы 106. Информация из регистров 60i (i=

, которые подаются соответственно на входы элементов И групп 87, 88 и элемента И 94. При этом входной элемент aj, подаваемый на вход 50, записывается в регистр 601 узла 60 задержки на n+1 тактов через элементы И группы 87 и ИЛИ группы 106. Информация из регистров 60i (i=  ) записывается в регистры 60i+1. Аналогисчно информация записывается и в триггеры 57i (i=

) записывается в регистры 60i+1. Аналогисчно информация записывается и в триггеры 57i (i=  ) и 61i (i=

) и 61i (i=  ).

).

Второй режим работы задается управляющими сигналами α ) записывается в регистры 58i+1. На выходе делителя 63 формируется значение aj/aj-1, которое на (j+1)-м такте записывается в регистр 61. Управляющий сигнал εj записывается в триггер 571. Информация в регистрах 60i (i=

) записывается в регистры 58i+1. На выходе делителя 63 формируется значение aj/aj-1, которое на (j+1)-м такте записывается в регистр 61. Управляющий сигнал εj записывается в триггер 571. Информация в регистрах 60i (i=  ) циклически переписывается. Аналогично записывается информация и в триггерах 57i (i=

) циклически переписывается. Аналогично записывается информация и в триггерах 57i (i=  ) и 62i (i=

) и 62i (i=  ).

).

Третий режим работы определяется управляющими сигналами τ3j= α3j+1= (uj, vj, ωj)= (1,0,0). Уп-равляющие сигналы τ3jи α3j+1 формируются соответственно на выходах элемента И 97 и триггера 68. Сигнал τ3jподается на входы элементов И групп 78, 79 и на вход элемента И 91. Сигнал α3j+1 подается на вход элементов И группы 86, а сигнал α3j+1 - на вход элементов И группы 80. При этом в регистр 581 записывается содержимое регистра 61 через элементы И 78 и ИЛИ группы 102. Содержимое регистра 59 через элементы И группы 86 и ИЛИ группы 104 выдается на (j+1)-м такте на выход 115. Единичный сигнал, подаваемый на вход 55, через элементы И 91 и ИЛИ 107 устанавливает триггер 571 в единичное состояние. Информация из триггера 57i (i=  ) записывается в триггер 57i+1. Аналогично информация циклически переписывается в регистрах 60i(i=

) записывается в триггер 57i+1. Аналогично информация циклически переписывается в регистрах 60i(i=  ) и триггерах 62i (i=

) и триггерах 62i (i=  ).

).

В четвертом режиме работы подаются управляющие сигналы τ4j= α4j+1= (uj, εj)= (0,1) (сигналы ujиωjна режим работы не влияют). На выходах элемента И 98 и триггера 69 формируются соответственно управляющие сигналы τ4jиα4j+1. Управляющий сигнал τ4j подается на входы элементов И группы 77, управляющий сигнал α4j+1 - на входы элементов И группы 81. При этом входной элемент aj записывается в регистр 581. На выходе умножителя 64 формируется произведение <Рег. 601>˙<Рег. 61>, которое подается на вход вычитателя 65. На второй вход последнего подается содержимое регистра 581 и на его выходе формируется значение <Рег. 581>-<Рег. 601>˙<<Рег. 61>, которое на (j+1)-м такте через элементы И группы 81 и ИЛИ группы 103 записывается в регистр 582. Информация из регистров 58i (i=  ) записывается в регистры 58i+1. Содержимое регистра 58n через элементы И группы 80 и ИЛИ группы 104 ( α3= 1) выдается на выход 115. Аналогично информация записывается в регистры 60i (i=

) записывается в регистры 58i+1. Содержимое регистра 58n через элементы И группы 80 и ИЛИ группы 104 ( α3= 1) выдается на выход 115. Аналогично информация записывается в регистры 60i (i=  ) и триггеры 57i (i=

) и триггеры 57i (i=  ) и 62i (i=

) и 62i (i=  ).

).

Пятый режим работы задается управляющими сигналами τ5j= α5j+!= (uj, vj, ωj, εj)= (0,1,0,0, ). На выходах элемента И 99 и триггера 70 формируется соответственно сигналы τ5j и α5j+1. Управляющий сигнал τ5j подается на входы элементов И группы 77 При этом в регистр 581записывается входной элемент aj, на выходе вычитателя 65 формируется значение <Рег. 581>-<Рег. 601>˙<Рег. 61>, которое на (j+1)-м такте по управляющему сигналу α5j+1 через элементы И группы 83 и ИЛИ группы 106 записывается в регистр 59 (элемент И 90 открыт и тактовый импульс подается на синхровход регистра 59). На выход 115 выдается содержимое регистра 58n (  = 1). Аналогично осуществляется запись информации в регистры 58i (i=

= 1). Аналогично осуществляется запись информации в регистры 58i (i=  ), 60i (i=

), 60i (i=  ) и триггеры 57i (i=

) и триггеры 57i (i=  ) и 62i(i=

) и 62i(i=  ).

).

В шестом режиме работы подаются управляющие сигналы τ6j= α6j+1= (uj, vj, ωj, εj)= (0, 0, 1, 0). На выходе элемента И 100 формируется сигнал τ6j, на выходе триггера 71 - сигнал α6j+1. Управляющий сигнал α5j+1 подается на входы элементов И группы 84 и на вход элемента И 90. Сигнал подается на входы элементов И группы 77. Сигнал τ6j подается на входы элементов И групп 82, 85 и на входы элементов И 90 и 93. При этом в регистр 581 записывается входной элемент aj, на выходе вычитателя 65 формируется значение A= <Рег. 581>-<Рег. 601>˙<Рег. 61> которое подается на первый вход коммутатора 66, на второй вход которого подается содержимое B регистра 59. Если  B

B  ≥

≥  A

A  , то на первом выходе коммутатора 66 выдается значение A, на втором выходе - значение B и на третьем выходе - сигнал ϕj= 0. На (j+1)-м такте по сигналу α6j+1 значение A записывается через элементы И группы 82 и ИЛИ группы 103 в регистр 582, значение B записывается через элементы И группы 85 и группы ИЛИ 105 в регистр 59 и сигнал ϕj = 0 - через элементы И 93 и ИЛИ 108 в триггер 621. Если

, то на первом выходе коммутатора 66 выдается значение A, на втором выходе - значение B и на третьем выходе - сигнал ϕj= 0. На (j+1)-м такте по сигналу α6j+1 значение A записывается через элементы И группы 82 и ИЛИ группы 103 в регистр 582, значение B записывается через элементы И группы 85 и группы ИЛИ 105 в регистр 59 и сигнал ϕj = 0 - через элементы И 93 и ИЛИ 108 в триггер 621. Если  B

B  <

<  A

A  , то на первом выходе коммутатора 66 выдается значение B, на втором выходе - значение A и на третьем выходе - сигнал ϕj= 1. На (j+1)-м такте по сигналу α6j+1значение B записывается в регистр 582, значение A - в регистр 59 и сигнал ϕ = 1 - в триггер 621. Содержимое 58n выдается на выход 115 (

, то на первом выходе коммутатора 66 выдается значение B, на втором выходе - значение A и на третьем выходе - сигнал ϕj= 1. На (j+1)-м такте по сигналу α6j+1значение B записывается в регистр 582, значение A - в регистр 59 и сигнал ϕ = 1 - в триггер 621. Содержимое 58n выдается на выход 115 (  = 1). Аналогично информация записывается в регистры 58i (i=

= 1). Аналогично информация записывается в регистры 58i (i=  ), 60i(i=

), 60i(i=  ) и триггеры 57i (i=

) и триггеры 57i (i=  ), 62i (i=

), 62i (i=  ).

).

Седьмой режим работы определяется управляющими сигналами τ7j= α7j+1= (uj, vj, ωj, εj, ϕj)= = (0,0,0,0,1). Сигнал τ7j формируется на выходе элемента И 101, сигнал α7j+1 - на выходе триггера 72, сигнал α7j+1- на выходе триггера 73. Сигнал τ7j подается на входы элементов И группы 77, сигнал α7j+1 - на входы элементов И групп 83 и 84 и на вход элемента И 90, сигнал α7j+1- на входы элементов И группы 81. При этом в регистр 581 записывается элемент ai, на выходе вычитателя 65 формируется значение A= <Рег. 581>-<Рег. 601>˙<Рег. 61> содержимое регистров 58i (i=  ) записывается в регистры 58i+1, содержимое регистра 58n выдается на выход 115 (

) записывается в регистры 58i+1, содержимое регистра 58n выдается на выход 115 (  = 1). Если триггер 61n+1 в нулевом состоянии ( ϕ

= 1). Если триггер 61n+1 в нулевом состоянии ( ϕ  0), то

0), то  = 1 и значение A записывается в регистр 582 на (j+1)-м такте через элементы И группы 81 и ИЛИ группы 103. Если триггер 61n+1 в единичном состоянии, то α7j+1= 1, значение A записывается в регистры 59 на (j+1)-м такте через элементы И группы 84 и ИЛИ группы 105, содержимое B регистра 59 через элементы И группы 83 и ИЛИ группы 103 записывается в регистр 582.

= 1 и значение A записывается в регистр 582 на (j+1)-м такте через элементы И группы 81 и ИЛИ группы 103. Если триггер 61n+1 в единичном состоянии, то α7j+1= 1, значение A записывается в регистры 59 на (j+1)-м такте через элементы И группы 84 и ИЛИ группы 105, содержимое B регистра 59 через элементы И группы 83 и ИЛИ группы 103 записывается в регистр 582.

Коммутатор 66 (фиг. 5) работает следующим образом. На входы 119 и 120 подаются соответственно значения A и B. Если  B

B  ≥

≥  A

A  , то на выходе узла 122 сравнения формируется единичный сигнал, на выходе элемента НЕ 129 - нулевой сигнал ( ϕ= 0), элементы И групп 125 и 126 закрыты, а групп 123 и 124 открыты, значение A через элементы И группы 123 и ИЛИ группы 127 подается на выход 130, а значение B через элементы И группы 124 и ИЛИ группы 128 - на выход 131. Если

, то на выходе узла 122 сравнения формируется единичный сигнал, на выходе элемента НЕ 129 - нулевой сигнал ( ϕ= 0), элементы И групп 125 и 126 закрыты, а групп 123 и 124 открыты, значение A через элементы И группы 123 и ИЛИ группы 127 подается на выход 130, а значение B через элементы И группы 124 и ИЛИ группы 128 - на выход 131. Если  B

B  <

<  A

A  , то на выходе узла 122 сравнения формируется нулевой сигнал, элементы И групп 123 и 124 закрыты, а элементы И групп 126 и ИЛИ группы 128 подается на выход 131, а значение B через элементы И группы 125 и ИЛИ группы 127 на выход 130 и ϕ = 1.

, то на выходе узла 122 сравнения формируется нулевой сигнал, элементы И групп 123 и 124 закрыты, а элементы И групп 126 и ИЛИ группы 128 подается на выход 131, а значение B через элементы И группы 125 и ИЛИ группы 127 на выход 130 и ϕ = 1.

В основу работы устройства для решения систем линейных алгебраических уравнений вида A1 ˙X= A2, где A1= (aij), i, j=  , A2= (aij), i=

, A2= (aij), i=  , j=

, j=  , X= (xij), i=

, X= (xij), i=  , j=

, j=  , положен метод Гаусса-Жордана с частичным выбором ведущего элемента по столбцам матрицы в виде следующих рекуррентных соотношений:

, положен метод Гаусса-Жордана с частичным выбором ведущего элемента по столбцам матрицы в виде следующих рекуррентных соотношений:

b1j= a1j, j=  , ,

, ,

i=  :

:

если  b

b ≥

≥  a

a , то a(o)ij= aij, j=

, то a(o)ij= aij, j=  , иначе a(o)ij= b1j,b1j= aij, j=

, иначе a(o)ij= b1j,b1j= aij, j=  ; a(o)1j= b1j, j=

; a(o)1j= b1j, j=

k =  :

:

a ;

;

a ;

;

b ;

;

i =

c b

b то a

то a

иначе a ;

;

a ;

;

a , j=

, j=  (эта операция при k= 1 не выполняется),

(эта операция при k= 1 не выполняется),

a ;

;

a ;

;

k =  :

:

a

a ;

;

a ;

;

a , j=

, j=  ;

;

a ;

;

xij= a , j=

, j=

Рассмотрим работу устройства.

На вход 1 устройства подаются элементы aij в моменты времени taij= i+(n+1)j-n-1, i=  , j=

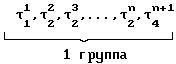

, j=  . На входы 5 и 6 подаются соответственно управляющие сигналы αиβ , принимающие значение 0 или 1. Первый режим работы вычислительного модуля 10 задается комбинацией сигналов τ1= (α, β)= (1,1), второй режим - τ2(1, 0), третий режим - τ3= (0, 0) и четвертый режим - τ4= (0, 1). Организация ввода управляющих сигналов τit (i=

. На входы 5 и 6 подаются соответственно управляющие сигналы αиβ , принимающие значение 0 или 1. Первый режим работы вычислительного модуля 10 задается комбинацией сигналов τ1= (α, β)= (1,1), второй режим - τ2(1, 0), третий режим - τ3= (0, 0) и четвертый режим - τ4= (0, 1). Организация ввода управляющих сигналов τit (i=  ), где t - номер такта, следующая:

), где t - номер такта, следующая:

(вторая группа повторяется n+m-2 раз, т. е. всего подается одна первая группа и n+m-1 вторых групп).

(вторая группа повторяется n+m-2 раз, т. е. всего подается одна первая группа и n+m-1 вторых групп).

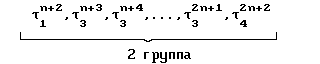

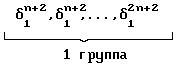

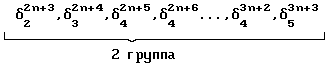

На входы 2, 3 и 4 подаются соответственно управляющие сигналы u, v и ω , принимающие значение 0 или 1. На входы 2, 3 и 4 подаются следующие комбинации сигналов u, v и ω : δ1= (u, v, ω )= (1, 1, 1), δ2= (1, 1, 0), δ3= (0, 1, 0), δ4= (0, 0, 1), δ5 = (1, 0, 0) и δ6 = (0, 0, 0). Организация ввода управляющих сигналов δiτ (i=  ) следующая:

) следующая:

. . . (третья группа повторяется n+m-3 раз, т. е. всего подается одна первая группа, одна вторая группа и n+m-2 третьих групп). На вход 7 постоянно подается нулевой сигнал, на вход 8 - единичный сигнал.

. . . (третья группа повторяется n+m-3 раз, т. е. всего подается одна первая группа, одна вторая группа и n+m-2 третьих групп). На вход 7 постоянно подается нулевой сигнал, на вход 8 - единичный сигнал.

Элементы xij формируются на выходе 12 устройства в моменты времени

txij= 2n(n+1)+i+j(n+1)-1.

Последний элемент xnm формируется на (2n2+m(n+1)+3n-1)-м такте. Период ввода элементов aij очередной задачи решения систем линейных алгебраических уравнений равен (n+1)(n+m) тактом.

Рассмотрим работу устройства для случая n= 3 и m= 1 (фиг. 2). Пусть требуется решисть систему линейных алгебраических уравнений вида

Входные и выходные данные, состояния регистров и триггеров вычислительных модулей 10, 111, 112 и 113 приведены в табл. 1-4.

Вчислительный модуль 10 обеспечивает выбор ведущего элемента по столбцам матрицы, т. е. перемещает строки так, чтобы строка, содержащая максимальный элемент первого столбца, была первой. С первого по третий такты выбирается ведущий элемент (амакс= а31= 2), который записывается в регистр 18, и на третьем такте в триггер 201 записывается значение γ= 1. На последующих тактах в соответствии с приведенным алгоритмом работы вычислительного модуля 10 происходит перемещение местами элементов первой и третьей строк исходной матрицы. На выходе 49 формируются элементы исходной матрицы в моменты времени

(i=  , j=

, j=  ).

).

В вычислительном модуле 111 с пятого по седьмой такты в регистры 60i (i= 1, n+1) записываются элементы a(o)i1 (i=  ), которые на последующих тактах циклически переписываются. На девятом такте формируется элемент a(1)42= a(1)12= a(o)12/a(o)11= 3/2, который записывается на девятом такте в регистр 61. На десятом такте формируется элемент a(1)22= a(o)22-a(o)21˙a(1)12= 2-0 ˙3/2= 2, который записывается на одиннадцатом такте в регистр 59. На одиннадцатом такте формируется элемент a(1)32= a(o)32-a(o)31˙ a(1)12= 2-1 ˙3/2= 1/2, который записывается в регистр 582 на двенадцатом такте, и в триггер записывается сигнал ϕ = 0, так как

), которые на последующих тактах циклически переписываются. На девятом такте формируется элемент a(1)42= a(1)12= a(o)12/a(o)11= 3/2, который записывается на девятом такте в регистр 61. На десятом такте формируется элемент a(1)22= a(o)22-a(o)21˙a(1)12= 2-0 ˙3/2= 2, который записывается на одиннадцатом такте в регистр 59. На одиннадцатом такте формируется элемент a(1)32= a(o)32-a(o)31˙ a(1)12= 2-1 ˙3/2= 1/2, который записывается в регистр 582 на двенадцатом такте, и в триггер записывается сигнал ϕ = 0, так как  a

a <

< a

a . На тринадцатом такте в регистр 582 записывается элемент а(1)42= 3/2. Элементы а(1)22, а(1)32 и а(1)42 выдаются на выход 115 соответственно на двенадцатом, тринадцатом и четырнадцатом тактах. На тринадцатом такте формируется элемент а(1)43= а(1)13= а(о)13/a(o)11= 0/2= 0, который на четырнадцатом такте записывается в регистр 61. На четырнадцатом такте формируется элемент a(1)23= а(о)23-а(о)21 ˙а(1)13= 1-0˙ 0= 1, который на пятнадцатом такте записывается в регистр 59. На пятнадцатом такте формируется элемент а(1)33= а(о)33-а(о)31 ˙а(о)13= 0-1 ˙0= 0, который на шестнадцатом такте записывается в регистр 582, так как триггер 624 находится в нулевом состоянии ( ϕ= 0). На семнадцатом такте элемент а(1)43= 0 записывается в регистр 581. Элементы а(1)23, а(1)33 и а(1)43выдаются на выход 115 соответственно на шестнадцатом, семнадцатом и восемнадцатом тактах. Аналогично формируются элемет a(1)44= a(1)14= a(o)14/a(o)11= 4/2= 2 (записывается в регистр 61 на восемнадцатом такте), элемент a(1)24= a(o)24-a(o)21 ˙a(1)14= 5-0 ˙2= 5 (записывается в регистр 582 на двадцатом такте), элемент a(1)34= a(o)34-a(o)31 ˙a(1)14= 3-1 ˙2= 1 (записывается в регистр 582 на двадцать первом такте). Элемент а(1)44= 2 записывается в регистр 581 на двадцатом такте. Элементы а(1)24, а(1)34 и а(1)44 выдаются на выход 115 соответственно на двадцатом, двадцать первом и двадцать втором тактах.

. На тринадцатом такте в регистр 582 записывается элемент а(1)42= 3/2. Элементы а(1)22, а(1)32 и а(1)42 выдаются на выход 115 соответственно на двенадцатом, тринадцатом и четырнадцатом тактах. На тринадцатом такте формируется элемент а(1)43= а(1)13= а(о)13/a(o)11= 0/2= 0, который на четырнадцатом такте записывается в регистр 61. На четырнадцатом такте формируется элемент a(1)23= а(о)23-а(о)21 ˙а(1)13= 1-0˙ 0= 1, который на пятнадцатом такте записывается в регистр 59. На пятнадцатом такте формируется элемент а(1)33= а(о)33-а(о)31 ˙а(о)13= 0-1 ˙0= 0, который на шестнадцатом такте записывается в регистр 582, так как триггер 624 находится в нулевом состоянии ( ϕ= 0). На семнадцатом такте элемент а(1)43= 0 записывается в регистр 581. Элементы а(1)23, а(1)33 и а(1)43выдаются на выход 115 соответственно на шестнадцатом, семнадцатом и восемнадцатом тактах. Аналогично формируются элемет a(1)44= a(1)14= a(o)14/a(o)11= 4/2= 2 (записывается в регистр 61 на восемнадцатом такте), элемент a(1)24= a(o)24-a(o)21 ˙a(1)14= 5-0 ˙2= 5 (записывается в регистр 582 на двадцатом такте), элемент a(1)34= a(o)34-a(o)31 ˙a(1)14= 3-1 ˙2= 1 (записывается в регистр 582 на двадцать первом такте). Элемент а(1)44= 2 записывается в регистр 581 на двадцатом такте. Элементы а(1)24, а(1)34 и а(1)44 выдаются на выход 115 соответственно на двадцатом, двадцать первом и двадцать втором тактах.

В вычислительном модуле 112 с тринадцатого по пятнадцатый такты записываются в регистры 60i (i=  ) элементы a(1)i2 (i=

) элементы a(1)i2 (i=  ), которые на последующих тактах циклически переписываются. На семнадцатом такте формируется элемент а(2)53= а(2)23= а(1)23/а(1)22= 1/2, который на восемнадцатом такте записывается в регистр 61. На восемнадцатом такте формируется элемент а(2)33= а(1)33-а(1)32˙ а(2)23= -1/4, который записывается в регистр 59 на девятнадцатом такте. Элемент а(2)43= а(1)43-а(1)42 ˙а(2)23= 0-3/2 ˙1/2= -3/4 формируется на девятнадцатом такте, который записывается в регистр 582 на двадцатом такте. Также на двадцатом такте в регистр 581 записывается элемент а(2)53= 1/2. Элементы а(2)33, а(2)43 и а(2)53 задаются на выход 115 соответственно на двадцатом, двадцать первом и двадцать втором тактах. На двадцать первом такте формируется элемент а(2)54= а(2)24-а(1)24˙а(1)22= 5/2, который записывается на двадцать втором такте в регистр 61. На двадцать втором такте формируется элемент а(2)34= а(1)34-а(1)32˙ а(2)24= 1-1/2˙ 5/2= -1/4 , который записывается в регистр 59 на двадцать третьем такте. Элемент а(2)44= а(1)44-а(1)42˙ а(2)24= -7/4 формируется на двадцать третьем такте и на двадцать четвертом такте записывается в регистр 582. Элемент а(2)54 записывается на двадцать четвертом такте в регистр 581. Элементы а(2)34, а(2)44 и а(2)54 выдаются на выход 115 соответственно на двадцать четвертом, двадцать пятом и двадцать шестом тактах. Состояние триггера 624 (значение ϕ ) на режим работы вычислительного модуля 112 не влияет, так как комбинация управляющих сигналов (u, v, ω, ε )= (0, 0, 0, 0) на входах 51, 52, 53 и 54 соответственно отсутствует.

), которые на последующих тактах циклически переписываются. На семнадцатом такте формируется элемент а(2)53= а(2)23= а(1)23/а(1)22= 1/2, который на восемнадцатом такте записывается в регистр 61. На восемнадцатом такте формируется элемент а(2)33= а(1)33-а(1)32˙ а(2)23= -1/4, который записывается в регистр 59 на девятнадцатом такте. Элемент а(2)43= а(1)43-а(1)42 ˙а(2)23= 0-3/2 ˙1/2= -3/4 формируется на девятнадцатом такте, который записывается в регистр 582 на двадцатом такте. Также на двадцатом такте в регистр 581 записывается элемент а(2)53= 1/2. Элементы а(2)33, а(2)43 и а(2)53 задаются на выход 115 соответственно на двадцатом, двадцать первом и двадцать втором тактах. На двадцать первом такте формируется элемент а(2)54= а(2)24-а(1)24˙а(1)22= 5/2, который записывается на двадцать втором такте в регистр 61. На двадцать втором такте формируется элемент а(2)34= а(1)34-а(1)32˙ а(2)24= 1-1/2˙ 5/2= -1/4 , который записывается в регистр 59 на двадцать третьем такте. Элемент а(2)44= а(1)44-а(1)42˙ а(2)24= -7/4 формируется на двадцать третьем такте и на двадцать четвертом такте записывается в регистр 582. Элемент а(2)54 записывается на двадцать четвертом такте в регистр 581. Элементы а(2)34, а(2)44 и а(2)54 выдаются на выход 115 соответственно на двадцать четвертом, двадцать пятом и двадцать шестом тактах. Состояние триггера 624 (значение ϕ ) на режим работы вычислительного модуля 112 не влияет, так как комбинация управляющих сигналов (u, v, ω, ε )= (0, 0, 0, 0) на входах 51, 52, 53 и 54 соответственно отсутствует.

В вычислительном модуле 113 двадцать первого по двадцать третий такты в регистры 60i (i=  ) записываются элементы а(2)33, а(2)43 и а(2)53, которые на последующих тактах циклически переписываются. На двадцать пятом такте формируется элемент а(3)64= а(3)34= а(2)34/а(2)33= 1, который записывается в регистр 61 на двадцать шестом такте. Элемент а(3)44= а(2)44-а(2)43˙ а(3)34= -7/4+3/4 ˙1= -1 формируется на двадцать шестом такте и записывается в регистр 582 на двадцать сельмом такте. На двадцать седьмом такте формируется элемент a(3)54= a(2)54-a(2)53˙ a(2)34= 5/2-1/2˙ 1= 2, который записывается на двадцать восьмом такте в регистр 582. Состояние триггера 624 (значение ϕ ) не влияет на режим работы вычислительного модуля 113 (отсутствует комбинация входных сигналов (u, v, ω, ε )= = ( 0, 0, 0, 0). Элементы х1= а(3)44= -1, х2= а(3)54= 2 и х3= а(3)64= 1 выдаются на выход 115 соответственно на двадцать восьмом, двадцать девятом и традцатом тактах.

) записываются элементы а(2)33, а(2)43 и а(2)53, которые на последующих тактах циклически переписываются. На двадцать пятом такте формируется элемент а(3)64= а(3)34= а(2)34/а(2)33= 1, который записывается в регистр 61 на двадцать шестом такте. Элемент а(3)44= а(2)44-а(2)43˙ а(3)34= -7/4+3/4 ˙1= -1 формируется на двадцать шестом такте и записывается в регистр 582 на двадцать сельмом такте. На двадцать седьмом такте формируется элемент a(3)54= a(2)54-a(2)53˙ a(2)34= 5/2-1/2˙ 1= 2, который записывается на двадцать восьмом такте в регистр 582. Состояние триггера 624 (значение ϕ ) не влияет на режим работы вычислительного модуля 113 (отсутствует комбинация входных сигналов (u, v, ω, ε )= = ( 0, 0, 0, 0). Элементы х1= а(3)44= -1, х2= а(3)54= 2 и х3= а(3)64= 1 выдаются на выход 115 соответственно на двадцать восьмом, двадцать девятом и традцатом тактах.

Таким образом, предлагаемое устройство по сравнению с прототипом обладает более высокой точностью вычисления за счет возможности выбора ведущего элемента. В прототипе не выбирается ведущий элемент и возможны случаи давления на нуль или числа, близкие по величине к нулю. Это приводит к неработоспособности прототипа.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ТРЕХ МАТРИЦ | 1990 |

|

RU2024933C1 |

| УСТРОЙСТВО ДЛЯ ОБРАЩЕНИЯ МАТРИЦ | 1989 |

|

SU1819020A1 |

| УСТРОЙСТВО ДЛЯ РЕШЕНИЯ СИСТЕМ ЛИНЕЙНЫХ АЛГЕБРАИЧЕСКИХ УРАВНЕНИЙ | 1989 |

|

SU1819019A1 |

| УСТРОЙСТВО ДЛЯ ОБРАЩЕНИЯ N X N МАТРИЦ | 1990 |

|

RU2037199C1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ДВУМЕРНОГО ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1991 |

|

RU2012048C1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ МАТРИЦ | 1991 |

|

RU2011221C1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ СОБСТВЕННЫХ ЗНАЧЕНИЙ (N X N)-МАТРИЦЫ | 1992 |

|

RU2012050C1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ТРЕХ МАТРИЦ | 1990 |

|

RU2024932C1 |

| УСТРОЙСТВО ДЛЯ РЕШЕНИЯ СИСТЕМ ЛИНЕЙНЫХ АЛГЕБРАИЧЕСКИХ УРАВНЕНИЙ | 1990 |

|

RU2037197C1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ МАТРИЦ | 1990 |

|

SU1779180A1 |

Изобретение относится к вычислительной технике и может быть использовано в высокопроизводительных машинах и устройствах обработки сигналов. Цель изобретения - повышение точности вычисления за счет выбора ведущего элемента. Цель достигается тем, что устройство содержит вычислительный модуль первого типа, реализующий основную операцию сравнения по модулю двух чисел, и n вычислительных модулей второго типа, реализующих основные арифметические операции - деление, умножение и вычитание чисел, где n - порядок системы линейных алгебраических уравнений. В основу работы устройства положен метод Гаусса-Жордана с частичным выбором ведущего элемента по столбцам матрицы. 1 з. п. ф-лы, 4 табл. , 5 ил.

) подключен к информационному входу (i + 1)-го вычислительного модуля первого типа, первый и второй настроечные выходы i-го вычислительного модуля первого типа подключены соответственно к первому и второму настроечным входам (i + 1)-го вычислительного модуля первого типа, информационный выход n-го вычислительного модуля первого типа подключен к выходу устройства, синхровход которого подключен к синхровходам всех вычислительных модулей первого типа, отличающееся тем, что, с целью повышения точности вычисления за счет выбора ведущего элемента по столбцам матрицы, введен вычислительный модуль второго типа, причем информационный вход устройства подключен к информационному входу вычислительного модуля второго типа, третий и четвертый настроечные выходы устройства подключены соответственно к третьему и четвертому настроечным входам первого вычислительного модуля первого типа, пятый настроечный вход устройства подключен к пятым настроечным входам j-х вычислительных модулей первого типа (j =

) подключен к информационному входу (i + 1)-го вычислительного модуля первого типа, первый и второй настроечные выходы i-го вычислительного модуля первого типа подключены соответственно к первому и второму настроечным входам (i + 1)-го вычислительного модуля первого типа, информационный выход n-го вычислительного модуля первого типа подключен к выходу устройства, синхровход которого подключен к синхровходам всех вычислительных модулей первого типа, отличающееся тем, что, с целью повышения точности вычисления за счет выбора ведущего элемента по столбцам матрицы, введен вычислительный модуль второго типа, причем информационный вход устройства подключен к информационному входу вычислительного модуля второго типа, третий и четвертый настроечные выходы устройства подключены соответственно к третьему и четвертому настроечным входам первого вычислительного модуля первого типа, пятый настроечный вход устройства подключен к пятым настроечным входам j-х вычислительных модулей первого типа (j =  ), шестой и седьмой настроечные входы устройства подключены соответственно к первому и второму настроечным входам вычислительного модуля второго типа, информационный выход которого подключен к информационному входу первого вычислительного модуля первого типа, третий и четвертый настроечные выходы i-го вычислительного модуля первого типа подключены соответственно к третьему и четвертому настроечным входам (i + 1)-го вычислительного модуля первого типа, синхровход устройства подключен к синхровходу вычислительного модуля второго типа, а в каждый вычислительный модуль первого типа введены делитель, коммутатор, узлы задержки с четвертого по седьмой, триггеры с третьего по седьмой, группы элементов И с десятой по двенадцатую, элементы И с шестого по четырнадцатый, пятую группу элементов ИЛИ, два элемента ИЛИ и элементы НЕ с третьего по пятый, при этом в каждом вычислительном модуле первого типа информационный вход модуля подключен к первым входам элементов И первой и второй групп, выходы которых подключены соответственно к первым входам элементов ИЛИ первой и второй групп, выходы которых подключены к информационным входам первых регистров соответственно первого и второго узлов задержки, выход первого регистра первого узла задержки подключен к первым входам вычитателя, делителя и элементов И третьей группы, выходы элементов И третьей группы подключены к первым входам элементов ИЛИ третьей группы, вторые, третьи и четвертые входы которых подключены соответственно к выходам элементов И четвертой, пятой и шестой групп, а выходы - к информационному входу второго регистра первого узла задержки, выход K-го регистра первого узла задержки (K =

), шестой и седьмой настроечные входы устройства подключены соответственно к первому и второму настроечным входам вычислительного модуля второго типа, информационный выход которого подключен к информационному входу первого вычислительного модуля первого типа, третий и четвертый настроечные выходы i-го вычислительного модуля первого типа подключены соответственно к третьему и четвертому настроечным входам (i + 1)-го вычислительного модуля первого типа, синхровход устройства подключен к синхровходу вычислительного модуля второго типа, а в каждый вычислительный модуль первого типа введены делитель, коммутатор, узлы задержки с четвертого по седьмой, триггеры с третьего по седьмой, группы элементов И с десятой по двенадцатую, элементы И с шестого по четырнадцатый, пятую группу элементов ИЛИ, два элемента ИЛИ и элементы НЕ с третьего по пятый, при этом в каждом вычислительном модуле первого типа информационный вход модуля подключен к первым входам элементов И первой и второй групп, выходы которых подключены соответственно к первым входам элементов ИЛИ первой и второй групп, выходы которых подключены к информационным входам первых регистров соответственно первого и второго узлов задержки, выход первого регистра первого узла задержки подключен к первым входам вычитателя, делителя и элементов И третьей группы, выходы элементов И третьей группы подключены к первым входам элементов ИЛИ третьей группы, вторые, третьи и четвертые входы которых подключены соответственно к выходам элементов И четвертой, пятой и шестой групп, а выходы - к информационному входу второго регистра первого узла задержки, выход K-го регистра первого узла задержки (K =  ) подключен к информационному входу (K + 1)-го регистра первого узла задержки, выход n-го регистра первого узла задержки подключен к первым входам элементов И седьмой группы, выходы которых подключены к первым входам элементов ИЛИ четвертой группы, вторые входы которых подключены к выходу элементов И восьмой группы, а выходы - к информационному выходу модуля, вторые входы элементов ИЛИ первой группы подключены к выходам элементов И девятой группы, первые входы которых подключены к первому входу умножителя и выходу первого регистра, информационный вход которого подключен к выходу делителя, а синхровход - к выходу первого элемента И, вторые входы элементов ИЛИ второй группы подключены к выходам элементов И десятой группы, первые входы которых подключены к выходу (n + 1)-го регистра второго узла задержки, выход первого регистра которого подключен к второму входу делителя, информационному входу второго регистра второго узла задержки и второму входу умножителя, выход которого подключен к второму входу вычитателя, выход которого подключен к первым входам элементов И четвертой и одиннадцатой групп и первому входу коммутатора, выход l-го регистра второго узла задержки подключен к информационному входу (l + 1)-го регистра второго узла задержки (l =

) подключен к информационному входу (K + 1)-го регистра первого узла задержки, выход n-го регистра первого узла задержки подключен к первым входам элементов И седьмой группы, выходы которых подключены к первым входам элементов ИЛИ четвертой группы, вторые входы которых подключены к выходу элементов И восьмой группы, а выходы - к информационному выходу модуля, вторые входы элементов ИЛИ первой группы подключены к выходам элементов И девятой группы, первые входы которых подключены к первому входу умножителя и выходу первого регистра, информационный вход которого подключен к выходу делителя, а синхровход - к выходу первого элемента И, вторые входы элементов ИЛИ второй группы подключены к выходам элементов И десятой группы, первые входы которых подключены к выходу (n + 1)-го регистра второго узла задержки, выход первого регистра которого подключен к второму входу делителя, информационному входу второго регистра второго узла задержки и второму входу умножителя, выход которого подключен к второму входу вычитателя, выход которого подключен к первым входам элементов И четвертой и одиннадцатой групп и первому входу коммутатора, выход l-го регистра второго узла задержки подключен к информационному входу (l + 1)-го регистра второго узла задержки (l =  ), выходы элементов И одиннадцатой и двенадцатой групп подключены соответственно к первым и вторым входам элементов ИЛИ пятой группы, выходы которых подключены к информационному входу второго регистра, синхровход которого подключен к выходу второго элемента И, а выход - к первым входам элементов И пятой и восьмой групп и второму входу коммутатора, первые, вторые и третьи выходы которого подключены соответственно к первым входам элементов И шестой группы, первым входам элементов И двенадцатой группы и первому входу третьего элемента И, выход которого подключен к первому входу первого элемента ИЛИ, второй вход которого подключен к выходу четвертого элемента И, а выход - к информационному входу первого триггера третьего узла задержки, выход i-го триггера которого (j =

), выходы элементов И одиннадцатой и двенадцатой групп подключены соответственно к первым и вторым входам элементов ИЛИ пятой группы, выходы которых подключены к информационному входу второго регистра, синхровход которого подключен к выходу второго элемента И, а выход - к первым входам элементов И пятой и восьмой групп и второму входу коммутатора, первые, вторые и третьи выходы которого подключены соответственно к первым входам элементов И шестой группы, первым входам элементов И двенадцатой группы и первому входу третьего элемента И, выход которого подключен к первому входу первого элемента ИЛИ, второй вход которого подключен к выходу четвертого элемента И, а выход - к информационному входу первого триггера третьего узла задержки, выход i-го триггера которого (j =  ) подключен к информационному входу (j + 1)-го триггера третьего узла задержки, а прямой выход (n + 1)-го триггера подключен к первому входу четвертого элемента И, четвертый настроечный вход модуля подключен к первому входу второго элемента ИЛИ, выход которого подключен к информационному входу первого триггера четвертого узла задержки, выход l-го триггера которого (l =

) подключен к информационному входу (j + 1)-го триггера третьего узла задержки, а прямой выход (n + 1)-го триггера подключен к первому входу четвертого элемента И, четвертый настроечный вход модуля подключен к первому входу второго элемента ИЛИ, выход которого подключен к информационному входу первого триггера четвертого узла задержки, выход l-го триггера которого (l =  1) подключен к информационному входу (l + 1)-го триггера четвертого узла задержки, выход n-го триггера четвертого узла задержки подключен к четвертому настроечному выходу модуля, пятый настроечный вход которого подключен к первому входу пятого элемента И, выход которого подключен к второму входу второго элемента ИЛИ, первый настроечный вход модуля подключен к первым входам шестого, седьмого и восьмого элементов И, к входу первого элемента НЕ и информационному входу первого триггера пятого узла задержки, выход K-го триггера p-го узла задержки (K =

1) подключен к информационному входу (l + 1)-го триггера четвертого узла задержки, выход n-го триггера четвертого узла задержки подключен к четвертому настроечному выходу модуля, пятый настроечный вход которого подключен к первому входу пятого элемента И, выход которого подключен к второму входу второго элемента ИЛИ, первый настроечный вход модуля подключен к первым входам шестого, седьмого и восьмого элементов И, к входу первого элемента НЕ и информационному входу первого триггера пятого узла задержки, выход K-го триггера p-го узла задержки (K =  , p =

, p =  ) подключен к информационному входу (K + 1)-го триггера p-го узла задержки, второй настроечный вход модуля подключен к вторым входам шестого и седьмого элементов И, первому входу девятого элемента И, входу второго элемента НЕ и информационному входу первого триггера шестого узла задержки, третий настроечный вход вычислительного модуля подключен к третьему входу шестого элемента И, первому входу десятого элемента И, входу третьего элемента НЕ и информационному входу первого триггера седьмого узла задержки, выходы (2n + 2)-х триггеров пятого, шестого и седьмого узлов задержки подключены соответственно к первому, второму и третьему настроечным выходам модуля, выход шестого элемента И подключен к входу четвертого элемента НЕ и вторым входам элементов И второй группы, выход четвертого элемента НЕ подключен к вторым входам элементов И десятой группы и второму входу четвертого элемента И, выход третьего элемента НЕ подключен к вторым входам восьмого и девятого элементов И, к первому входу одиннадцатого элемента И и третьему входу седьмого элемента И, выход которого подключен к вторым входам элементов И первой и третьей групп и информационному входу первого триггера, выход которого подключен к первому входу первого элемента И, выход второго элемента НЕ подключен к вторым входам десятого и одиннадцатого элементов И и третьему входу восьмого элемента И, выход которого подключен к вторым входам элементов И третьей и девятой групп, второму входу пятого элемента И и информационному входу второго триггера, прямой выход которого подключен к вторым входам элементов И восьмой группы, а инверсный выход - к вторым входам элементов седьмой группы, выход первого элемента НЕ подключен к третьим входам девятого, десятого и одиннадцатого элементов И и первому входу двенадцатого элемента И, выход которого подключен к вторым входам элементов И первой группы и информационному входу третьего триггера, выход которого подключен к вторым входам элементов И четвертой группы, выход пятого элемента НЕ подключен к четвертым входам девятого, десятого и одиннадцатого элементов И, выход девятого элемента И подключен к вторым входам элементов И первой группы и информационному входу четвертого триггера, выход которого подключен к вторым входам второго элемента И и элементов И одиннадцатой группы, выход десятого элемента И подключен к вторым входам элементов И первой группы и информационному входу пятого триггера, выход которого подключен к вторым входам элементов И шестой и двенадцатой групп и вторым входам второго и третьего элементов И, выход одиннадцатого элемента И подключен к первым входам тринадцатого и четырнадцатого элементов И, прямой выход (n + 1)-го триггера третьего узла задержки подключен к второму входу тринадцатого элемента И, а инверсный выход - к второму входу четырнадцатого элемента И, выход которого подключен к информационному входу шестого триггера, выход которого подключен к вторым входам элементов И четвертой группы, выход тринадцатого элемента И подключен к вторым входам элементов И первой группы и информационному входу седьмого триггера, выход которого подключен к вторым входам элементов И пятой и одиннадцатой групп и к первому входу второго элемента И, синхровход модуля подключен к синхровходам всех регистров первого и второго узлов задержки, всех триггеров с третьего по седьмой узлов задержки, с первого по седьмой триггеров, к вторым входам первого и второго элементов И, четвертый настроечный вход модуля подключен к входу пятого элемента НЕ и второму входу двенадцатого элемента И.

) подключен к информационному входу (K + 1)-го триггера p-го узла задержки, второй настроечный вход модуля подключен к вторым входам шестого и седьмого элементов И, первому входу девятого элемента И, входу второго элемента НЕ и информационному входу первого триггера шестого узла задержки, третий настроечный вход вычислительного модуля подключен к третьему входу шестого элемента И, первому входу десятого элемента И, входу третьего элемента НЕ и информационному входу первого триггера седьмого узла задержки, выходы (2n + 2)-х триггеров пятого, шестого и седьмого узлов задержки подключены соответственно к первому, второму и третьему настроечным выходам модуля, выход шестого элемента И подключен к входу четвертого элемента НЕ и вторым входам элементов И второй группы, выход четвертого элемента НЕ подключен к вторым входам элементов И десятой группы и второму входу четвертого элемента И, выход третьего элемента НЕ подключен к вторым входам восьмого и девятого элементов И, к первому входу одиннадцатого элемента И и третьему входу седьмого элемента И, выход которого подключен к вторым входам элементов И первой и третьей групп и информационному входу первого триггера, выход которого подключен к первому входу первого элемента И, выход второго элемента НЕ подключен к вторым входам десятого и одиннадцатого элементов И и третьему входу восьмого элемента И, выход которого подключен к вторым входам элементов И третьей и девятой групп, второму входу пятого элемента И и информационному входу второго триггера, прямой выход которого подключен к вторым входам элементов И восьмой группы, а инверсный выход - к вторым входам элементов седьмой группы, выход первого элемента НЕ подключен к третьим входам девятого, десятого и одиннадцатого элементов И и первому входу двенадцатого элемента И, выход которого подключен к вторым входам элементов И первой группы и информационному входу третьего триггера, выход которого подключен к вторым входам элементов И четвертой группы, выход пятого элемента НЕ подключен к четвертым входам девятого, десятого и одиннадцатого элементов И, выход девятого элемента И подключен к вторым входам элементов И первой группы и информационному входу четвертого триггера, выход которого подключен к вторым входам второго элемента И и элементов И одиннадцатой группы, выход десятого элемента И подключен к вторым входам элементов И первой группы и информационному входу пятого триггера, выход которого подключен к вторым входам элементов И шестой и двенадцатой групп и вторым входам второго и третьего элементов И, выход одиннадцатого элемента И подключен к первым входам тринадцатого и четырнадцатого элементов И, прямой выход (n + 1)-го триггера третьего узла задержки подключен к второму входу тринадцатого элемента И, а инверсный выход - к второму входу четырнадцатого элемента И, выход которого подключен к информационному входу шестого триггера, выход которого подключен к вторым входам элементов И четвертой группы, выход тринадцатого элемента И подключен к вторым входам элементов И первой группы и информационному входу седьмого триггера, выход которого подключен к вторым входам элементов И пятой и одиннадцатой групп и к первому входу второго элемента И, синхровход модуля подключен к синхровходам всех регистров первого и второго узлов задержки, всех триггеров с третьего по седьмой узлов задержки, с первого по седьмой триггеров, к вторым входам первого и второго элементов И, четвертый настроечный вход модуля подключен к входу пятого элемента НЕ и второму входу двенадцатого элемента И. ) подключен к информационному входу (j + 1)-го триггера, выходы элементов или первой группы подключены к информационному входу первого регистра второго узла задержки, выход j-го регистра которого подключен к информационному входу (j + 1)-го регистра, выход (n + 1)-го регистра второго узла задержки подключен к вторым входам элементов И шестой группы, синхровход модуля подключен к синхровходам всех регистров и триггеров, к третьим входам второго и четвертого элементов И и второму входу третьего элемента И, третьи и четвертые входы элементов ИЛИ первой группы соединены соответственно с выходами элементов И третьей и четвертой групп.

) подключен к информационному входу (j + 1)-го триггера, выходы элементов или первой группы подключены к информационному входу первого регистра второго узла задержки, выход j-го регистра которого подключен к информационному входу (j + 1)-го регистра, выход (n + 1)-го регистра второго узла задержки подключен к вторым входам элементов И шестой группы, синхровход модуля подключен к синхровходам всех регистров и триггеров, к третьим входам второго и четвертого элементов И и второму входу третьего элемента И, третьи и четвертые входы элементов ИЛИ первой группы соединены соответственно с выходами элементов И третьей и четвертой групп.

Авторы

Даты

1994-04-30—Публикация

1991-03-31—Подача