Изобретение относится к вычислительной технике и может быть использовано в системах группового управления станками с числовым программнымм управлением и другими объектами.

Цель изобретения - повышение быстродействия и упрощение устройства за счет сокращения внешних выводов.

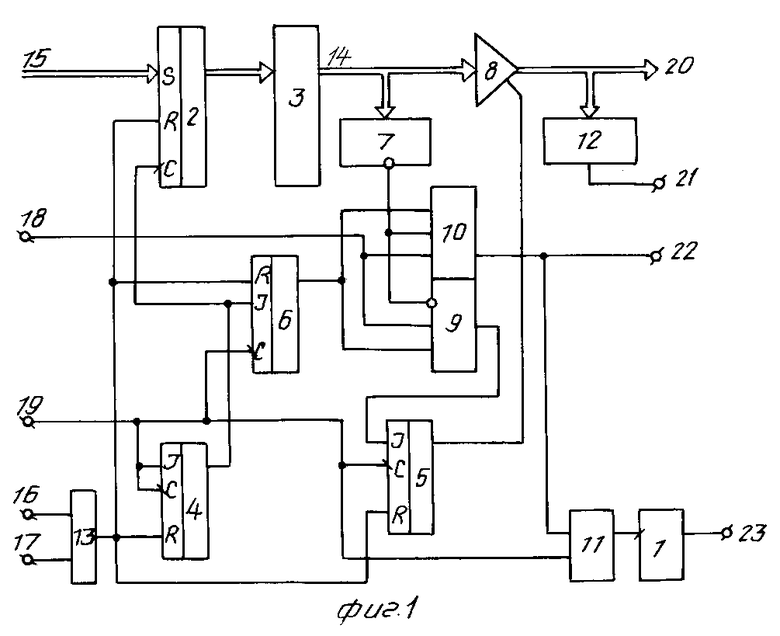

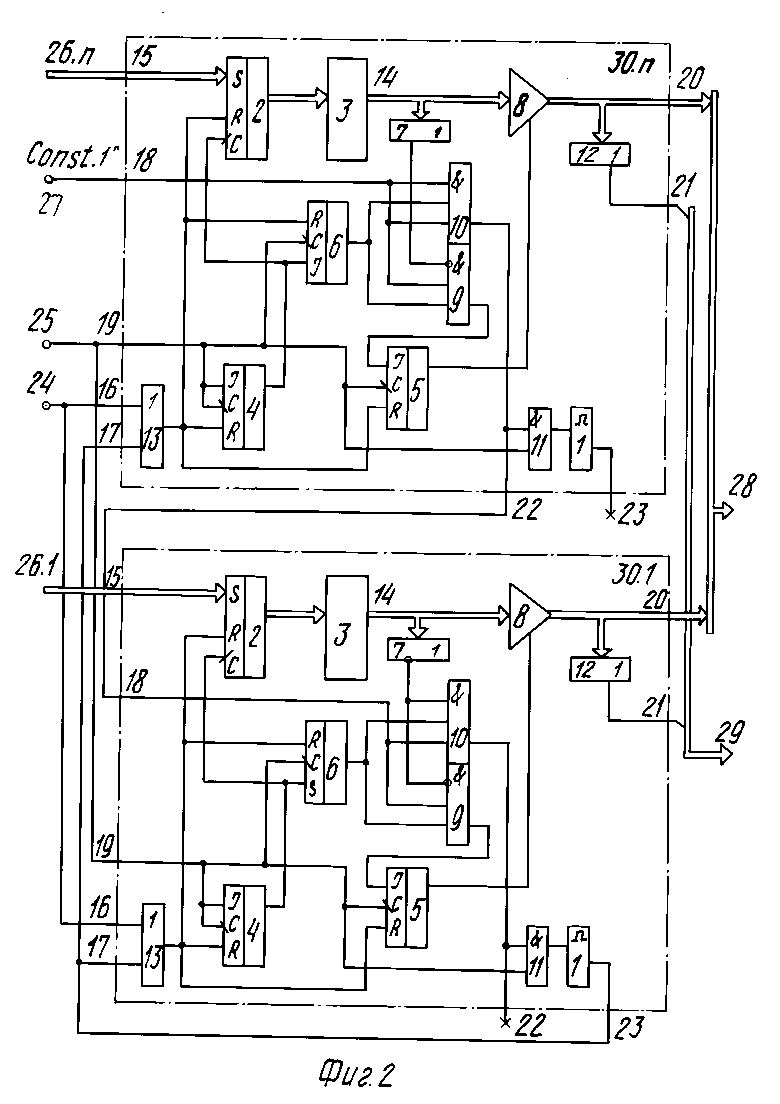

На фиг. 1 приведена функциональная схема устройства; на фиг. 2 - функциональная схема устройства приоритета на n х К входов запроса, реализованного объединением n предлагаемых устройств приоритета на К входов запроса каждое.

Многоканальное устройство приоритета (фиг. 1) содержит одновибратор 1, регистр 2, приоритетный шифратор 3, первый 4, второй 5, третий 6 триггеры, элемент ИЛИ-НЕ 7, буферный регистр 8, первый 9, второй 10 и третий 11 элементы И, первый 12 и второй 13 элементы ИЛИ, выход 14 приоритетного шифратора, запросный вход 15 устройства, первый 16 и второй 17 входы сброса устройства, вход 18 разрешения устройства, вход 19 синхронизации устройства, выход 20 кода номера запуска, сигнальный вход 21 устройства, выход 22 разрешения устройства, выход 23 сброса устройства.

Рассмотрим функционирование многоканального устройства приоритета.

В исходном состоянии все элементы памяти находятся в нулевом состоянии (цепи установки в исходное состояние на фиг. 1, 2 условно не показаны).

Функционирование устройства начинается после поступления синхроимпульсов на вход 25 устройства. По первому синхроимпульсу, который с входа 25 поступит на входы 19 модулей 30.1-30. n триггеры 4 всех модулей установятся в единичное состояние (по заднему фронту синхроимпульса). Выходные сигналы триггеров 4 своим передним фронтом произведут запись поступивших к этому моменту запросов в регистры 2 модулей 30.1-30. n. Записанные в регистры 2 запросы с их выходов поступят на входы приоритетных шифраторов 3, которые сформируют на своих выходах номера наиболее приоритетных в своих группах запросов, двоичные коды запросов с выходов шифраторов 3 поступят на входы групп буферных элементов 8 и входы элементов ИЛИ-НЕ 7 своих модулей.

Если в регистр 2 модуля 30. i поступил хотя бы один запрос, то на выходе элемента ИЛИ-НЕ 7 этого модуля появится нулевой сигнал, который откроет элемент И 9 и закроет элемент И 10 своего модуля.

После окончания переходных процессов в элементах 4, 2, 3, 7, на вход 25 устройства поступит второй синхроимпульс, который установит в единичное состояние триггеры 6 модулей 30. n-30.1. Выходные сигналы триггеров 6 откроют элементы И 9, 10 своих модулей.

Если на входы 15 модуля 30. n поступил хотя бы один запрос, то единичный сигнал, постоянно присутствующий на входе 18 этого модуля, пройдет через элемент И 9 на вход I триггера 5, а нулевой сигнал с выхода элемента И 10 пройдет на выход 22 модуля 30. n и далее на вход 18 модуля 30. n-1, в котором закроет элементы И 9, 10 этого модуля. Это, в свою очередь, приведет к закрытию элементов И 9, 10, модулей 30. n - 2-30.1.

После окончания описанного переходного процесса в устройстве на его вход 25 поступит третий синхроимпульс, который поступит на входы триггеров 5 и элементов И 11 своих модулей. В результате этого триггер 5 модуля 30. n переключится в единичное состояние и его выходной сигнал откроет группу буферных регистров 8 модуля 30. n. Таким образом, код наиболее приоритетного запроса наиболее приоритетной n-й группы запросов поступит на выход 20 модуля 30. n и далее через шину номера запроса на выход 28 номера запроса устройства. Одновременно на выходе элемента ИЛИ 12 модуля 30. n сформируется единичный сигнал, который пройдет на n-й выход группы выходов 29 устройства, указывая на принадлежность найденного запроса n-й группе запросов.

Обслуживающее устройство произведет считывание номеров запроса и группы запросов с выходов 28, 29 устройства и приступит к его обслуживанию. После окончания обслуживания этого запроса соответствующий ему сигнал будет снят с входа 15 модуля 30. n, а на вход 24 устройства от обслуживающего устройства поступит сигнал сброса, который пройдет через элементы ИЛИ 13 модулей 30. n-30.1 и возвратит все элементы памяти в исходное состояние. Устройство приоритета приступит к поиску очередного запроса.

Если при очередном цикле поиска наиболее приоритетного запроса последний будет обнаружен модулем 30. i (i < n), то есть на входы модулей 30. n. i+1 запросы не поступили, то на выходе элемента ИЛИ-НЕ 7 этого модуля появится нулевой сигнал, который откроет элемент И 9 и закроет элемент И 10. В результате этого единичный сигнал с выхода 22 модуля 30. i+1 пройдет через элемент И 9 на вход I триггера 5 модуя 30. i и по очередному синхроимпульсу триггер 5 установится в единицу и откроет группу буферных регистров И 8 модуля 30. i. Таким образом, на выходы 28, 29 устройства поступят номер запроса, принадлежащего i-й группе, и единичный сигнал, указывающий на его принадлежность к i-й группе. Обслуживающее устройство произведет считывание и обработку этого запроса.

Если при очередном цикле поиска запрос не обнаружен ни в одной из групп запросов, то после поступления второго синхроимпульса на выходе элемента И 10 модуля 30.1 сформируется единичный сигнал, который откроет элемент И 11, и третий синхроимпульс пройдет через открытый элемент И 11 и запустит одновибратор 1 модуля 30.1. Его выходной сигнал пройдет на выход 23 модуля 30.1 и далее на входы 17 модулей 30.1-30. n и надежно установит в исходное состояние регистры 2 и триггеры 4-6 этих модулей. При поступлении следующей триады синхроимпульсов на вход 25 устройства цикл поиска наиболее приоритетного запроса повторится.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО УПРАВЛЕНИЯ ДОСТУПОМ К МАГИСТРАЛИ В ЛОКАЛЬНЫХ СЕТЯХ С МАГИСТРАЛЬНОЙ АРХИТЕКТУРОЙ | 1991 |

|

RU2017214C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ДОСТУПОМ К МАГИСТРАЛИ В ЛОКАЛЬНЫХ ВЫЧИСЛИТЕЛЬНЫХ СЕТЯХ С МАГИСТРАЛЬНОЙ АРХИТЕКТУРОЙ | 1991 |

|

RU2012042C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ДОСТУПОМ К МАГИСТРАЛИ В ЛОКАЛЬНЫХ СЕТЯХ С МАГИСТРАЛЬНОЙ АРХИТЕКТУРОЙ | 1991 |

|

RU2017204C1 |

| ТРЕХКАНАЛЬНАЯ РЕЗЕРВИРОВАННАЯ СИСТЕМА | 1989 |

|

RU1819116C |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ КАЧЕСТВА МАГНИТНОГО НОСИТЕЛЯ | 1992 |

|

RU2040050C1 |

| Устройство приоритета | 1990 |

|

SU1789984A1 |

| Устройство приоритета | 1991 |

|

SU1833874A1 |

| Устройство для обслуживания запросов | 1990 |

|

SU1805467A1 |

| УСТРОЙСТВО ДЛЯ ПРОГРАММНОГО КОНТРОЛЯ | 1991 |

|

RU2015523C1 |

| Многоканальное устройство для включения резервных радиостанций | 1990 |

|

SU1748299A1 |

Изобретение относится к вычислительной технике и может быть использовано в системах группового управления станками с числовым программным управлением и другими объектами. Цель изобретения - повышение быстродействия и упрощения устройства за счет сокращения числа внешних выводов. Многоканальное устройство приоритета содержит регистр, шифратор, одновибратор, триггеры, элемент ИЛИ - НЕ, буферный регистр, элементы И, элементы ИЛИ. 2 ил.

МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ПРИОРИТЕТА, содержащее регистр, первый и второй триггеры, первый и второй элементы И, первый элемент ИЛИ, одновибратор, буферный регистр, причем запросный вход устройства соединен с S-входом регистра, вход синхронизация устройства подключен к C-входу первого триггера, выход первого элемента И подключен через одновибратор к выходу сброса устройства, выход буферного регистра подключен к выходу кода номера запуска устройства, выход первого элемента ИЛИ подключен к сигнальному выходу устройства, отличающееся тем, что, с целью повышения быстродействия и упрощения устройства за счет сокращения числа внешних выводов, в него введены третий триггер, шифратор, второй элемент ИЛИ, третий элемент И, элемент ИЛИ - НЕ, причем первый и второй входы сброса устройства соединены с входами второго элемента ИЛИ, выход которого подключен к входам сброса с первого по третий триггеры и регистра, вход разрешения устройства подключен к первым входам второго и третьего элементов И, прямой выход первого триггера подключен к синхровходу регистра и входу второго триггера, выход которого подключен к вторым входам второго и третьего элементов И, вход синхронизации устройства подключен к первому входу первого элемента И, к J-входу первого и к C-входам второго и третьего триггеров, прямой выход третьего триггера подключен к управляющему входу буферного регистра, группа выходов регистра через шифратор подключена к группе информационных входов буферного регистра и группе входов элемента ИЛИ - НЕ, выход которого подключен к третьему входу третьего элемента И и третьему инверсному входу второго элемента И, выход которого подключен к J-входу третьего триггера, выход третьего элемента И подключен к второму входу первого элемента И и выходу разрешения устройства, группа выходов буферного регистра подключена к группе входов первого элемента ИЛИ.

Авторы

Даты

1994-05-30—Публикация

1991-04-03—Подача