Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах контроля и испытаний сложных программно-аппаратных средств.

Известно устройство для программного контроля и управления, содержащее блок памяти, счетчики, триггеры, генератор импульсов, элементы И, ИЛИ, НЕ [1].

Недостатком устройства является узкая область применения, обусловленная невозможностью программного управления частотой выдачи тестовых сигналов и определения предельной частоты устойчивого функционирования объекта.

Известно устройство для программного контроля и управления, содержащее блок памяти, первый и второй счетчики, мультиплексор, дешифратор, генератор импульсов, триггер, первый-третий элементы И, элемент ИЛИ, элемент НЕ, элементы задержки, группу элементов И [2].

Недостатком данного устройства является узкая область применения, обусловленная невозможностью выдачи многоразрядных управляющих и тестовых воздействий на объект, отсутствием возможности реализации алгоритма определения граничных частот, на которых теряется работоспособность устройства, невозможностью реализации гибких процедур управления заданием частот тестирования, допустимого числа ошибок и т.д. Эти недостатки являются следствием отсутствия в прототипе специальных программно-аппаратных средств реализации процедур тестового контроля с варьируемыми параметрами.

Целью изобретения является расширение области применения устройства.

Цель достигается тем, что в устройство для программного контроля, содержащее блок памяти тестовых задач, делитель частоты, счетчик адреса, генератор импульсов, мультиплексор, триггер пуска, формирователь импульсов, первый и второй элементы И, причем вход пуска устройства соединен с единичным ходом триггера пуска, выход которого соединен с входом генератора импульсов, первый и второй выходы формирователя импульсов соединены с первыми входами первого и второго элементов И, выход счетчика адреса соединен с входом блока памяти тестовых задач, выход циклов которого и вход первого элемента И соединены соответственно с информационным и синхронизирующим входами делителя частоты, введены блоки памяти тестовых программ и несовпадений, блок задания частоты, счетчик несовпадений, регистр, первая и вторая схема сравнения, коммутатор, триггер останова, сумматор по модулю два, при этом выходы генератора импульсов соединены с информационными входами мультиплексора, выход которого соединен с входом формирователя импульсов, первый выход которого соединен с входом синхронизации триггера останова, третий выход - с входом синхронизации регистра и является выходом синхронизации устройства, выходы начальной частоты и управления счетом блока памяти тестовых задач соединены соответственно с информационным и управляющими выходами блока задания частоты, выход которого соединен с адресными входами мультиплексора, блока памяти несовпадений и выходом кода частоты устройства, выход адреса блока памяти тестовых задач соединен с первым информационным входом коммутатора, выход которого соединен с информационным входом регистра, выход конца работы блока памяти тестовых задач является выходом конца работы устройства и соединен с первым входом элемента ИЛИ, выход которого соединен с нулевым входом триггера пуск, выход конца программы регистра соединен с управляющими входами коммутатора, инверсным входом второго элемента И и вторым входом первого элемента И, выход которого соединен с входом синхронизации блока задания частоты и установочным входом счетчика несовпадений, выходы теста и эталона соединены соответственно с выходом теста устройства и первым входом первой схемы сравнения, второй вход которой является входом реакции устройства, а выход соединен с вторым прямым входом второго элемента И, выход модифицируемого разряда регистра и вход условий устройства соединены соответственно с первыми и вторым входами сумматора по модулю два, выход которого совместно с выходами немодифицируемых разрядов регистра соединены с вторым информационным входом коммутатора, выход делителя частоты соединен с установочным входом блока задания частоты и счетным входом счетчика адреса, информационный и синхронизирующий входы которого являются входами начального адреса и синхронизации устройства соответственно, выход второго элемента И соединен со счетным входом счетчика несовпадений, выход которого и выход блока памяти несовпадений соединены с первым и вторым входами второй схемы сравнения соответственно, выход второй схемы сравнения соединен с единичным входом триггера останова, выход которого соединен с вторым входом элемента ИЛИ и является выходом останова устройства.

Сущность изобретения состоит в расширении области применения путем обеспечения возможности реализации тестовых процедур с варьируемыми параметрами. Это свойство устройства реализуется благодаря введению новой дисциплины функционирования, суть которой состоит в следующем.

Процесс контроля представляет собой последовательное выполнение тестовых задач ТЗ1, ТЗ2, ..., ТЗк. Код каждой из тестовых задач ТЗiсодержит начальный адрес тестовой программы ее выполнения АТПi, число циклов решения этой задачи ЧЦРi, начальную частоту тестирования НЧТi, биты управления счетом БУСi и конца работы БКPi:

ТЗi={АТПi, ЧЦРi, НЧТi, БУСi, БКРi}. (1)

Другими словами каждая из тестовых задач ТЗi выполняется ЧЦРi раз по тестовой программе ТПi, определяемой АТПi, на частотах fi1,...,fini, причем fi1=НЧТi (2);

fini=НЧТi ± Δf ЧЦРi1, (3)

где Δ f - приращение частоты за один цикл.

Знак формулы (3) определяется БУСi.

Кроме того, по каждой частоте тестирования задается число допустимых несовпадений реакций обмена контроля и эталонных реакций, заявляемых в тестовой программе.

Сущность изобретения реализуется путем введения следующих элементов и связей, определяющих соответствие заявляемого устройства критерию "новизны". Введение блока памяти тестовых программ, коммутатора, регистра и их связей позволяет реализовать процесс выполнения тестовых программ при контроле. Введение сумматора по модулю два и его связей обеспечивает модификацию программы по текущему состоянию объекта. Введение блока задания частоты и его связей позволяет управлять частотой выполнения тестовых программ. Введение блока памяти несовпадений, первой и второй схем сравнения, счетчика несовпадений, триггера останова и их связей обеспечивает реализацию гибкого механизма определения числа несовпадений эталонов и реакций в зависимости от частоты тестирования.

Таким образом, заявляемое устройство соответствует критерию "существенные отличия", поскольку в известных технических решениях отсутствуют указанные выше элементы и связи, и вследствие этого не обеспечивается свойство реализации гибких процедур тестирования с варьируемыми параметрами. При использовании заявляемого устройства может быть потерян положительный эффект, состоящий в расширении области применения, повышении гибкости и уменьшении времени испытаний. Количественная оценка положительного эффекта приведена ниже.

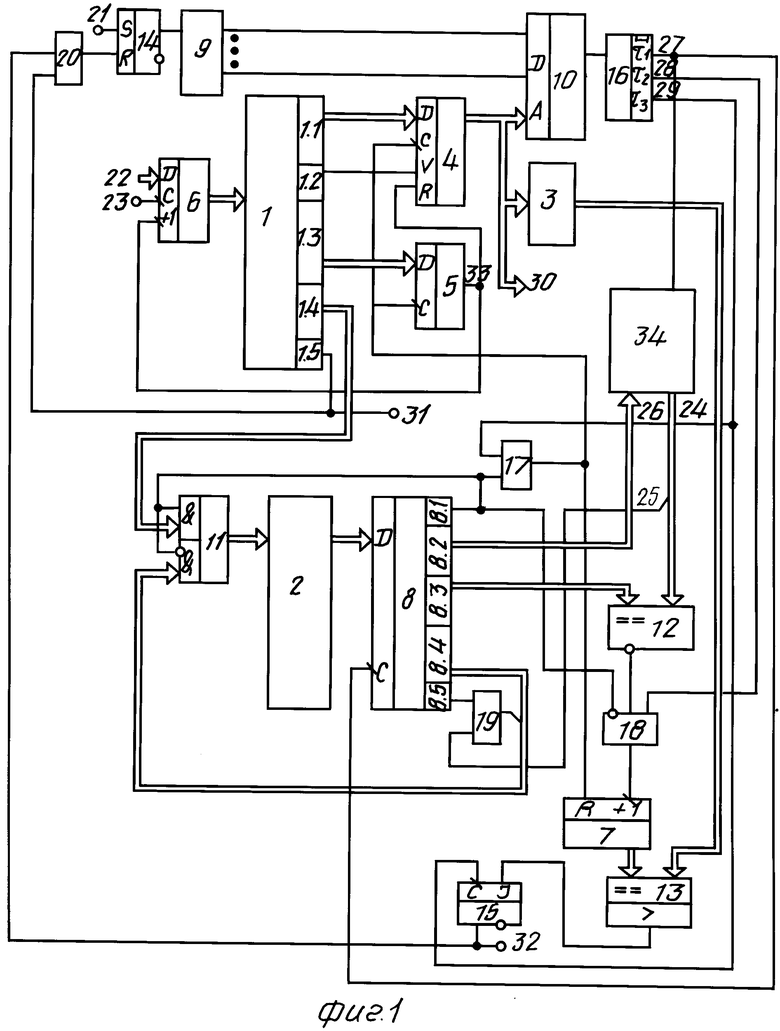

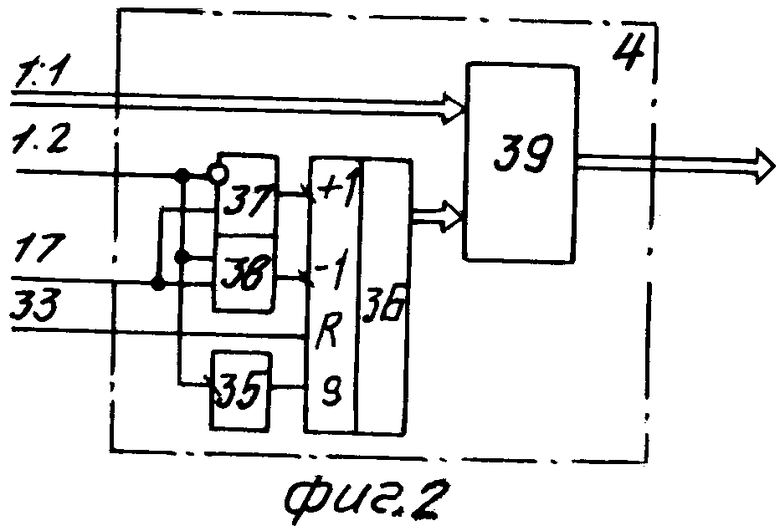

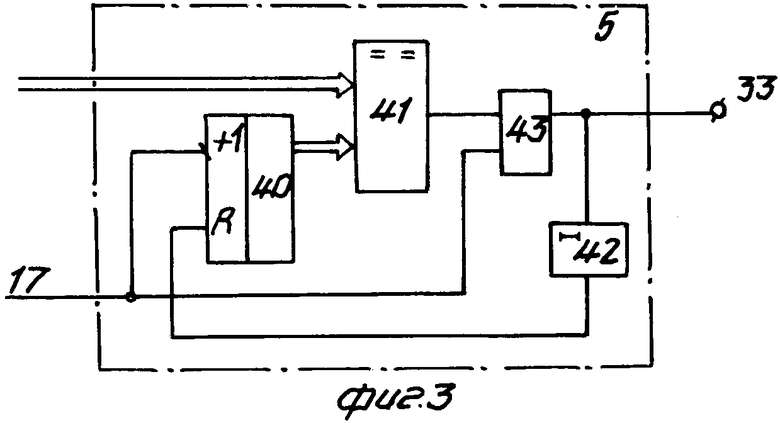

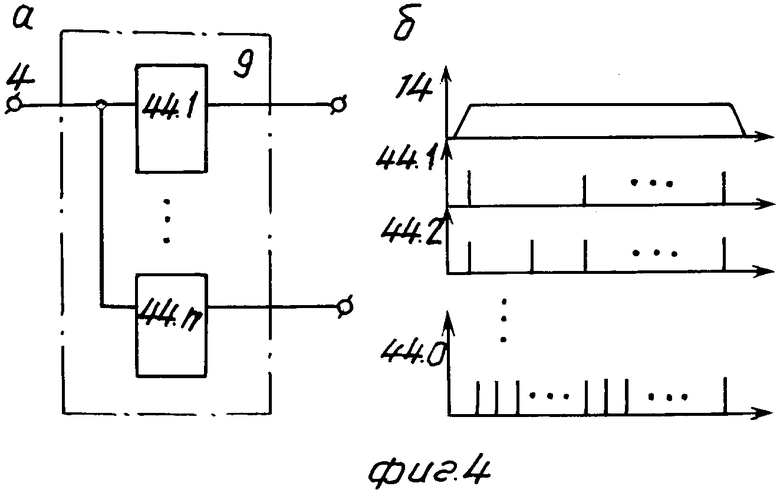

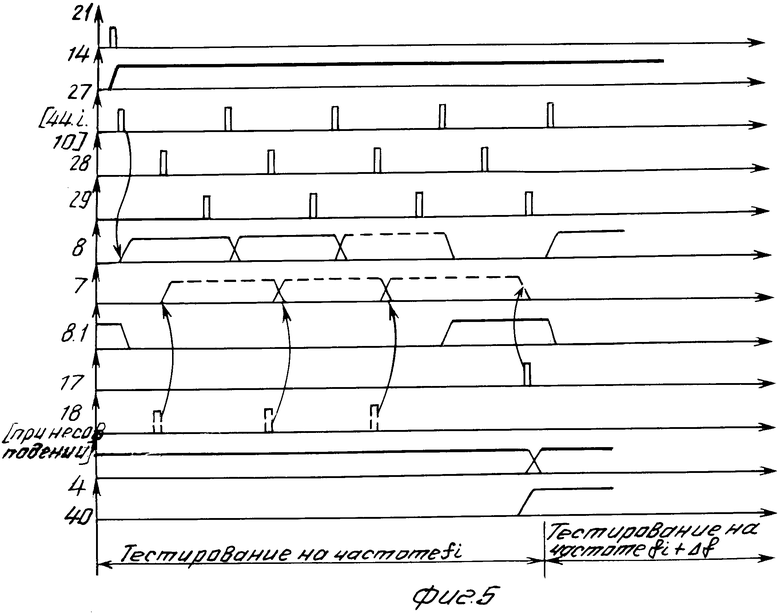

На фиг.1 приведена функциональная схема устройства для программного контроля; на фиг.2 - 4 - функциональные схемы блока задания частоты, делителя частоты, генератора импульсов; временная диаграмма работы устройства приведена на фиг.5.

Устройство для программного контроля (фиг.1) содержит блок 1 памяти тестовых задач с полями начальной частоты 1.1, управления счетом 1.2, циклов 1.3, адреса 1.4 и конца работы 1.5, блоки памяти тестовых программ 2 и несовпадений 3, блок 4 задания частоты, делитель 5 частоты, счетчики адреса 6 и несовпадений 7, регистр 8 с полями конца программы 8.1, теста 8.2, эталона 8.3, немодифицируемых 8.4 и модифицируемых 8.5 разрядов адреса, генератор 9 импульсов, мультиплексор 10, коммутатор 11, первую 12 и вторую 13 схемы сравнения, триггеры пуска 14 и останова 15, формирователь 16 импульсов, первый 17 и второй 18 элементы И, сумматор 19 по модулю два, элемент ИЛИ 20, входы пуска 21, начального адреса 22, синхронизации 23, реакции 24, условий 25 устройства, выход 26 теста устройства, третий 27, первый 28 и второй 29 выходы формирователя 16 импульсов, выходы кода частоты 30, конца работы 31, останова 32 устройства, выход 33 делителя частоты. Объект контроля и диагностирования обозначен символом 34.

Вход 21 пуска устройства соединен с единичным входом триггера 14 пуска, выход которого соединен с входом генератора 9 импульсов, первый 28 и второй 29 выходы формирователя 16 импульсов соединены с первыми входами первого 17 и второго 18 элементов И. Выход счетчика 6 адреса соединен с входом блока 1 памяти тестовых задач, выход 1.3 циклов которого и выход первого элемента И 17 соединены соответственно с информационным и синхронизирующим входами делителя 5 частоты. Выходы генератора 9 импульсов соединены с информационными входами мультиплексора 10, выход которого соединен с входом формирователя 16 импульсов, второй выход которого соединен с входом синхронизации триггера 15 останова, третий выход 27 соединен с входом синхронизации регистра 8 и является выходом синхронизации устройства. Выходы начальной частоты 1.1 и управления счетом 1.2 блока 1 памяти тестовых задач соединены соответственно с информационным и управляющим входами блока 4 задания частоты, выход которого соединен с адресными входами мультиплексора 10, блока 3 памяти несовпадений и выходом 30 кода частоты устройства. Выход 1.4 адреса блока 1 памяти тестовых задач соединен с первым информационным входом коммутатора 11, выход которого соединен с блоком 2 памяти тестовых программ, выход которого соединен с информационным входом регистра 8. Выход 1.5 конца работы блока 1 памяти тестовых задач является выходом 31 конца работы устройства и соединен с первым входом элемента ИЛИ 20, выход которого соединен с нулевым входом триггера 14 пуска. Выход 8.1 конца программы регистра 8 соединен с управляющим входом коммутатора 11, инверсным входом второго элемента И 18 и вторым входом первого элемента И 17, выход которого соединен с входом синхронизации блока 4 задания частоты и установочным входом счетчика 7 несовпадений. Выходы теста 8.2 и эталона 8.3 соединены соответственно с выходом 26 теста устройства и первым входом первой схемы 12 сравнения, второй вход которой является входом 24 реакции устройства, а выход соединен с вторым прямым входом второго элемента И 18. Выход 8.5 модифицируемого разряда регистра 8 и выход 25 условий устройства соединены соответственно с первым и вторым входами сумматора 19 по модулю два, выход которого совместно с выходами немодифицируемых разрядов регистра 8 соединены с вторым информационным входом коммутатора 11. Выход 33 делителя 3 частоты соединен с установочным входом блока 4 задания частоты и счетным входом счетчика 6 адреса, информационный и синхронизирующий входы которого являются входами начального адреса 22 и синхронизации 23 устройства соответственно. Выход второго элемента И 18 соединен со счетным входом счетчика 7 несовпадений, выход которого и выход блока 3 памяти несовпадений соединены с первым и вторым входами второй схемы 13 сравнения соответственно. Выход второй схемы сравнения соединен с единичным входом триггера 15 останова, выход которого соединен с вторым входом элемента ИЛИ 20 и является выходом 32 останова устройства.

Блок 4 задания частоты (фиг.2) содержит формирователь 35, реверсивный счетчик 36, первый 37 и второй 38 элементы И, сумматор 39.

Делитель 5 частоты (фиг. 3) содержит счетчик 40, схему 41 сравнения, элемент 42 задержки, элемент И 43.

Генератор 9 импульсов (фиг.4) содержит группу генераторов 44.1,...44.n.

На фиг.5 использованы обозначения, введенные на фиг.1-4.

Блок 1 памяти предназначен для хранения кодов тестовых задач (ТЗ). Код ТЗ в соответствии с формулой (1) содержит поля НЧТ (поле 1.1), БУС (поле 1.2), ЧЦР (поле 1.3), АТП (поле 1.4) и БКР (поле 1.5). Блок 1 памяти, так же как и блоки 2, 3, представляют собой ПЗУ статического типа, в которых на вход обращения (чтения) может быть постоянно подан разрешающий сигнал нулевого или единичного уровня в зависимости от типа используемой микросхемы.

Блок 2 памяти служит для хранения кодов тестовых команд, образующих тестовые программы. Эти коды фиксируются регистром 8. Код тестовой команды содержит поле 8.1 конца программы, в котором присутствует единичный сигнал в последних командах соответствующей программы, поле 8.2 теста (тестового воздействия, подаваемого на объект), поле 8.3 эталона (эталонной реакции объекта на тестовое воздействие, поле 8.4 немодифицируемых разрядов адреса следующей тестовой команды и поле 8.5 модифицируемого разряда, который может измениться в зависимости от значения логического условия Х (25), формируемого объектом. Исполнительный адрес формируется следующим образом:

a1и=а1(8.4);

аnи=аn(8.4);

aиn+1= а(8.5)⊕ x(25), где аiи - i-й разряд исполнительного адреса, i =  ;

;

ai(8.4), a(8.5) - разряды соответствующих полей.

При необходимости модификации нескольких разрядов адреса поле 8.5, вход 25 и сумматор 19 по модулю два могут быть многоразрядными.

Блок 3 памяти предназначен для преобразования кода частоты тестирования, который является адресным кодом, в код числа допустимых несовпадений (ошибок, сбоев) при выполнении тестовой программы на данной частоте.

Блок 4 задания частоты служит для формирования частоты, на которой осуществляется тестирование. В исходном состоянии счетчик 36 обнулен и выходной код, формируемый сумматором 39, определяется кодом на выходе 1.1

Z4=X1.1+[CT36].

Содержимое счетчика 36 в зависимости от сигнала на входе 1.2 может в процессе поступления импульсов на вход 17 или увеличиваться от кода 0...0 до величины ЧЦТ, или уменьшаться от кода 1...1 до величины 1...1 - ЧЦТ. Обнуление счетчика 36 производится сигналом на входе 33. При изменении сигнала на входе 1.2 с единичного уровня на нулевой формирователь 35 выдает короткий импульс, устанавливающий в счетчике код 1...1.

Делитель 5 частоты построен на основе счетчика 40, который увеличивает содержимое по импульсам на входе 17. Процесс счета продолжается до тех пор, пока в счетчик не запишется код, равный коду на входе 1.3. После этого очередной импульс проходит через элемент И 43, открываемый сигналом с выхода схемы 41 сравнения на выход 33, а с задержкой, определяемой элементом 42, производит обнуление счетчика 40.

Генератор состоит из n генераторов 44, которые формируют импульсные последовательности различной частоты. Включение генераторов производится при наличии единичного сигнала на входе 14.

Счетчик 6 осуществляет выбор очередного адреса по импульсам, поступающим с выхода 33 блока 5. Запись начального адреса производится по входам 22, 23. Счетчик 7 производит подсчет числа несовпадений (ошибок, сбоев) при выполнении тестовой программы в соответствии с импульсами, поступающими с выхода элемента И 18. Обнуление счетчика 7 происходит импульсом с выхода элемента И 17 в конце выполнения тест-программы на определенной частоте.

Регистр 8 осуществляет хранение кодов тестовых команд с выхода блока 2 по импульсам, формируемым на выходе 27 формирователя 16. Мультиплексор 10 предназначен для подключения соответствующего выхода генератора 9 импульсов в соответствии с кодом на выходе блока 4.

Коммутатор 11 управляет передачей адреса с выхода 1.4 или текущего адреса с поля 8.4 и элемента 19 в зависимости от сигнала на выходе 8.1 регистра 8. Схемы 12, 13 служат для сравнения соответствующих кодов. Схема 12 выдает единичный сигнал при несовпадении кодов эталона и реакции объекта, а схема 13 - при превышении содержимого счетчика 7 кода на выходе блока 3 несовпадений. Триггер 14 служит для управления генератором 9, а триггер 15 - для формирования сигнала останова при превышении допустимого числа несовпадений.

Формирователь 16 по сигналу с выхода мультиплексора 10 выдает три сдвинутых по фазе импульса с задержками определяемыми параметрами схемы. Импульс на выходе 27 ( τ1) синфазен импульсу на выходе мультиплексора 10, импульс на выходе 28 (τ2) задерживается на время, определяемое сумматором срабатывания регистра 8, реакции объекта на тест и срабатыванием схемы 12, импульс на выходе 29 (τ3) задерживается по отношению к импульсу τ2 на время срабатывания счетчика 7 и схемы 13. Элемент ИЛИ 20 формирует сигнал выключения триггера 14 при успешном выполнении программы по сигналу с поля 1.5 или при превышении числа допустимых несовпадений.

Устройство работает следующим образом.

В исходном состоянии все элементы памяти обнулены за исключением разряда 8.1 регистра 8. Цепи установки исходного состояния условно не показаны. По импульсу на входе 23 в счетчик 6 заносится начальный адрес тестовой программы, в соответствии с которым на выходы блока 1 памяти формируется код первой тестовой задачи.

Работа устройства начинается по сигналу на входе 21, по которому срабатывает триггер 14 и разблокируется генератор 9 импульсов.

В соответствии с кодом на выходе блока 4, определяемом содержимым поля 1.1, на выход мультиплексора 10 проходит первый импульс последовательности частотой fo. Формирователь 16 по нему выдает три импульса τ1, τ2 и τ3.

По импульсу τ1 в регистр 8 заносится код первой команды программы выполнения первой тестовой задачи (начальный адрес с выхода поля 1.4 через открытый коммутатор был подан на входы блока 2). Код тестового воздействия с выхода поля 8.2 поступает на вход объекта, работа которого может синхронизироваться импульсом τ1. Реакция объекта сравнивается на схеме 12 с эталонным кодом с поля 8.3 и при их несовпадении открывается элемент И 18 (единичный сигнал с выхода 8.1 исчезает по заднему фронту импульса τ1 после записи первой команды в регистр 8). При равенстве указанных кодов элемент И 18 остается открытым. По импульсу τ2производится увеличение содержимого счетчика 7 при несовпадении кодов. В противном случае его содержимое не изменяется. Импульсом τ3 опрашивается выход схемы 13 сравнения. По очередному импульсу τ1 в регистр 8 заносится следующий код и ситуация повторяется.

Работа устройства по описанному алгоритму продолжается до тех пор, пока на выход 8.1 не считывается единичный сигнал конца программы (если ранее не срабатывает триггер 15). По этому сигналу открывается элемент И 17 и импульсом τ3 производится увеличение содержимого счетчика 40 блока 5 и счетчика 36. В результате на выходе блока 4 появляется код последовательности частотой fo+Δ f, по которому к выходу мультиплексора 10 подключается следующий выход генератора 9 (далее в процессе работы при необходимости может уменьшаться содержимое счетчика 36 при нулевом сигнале с поля 1.2). Таким образом, производится повторное выполнение той же тестовой программы, но уже на повышенной частоте.

Работа устройства по выполнению данной тестовой задачи упрощается до тех пор, пока очередной импульс с выхода элемента И 17 произведет обнуление счетчика 36 блока 4 (передним фронтом импульса), продвижение счетчика 6 (задним фронтом импульса) и с задержкой обнуление счетчика 40 блока 5. После этого начинается выполнение следующей тестовой задачи со своими параметрами. Таким образом, работа продолжается до тех пор, пока либо не появится сигнал на выходе поля 1.5 (выходе 31 устройства), свидетельствующий об успешном выполнении программы на всех частотах, либо не зафиксируется останов вследствие срабатывания триггера 15 и появления сигнала на выходе 32. В этом случае фиксируется код частоты на выходе 30, при котором произошел останов, что позволяет определить граничные значения частот устойчивого функционирования устройства.

Оценим технико-экономическую эффективность заявляемого устройства. Технические преимущества по сравнению с прототипом состоят в расширении области применения за счет обеспечения реализации режимов тестирования на разных частотах для различных тестовых задач, а также создания возможности определения критических частот устойчивого функционирования системы при их увеличении или снижении до некоторого фиксируемого порогового значения. Это приводит к созданию положительного эффекта, состоящего, с одной стороны, в увеличении достоверности контроля на величину

δD =  · 100% , где D(fo) - достоверность контроля при реализации тестовых программ на некоторой номинальной частоте fo<fгр (fгр - граничная частота тестирования, предельная в предлагаемом устройстве);

· 100% , где D(fo) - достоверность контроля при реализации тестовых программ на некоторой номинальной частоте fo<fгр (fгр - граничная частота тестирования, предельная в предлагаемом устройстве);

D(fгр) - достоверность контроля при реализации тестовых программ в диапазоне частот от fмин(fo) до fгр; а с другой стороны, в увеличении эксплуатационной производительности объекта (благодаря определению его программного быстродействия) на величину

δП = α  · 100%, где α - коэффициент пропорциональности.

· 100%, где α - коэффициент пропорциональности.

Таким образом, при использовании предлагаемого устройства может быть обеспечено увеличение достоверности контроля (на 25-30%) и производительности (на 5-10%) объекта за счет реализации в нем динамических тестовых режимов.

| название | год | авторы | номер документа |

|---|---|---|---|

| ТРЕХКАНАЛЬНАЯ РЕЗЕРВИРОВАННАЯ СИСТЕМА | 1989 |

|

RU1819116C |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ КАЧЕСТВА МАГНИТНОГО НОСИТЕЛЯ | 1992 |

|

RU2040050C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ДОСТУПОМ К МАГИСТРАЛИ В ЛОКАЛЬНЫХ СЕТЯХ С МАГИСТРАЛЬНОЙ АРХИТЕКТУРОЙ | 1991 |

|

RU2017214C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ДОСТУПОМ К МАГИСТРАЛИ В ЛОКАЛЬНЫХ ВЫЧИСЛИТЕЛЬНЫХ СЕТЯХ С МАГИСТРАЛЬНОЙ АРХИТЕКТУРОЙ | 1991 |

|

RU2012042C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ДОСТУПОМ К МАГИСТРАЛИ В ЛОКАЛЬНЫХ СЕТЯХ С МАГИСТРАЛЬНОЙ АРХИТЕКТУРОЙ | 1991 |

|

RU2017204C1 |

| Устройство для контроля программных автоматов | 1988 |

|

SU1571552A1 |

| РЕЗЕРВИРОВАННОЕ УСТРОЙСТВО | 1991 |

|

RU2015544C1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1142832A1 |

| Устройство для контроля тестопригодных программ | 1990 |

|

SU1751767A1 |

| УСТРОЙСТВО ДЛЯ МАЖОРИТАРНОГО ВЫБОРА СИГНАЛОВ | 1991 |

|

RU2015543C1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах контроля и испытаний сложных программно-аппаратных средств. Целью изобретения является расширение области применения устройства. Цель достигается тем, что в устройство программного контроля, содержащее блок памяти тестовых задач, делитель частоты, счетчик адреса, генератор импульсов, мультиплексор, триггер пуска, формирователь импульсов, первый и второй элементы И, введены блоки памяти тестовых программ и несовпадений, блок задания частоты, счетчик несовпадений, регистр, первая и вторая схемы сравнения, коммутатор, триггер останова, сумматор по модулю два. Сущность изобретения состоит в расширении области применения путем обеспечения возможности реализации тестовых процедур с варьируемыми параметрами. 5 ил.

УСТРОЙСТВО ДЛЯ ПРОГРАММНОГО КОНТРОЛЯ, содержащее блок памяти тестовых задач, делитель частоты, счетчик адреса, генератор импульсов, мультиплексор, триггер пуска, формирователь импульсов, первый и второй элементы И, причем вход пуска устройства соединен с единичным входом триггера пуска, выход которого соединен с входом генератора импульсов, первый и второй выходы формирователя импульсов соединены с первыми входами первого и второго элементов И, выход счетчика адреса соединен с входом блока памяти тестовых задач, выход циклов которого и выход первого элемента И соединены соответственно с информационным и синхронизирующим входами делителя частоты, отличающееся тем, что оно дополнительно содержит блоки памяти тестовых программ и несовпадений, блок задания частоты, счетчик несовпадений, регистр, первую и вторую схемы сравнения, коммутатор, триггер останова, сумматор по модулю два, группа выходов генератора импульсов соединена с группой информационных входов мультиплексора, выход которого соединен с входом формирователя импульсов, первых выходов которого соединен с входом синхронизации триггера останова, третий выход соединен с входом синхронизации регистра и является выходом синхронизации устройства, выходы начальной частоты и управления счетом блока памяти тестовых задач соединены соответственно с информационными и управляющим входами блока задания частоты, выход которого соединен с адресным входом мультиплексора, блока памяти несовпадений и выходом кода частоты устройства, выход адреса блока памяти тестовых задач соединен с первым информационным входом коммутатора, выход которого соединен с адресным входом блока памяти тестовых программ, группа выходов которого соединена с группой информационных входов регистра, выход конца работы блока памяти тестовых задач является выходом конца работы устройства и соединен с первым входом элемента ИЛИ, выход которого соединен с нулевым входом триггера пуска, выход конца программы регистра соединен с управляющим входом коммутатора, с инверсным входом второго элемента И и с вторым входом первого элемента И, выход которого соединен с входом синхронизации блока задания частоты и установочным входом счетчика несовпадений, выходы теста и эталона регистра соединены соответственно с выходом теста устройства и с первым входом первой схемы сравнения, второй вход которой является входом реакции устройства, а выход соединен с вторым прямым входом второго элемента И, выход модифицируемого разряда регистра и вход условий устройства соединены соответственно с первым и вторым входами сумматора по модулю два, выход которого совместно с группой выходов немодифицируемых разрядов регистра соединены с вторым информационным входом коммутатора, выход делителя частоты соединен с установочным входом коммутатора, выход делителя частоты соединен с установочным входом блока задания частоты и счетным входом счетчика адреса, информационный и синхронизирующий входы которого являются входами начального адреса и синхронизации устройства соответственно, выход второго элемента И соединен со счетным входом счетчика несовпадений, выход которого и выход блока памяти несовпадений соединены с первым и вторым входами второй схемы сравнения соответственно, выход второй схемы сравнения соединен с единичным входом триггера останова, выход которого соединен с вторым входом элемента ИЛИ и является выходом останова устройства.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство управления | 1985 |

|

SU1368880A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1994-06-30—Публикация

1991-07-29—Подача