Изобретение относится к микроэлектронике и может быть использовано, например в схемах управления двигателями, аудиоусилителях и измерительной аппаратуре.

Известен класс мощных операционных усилителей (МОУ) в интегральном исполнении фирмы "Burr Brown", например 3571, 3572.

Наиболее близким к предлагаемому изобретению по своей структуре является МОУ ОРА511, содержащий последовательно соединенные входной операционный усилитель, инвертирующий и неинвертирующий входы которого являются соответствующими входами устройства, и выходной двухтактный каскад, первое и второе плечи которого выполнены на составных транзисторах, включенных по схеме с общим коллектором, n-p-n- и p-n-p-структуры соответственно, между базами которых включен блок базового смещения, а в цепях эмиттеров - первый и второй токоограничительные резисторы соответственно, при этом точки соединения первого токоограничительного резистора с эмиттером составного транзистора первого плеча, первого и второго токоограничительных резисторов обоих плеч, второго токоограничительного резистора с эмиттером составного транзистора второго плеча соединены с первым, вторым и третьим входами блока ограничения тока соответственно, при этом выводы питания входного операционного усилителя, блока тепловой защиты, источника опорного тока и коллекторы составных транзисторов выходного двухтактного каскада являются соответствующими шинами питания.

Недостатком данной схемы является отсутствие контроля состояния МОУ и управления его состоянием.

В случае, если в операционном усилителе сработает защита по превышению выходного тока либо тепловая защита, то для определения вида срабатывания защиты, а следовательно, и возможной неисправности нагрузки, необходимо исследовать состояние выхода МОУ.

Кроме того, при необходимости управления состоянием МОУ, например его аварийного отключения, это возможно только снятием напряжения питания.

Целью изобретения является повышение надежности защиты за счет обеспечения контроля состояния устройства.

Это достигается тем, что в мощный операционный усилитель, содержащий последовательно соединенные входной операционный усилитель, инвертирующий и неинвертирующий входы которого являются соответствующими входами устройства, и выходной двухтактный каскад, первое и второе плечи которого выполнены на составных транзисторах, включенных по схеме с общим коллектором, n-p-n- и p-n-p-структуры соответственно, между базами которых включен блок базового смещения, а в цепях эмиттеров - первый и второй токоограничительные резисторы соответственно, при этом точки соединения первого токоограничительного резистора с эмиттером составного транзистора первого плеча, первого и второго токоограничительных резисторов обоих плеч, второго токоограничительного резистора с эмиттером составного транзистора второго плеча соединены с первым, вторым и третьим входами блока ограничения тока соответственно, при этом выводы питания входного операционного усилителя, блока тепловой защиты, источника опорного тока и коллекторы составных транзисторов выходного двухтактного каскада являются соответствующими шинами питания, введены первый, второй и третий двухколлекторные p-n-p-транзисторы, первый, второй резисторы и стабилитрон, при этом эмиттер первого двухколлекторного транзистора соединен с базой составного транзистора первого плеча, база - с первым коллектором этого транзистора и подключена к четвертому входу блока ограничения тока, эмиттер второго двухколлекторного транзистора соединен с пятым входом блока ограничения тока, база - с первым коллектором этого транзистора и с базой составного транзистора второго плеча, а вторые коллекторы первого и второго двухколлекторных транзисторов объединены и подключены к входу отражателя тока, выполненного на первом и втором транзисторах n-p-n-структуры, выход которого соединен с базой и первым коллектором третьего двухколлекторного транзистора, второй коллектор которого соединен с эмиттером третьего транзистора n-p-n-структуры и является контрольным выходом и соединен с коллектором четвертого транзистора n-p-n-cтруктуры, эмиттер которого соединен с соответствующей шиной питания, а база - с входом блока тепловой защиты, коллектор третьего транзистора n-p-n-cтруктуры соединен с входом источника опорного тока, между его базой и эмиттером третьего двухколлекторного транзистора включен первый резистор, эмиттер пятого транзистора n-p-n-структуры соединен с эмиттером третьего двухколлекторного транзистора и через резистивный делитель, отвод которого подключен к эмиттеру третьего транзистора, с соответствующей шиной питания, коллектор с соответствующей шиной питания и через последовательно соединенные второй резистор и стабилитрон - с соответствующей шиной питания, при этом точка соединения второго резистора и стабилитрона подключена к базе пятого транзистора n-p-n-структуры.

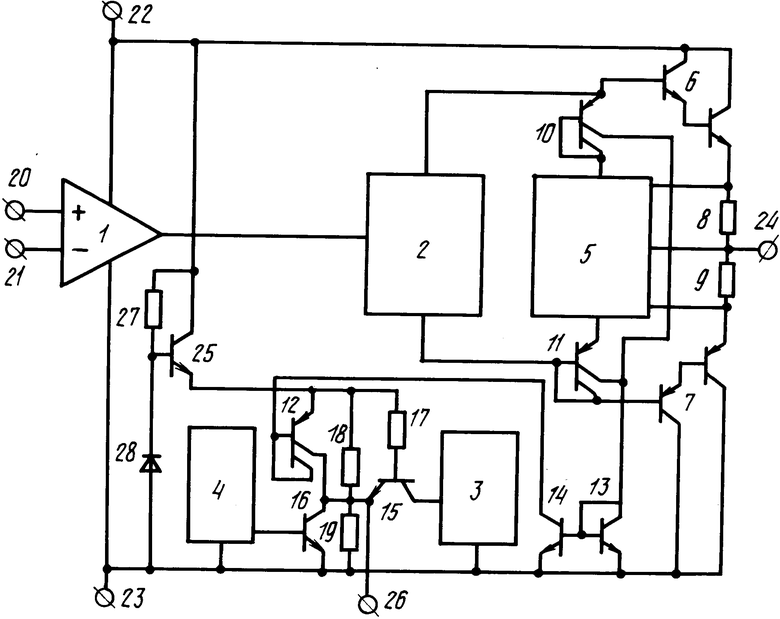

На чертеже приведена схема мощного операционного усилителя.

Он содержит входной операционный усилитель 1, выходной двухтактный каскад, выполненный на составных транзисторах 6 и 7, включенных по схеме с общим коллектором, n-p-n- и p-n-p-структуры соответственно и токоограничительных резисторах 8 и 9, блок базового смещения 2, источник опорного тока 3, блок тепловой защиты 4, блок огpаничения тока 5, первый 10, второй 11, третий 12 двухколлекторные p-n-p-транзисторы, первый 13, второй 14, третий 15, четвертый 16 и пятый 25 n-p-n-транзисторы, первый 17 и второй 27 резисторы и стабилитрон 28, при этом эмиттер первого двухколлекторного транзистора 10 соединен с базой составного транзистора 6, база - с первым коллектором этого транзистора и подключена к четвертому входу блока ограничения тока 5, эмиттер второго двухколлекторного транзистора 11 соединен с пятым входом блока ограничения тока 5, база - с первым коллектором этого транзистора и с базой составного транзистора 7.

Вторые коллекторы первого 10 и второго 11 двухколлекторных транзисторов объединены и подключены к входу отражателя тока, выполненного на первом 13 и втором 14 транзисторах n-p-n-структуры, выход которого соединен с базой и первым коллектором третьего двухколлекторного транзистора 12, второй коллектор которого соединен с эмиттером третьего транзистора 15 n-p-n-структуры и является контрольным выходом и соединен с коллектором четвертого транзистора 16 n-p-n-структуры, эмиттер которого соединен с соответствующей шиной питания, а база - с входом блока тепловой защиты 4.

Коллектор третьего транзистора 15 соединен с входом источника опорного тока 3, между его базой и эмиттером третьего двухколлекторного транзистора 12 включен первый резистор 17, эмиттер пятого транзистора 25 n-p-n-структуры соединен с эмиттером третьего двухколлекторного транзистора 12 и через резистивный делитель 18 и 19, отвод которого подключен к эмиттеру третьего транзистора 15, с соответствующей шиной питания, коллектор с соответствующей шиной питания и через последовательно соединенные второй резистор 27 и стабилитрон 28 - с соответствующей шиной питания, при этом точка соединения второго резистора 27 и стабилитрона 28 подключена к базе пятого транзистора n-p-n-структуры.

Мощный операционный усилитель работает следующим образом.

При подаче напряжения питания на эмиттере транзистора 25 устанавливается опорное напряжение ≈ 5В.

Uоп = Uст - Uбэ, где Uст - напряжение на стабилитроне 28;

Uбэ - напряжение на база-эмиттерном переходе открытого транзистора 25.

Транзисторы 12 и 16 закрыты, резисторы 18 и 19, равные по величине, устанавливают на контрольном выходе напряжение ≈2,5В.

Uвых=  Uоп

Uоп

Источник опорного тока 3 задает ток при напряжении на его входе, равном

Uпор=2Uбэ ≈ 1,4В, где Uбэ - напряжение на база-эмиттерном переходе открытого транзистора.

При напряжении на контрольном выходе

Uвых ≥ Uпор-Uкэ, где Uкэ - напряжение между коллектором и эмиттером открытого транзистора 15, транзистор 15 находится в инверсном режиме, а источник опорного тока 3 включен и запитывает током все каскады МОУ. Резистор 17 определяет величину тока Iоп, которым запитывается источник опорного тока

R17=  , где Uбк - напряжение на база-коллекторном переходе транзистора 15;

, где Uбк - напряжение на база-коллекторном переходе транзистора 15;

Iоп - опорный ток для источника опорного тока 3.

Напряжение на контрольном выходе, равное половине Uоп, указывает на то, что МОУ находится в нормальном рабочем состоянии. В этом состоянии дифференциальный сигнал, подаваемый на входы 20 и 21 МОУ, выделяется и усиливается входным операционным усилителем 1 и поступает на блок базового смещения 2, который в зависимости от знака дифференциального сигнала открывает либо верхний составной транзистор 6, либо нижний составной транзистор 7. Через составной транзистор и токоограничительный резистор (8 или 9 соответственно) начинает протекать ток нагрузки. Если ток нагрузки достигает граничного значения, определяемого токоограничивающим резистором, на последнем выделяется напряжение, которое вызывает срабатывание блока ограничения тока 5. Транзистор 10 или 11, если открыт нижний составной транзистор 7 открывается. Ток смещения Iсм, задаваемый блоком базового смещения и поступающий в базу составного транзистора, ответвляется через транзистор 10 (или 11 соответственно) в блок ограничения тока, ток базы составного транзистора уменьшается и он постепенно закрывается. Схема ограничения тока будет отбирать базовый ток составного транзистора до тех пор, пока ток нагрузки не уменьшится до граничного значения. При этом

Iсм=Iк1т10+Iк2т10+Iбт6, где Iбт6 - ток базы составного транзистора 6;

Iк1т10 - ток пеpвого коллектора транзистора 10;

Iк2т10 - ток второго коллектора транзистора 10.

Ток первого коллектора транзистора 10 втекает в блок ограничения тока 5, а второго коллектора отражается токовым зеркалом на транзисторах 13 и 14 и открывает p-n-p-транзистор 12. В результате на контрольном выходе устанавливается напряжение

Uвых= Uоп-Uкэт12, где Uкэт12 - напряжение между коллектором и эмиттером транзистора 12.

Учитывая, что Uкэ транзистора 12 в насыщенном состоянии мало, Uвых ≈ Uоп, т. е. при превышении тока нагрузки на контрольном выходе формируется напряжение ≈Uоп. Как только ток нагрузки входит в допустимые границы, транзистор 10, а следовательно, и транзистор 12 закрываются и на контрольном выходе восстанавливается исходное напряжение.

Если срабатывает блок тепловой защиты 4, транзистор 16 открывается и на контрольном выходе устанавливается напряжение

Uвых=Uкэнас.т16 ≈ ОВ, где Uкэнас.т16 - напряжение между коллектором и эмиттером транзистора Т16 в насыщенном состоянии.

Переход база-эмиттер транзистора 15 открывается, на входе схемы источника опорного тока 3 устанавливается напряжение Uвх<Uпор., источник опорного тока отключается, а следовательно, отключается и весь МОУ.

Если срабатывает и блок тепловой защиты 4, и блок ограничения тока 5, то на контрольном выходе устанавливается напряжение Uкэнас.т16, близкое к ОВ. Ток коллектора транзистора 12 не может превышать половины тока смещения Iсм, которое является постоянной величиной и задается источником опорного тока.

Таким образом, напряжение на контрольном выходе однозначно указывает на состояние МОУ (нормальная работа ≈  Uоп , перегрев ≈ ОВ, ограничение по току нагрузки ≈Uоп).

Uоп , перегрев ≈ ОВ, ограничение по току нагрузки ≈Uоп).

При необходимости управления состоянием МОУ, например при его аварийном отключении, на контрольный выход 26 подается сигнал низкого уровня (меньше ≃ 0,7В). При этом открывается база-эмиттерный переход транзистора 15 и, следовательно, отключается источник опорного тока, МОУ отключается в третье состояние. Таким образом можно управлять состоянием МОУ.

Примером конкретного выполнения изобретения является МОУ в интегральном исполнении, разработанный по НИР "Миф-1".

Технико-экономические преимущества изобретения по сравнению с прототипом заключаются в расширении функциональных возможностей, а следовательно, области применения, и повышении надежности аппаратуры, в которой будет применяться данный МОУ.

| название | год | авторы | номер документа |

|---|---|---|---|

| МОЩНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 1991 |

|

RU2092969C1 |

| ЭЛЕКТРОННОЕ РЕЛЕ С ТРАНСФОРМАТОРНОЙ РАЗВЯЗКОЙ И С ЗАЩИТОЙ ОТ ПЕРЕГРУЗКИ ПО ТОКУ И ПЕРЕГРЕВА ЭЛЕКТРОННОГО КЛЮЧА | 2008 |

|

RU2380828C1 |

| УСТРОЙСТВО ДЛЯ РЕЗЕРВНОГО ЭЛЕКТРОСНАБЖЕНИЯ | 2011 |

|

RU2446541C1 |

| ДВУХТАКТНЫЙ УСИЛИТЕЛЬ МОЩНОСТИ | 2004 |

|

RU2274947C2 |

| ЭЛЕКТРОННОЕ РЕЛЕ С ТРАНСФОРМАТОРНОЙ РАЗВЯЗКОЙ И С ЗАЩИТОЙ ОТ ПЕРЕГРУЗКИ ПО ТОКУ | 2008 |

|

RU2360358C1 |

| УСТРОЙСТВО ДЛЯ ТОКОВОЙ ЗАЩИТЫ СЕТИ ПЕРЕМЕННОГО ТОКА | 1997 |

|

RU2136096C1 |

| УСТРОЙСТВО РЕЗЕРВНОГО ЭЛЕКТРОПИТАНИЯ | 2011 |

|

RU2474028C1 |

| Способ построения стабилизатора постоянного напряжения | 2021 |

|

RU2775059C1 |

| УСТРОЙСТВО ДЛЯ БЕСПЕРЕБОЙНОГО ПИТАНИЯ | 2010 |

|

RU2446540C1 |

| Стабилизатор напряжения | 2023 |

|

RU2795284C1 |

Использование: в схемах управления двигателями, аудиоусилителях и в измерительной аппаратуре. Сущность изобретения: устройство содержит последовательно соединенные операционный усилитель и выходной двухтактный каскад, а также блок базового смещения, блок тепловой защиты, источник опорного тока, блок ограничения тока и отражатель тока. Инвертирующий и неинвертирующий входы операционного усилителя являются входами устройства. Первое и второе плечи выходного двухтактного каскада выполнены на составных транзисторах, включенных по схеме с общим коллектором. В цепях эмиттеров составных транзисторов включены токоограничительные резисторы. Эмиттер первого двухколлекторного p - n - p-транзистора соединен с блоком базового смещения и с базой составного транзистора первого плеча. База первого двухколлекторного p - n - p-транзистора соединена с первым коллектором этого же транзистора и подключена к соответствующему входу блока ограничения тока. К другому его входу подключен эмиттер второго двухколлекторного p - n - p-транзистора. База второго двухколлекторного p - n - p-транзистора соединена с первым коллектором этого же транзистора и с базой составного транзистора второго плеча. Вторые коллекторы первого и второго двухколлекторных p - n - p-транзисторов объединены и подключены к входу отражателя тока, соединенного с базой и одним коллектором третьего двухколлекторного p - n - p-транзистора. В устройстве имеются также пять n - p - n-транзисторов, подключенных к блоку тепловой защиты, резистивному делителю мощности, к источнику опорного тока и к стабилитрону. 1 ил.

МОЩНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ, содержащий последовательно соединенные входной операционный усилитель, инвертирующий и неинвертирующий входы которого являются соответствующими входами устройства, и выходной двухтактовый каскад, первое и второе плечи которого выполнены на составных транзисторах, включенных по схеме с общим коллектором, n-p-n-и p-n-p-структуры соответственно, между базами которых включен блок базового смешения, а в цепях эмиттеров - первый и второй токоограничительные резисторы соответственно, при этом точки соединения первого токоограничительного резистора с эмиттером составного транзистора первого плеча, первого и второго токоограничительных резисторов обоих плеч, второго токоограничительного резистора с эмиттером составного транзистора второго плеча соединены с первым, вторым и третьим входами блока ограничения тока соответственно, при этом выводы питания входного операционного усилителя, блока тепловой защиты, источника опорного тока и коллекторы составных транзисторов выходного двухтактного каскада являются соответствующими шинами питания, отличающийся тем, что, с целью повышения надежности защиты за счет обеспечения контроля состояния устройства, введены первый, второй и третий двухколлекторные p-n-p-транзисторы, первый, второй, третий, четвертый и пятый n-p-n-транзисторы, первый, второй резисторы и стабилитрон, при этом эмиттер первого двухколлекторного транзистора соединен с базой составного транзистора первого плеча, база - с первым коллектором этого транзистора и подключена к четвертому входу блока ограничения тока, эмиттер второго двухколлекторного транзистора соединен с пятым входом блока ограничения тока, база - с первым коллектором этого транзистора и с базой составного транзистора второго плеча, а вторые коллекторы первого и второго двухколлекторных транзисторов объединены и подключены к входу отражателя тока, выполненного на первом и втором транзисторах n-p-n-структуры, выход которого соединен с базой и первым коллектором третьего двухколлекторного транзистора, второй коллектор которого соединен с эмиттером третьего транзистора n-p-n-структуры и является контрольным выходом и соединен с коллектором четвертого транзистора n-p-n-структуры, эмиттер которого соединен с соответствующей шиной питания, а база - с входом блока тепловой защиты, коллектор третьего транзистора n-p-n-структуры соединен с входом источника опорного тока, между его базой и эмиттером третьего двухколлекторного транзистора включен первый резистор, эмиттер пятого транзистора n-p-n-структуры соединен с эмиттером третьего двухколлекторного транзистора и через резистивный делитель, отвод которого подключен к эмиттеру третьего транзистора, с соответствующей шиной питания, коллектор с соответствующей шиной питания и через последовательно соединенные второй резистор и стабилитрон - с соответствующей шиной питания, при этом точка соединения второго резистора и стабилитрона подключена к базе пятого транзистора n-p-n-структуры.

| Способ сопряжения брусьев в срубах | 1921 |

|

SU33A1 |

Авторы

Даты

1994-07-30—Публикация

1991-05-27—Подача