Изобретение относится к микроэлектронике и может быть использовано, например, в схемах управления двигателями, аудиоусилителями и измерительной технике.

Известен класс МОУ в интегральном исполнении фирмы Burr Brown [1] а также усилитель со схемой защиты [2]

Наиболее близким к изобретению является мощный операционный усилитель [3] содержащий входной каскад, неинвертирующий и инвертирующий входы которого являются соответствующими входами мощного операционного усилителя, выводы питания входного каскада подключены соответственно к положительной и отрицательной шинам питания, а выход соединен с входом цепи смещения, включенной между базами n-p-n и p-n-p транзисторов, выполненных по схеме Дарлингтона, выходного двухтактного каскада, коллекторы n-p-n и p-n-p транзисторов выходного двухтактного каскада соединены соответственно с положительной и отрицательной шинами питания, а эмиттеры соединены с первыми выводами первого и второго резисторов и через первый и второй токоограничительные резисторы соединены с общим выходом ограничителя тока, включенного между базами n-p-n и p-n-p транзисторов выходного двухтактного каскада, при этом точка соединения первого и второго токоограничительных резисторов является выходом мощного операционного усилителя.

Недостатком известных решений является или отсутствие ограничения выходного тока или входным сигналом для схемы ограничения тока является разность напряжения между коллектором и эмиттером выходного транзистора (поделенная на резистивном делителе), и ток ограничения выходного транзистора зависит от напряжения между его коллектором и эмиттером [2]

В предлагаемом устройстве на вход схемы ограничения подается ток с управляемого генератора, и ток ограничения выходного транзистора зависит от внешнего тока, подаваемого на управляемый генератор тока.

Техническая суть предлагаемого устройства заключается в возможности динамического управления током ограничения выходного транзистора в зависимости от внешних условий. Это особенно важно для МОУ для предохранения от выхода из области безопасной работы, которая определяется тепловым сопротивлением кристалл-среда и допустимым перегревом. Тепловое сопротивление определяется условиями внешней среды, характеристиками теплоотвода, конструкцией корпуса, электрическими характеристиками источников сигнала и конструктивно-топологическими решениями МОУ. Мощность, рассеиваемая МОУ, зависит также от режима его работы (усиление постоянного сигнала, импульсного, гармонического и т.д. ). Все эти факторы делают неудобным выбор фиксированной зависимости тока ограничения. Введение входа управления током нагрузки (т.е. током ограничения выходного транзистора) позволяет устанавливать предельный ток с учетом конкретных условий и режимов МОУ, тем самым повышая его надежность и расширяя его функциональные возможности.

Мощный операционный усилитель, отличающийся тем, что введены первый, второй, третий и четвертый p-n-p транзисторы, первый, второй, третий и четвертый n-p-n транзисторы, первый, второй и третий диоды, стабилитрон и с третьего по одиннадцатый резисторы, причем базы первого, второго и третьего p-n-p транзисторов соединены с коллектором первого p-n-p транзистора, эмиттеры первого, второго и третьего p-n-p транзисторов соответственно через третий, четвертый и пятый резисторы соединены с положительной шиной питания, коллектор второго p-n-p транзистора соединен с базой первого n-p-n транзистора и с коллектором и базой второго n-p-n транзистора, эмиттеры первого и второго n-p-n транзисторов соответственно через шестой и седьмой резисторы подключены к отрицательной шине питания, при этом коллектор третьего p-n-p транзистора соединен с первым управляющим входом ограничителя тока и со вторым выводом первого резистора, коллектор первого n-p-n транзистора соединен со вторым управляющим входом ограничителя тока и со вторым выводом второго резистора, причем база четвертого p-n-p транзистора является входом управления током нагрузки мощного операционного усилителя и через восьмой резистор соединена с отрицательной шиной питания и коллектором четвертого p-n-p транзистора, эмиттер которого через девятый резистор подключен к эмиттеру третьего n-p-n транзистора, коллектор которого соединен с коллектором первого p-n-p транзистора, база через последовательно соединенные в прямом включении первый, второй и третий диоды подключена к отрицательной шине питания, а через десятый резистор к эмиттеру четвертого n-p-n транзистора, база которого через одиннадцатый резистор соединена с положительной шиной питания и коллектором четвертого n-p-n транзистора, а через стабилитрон с отрицательной шиной питания.

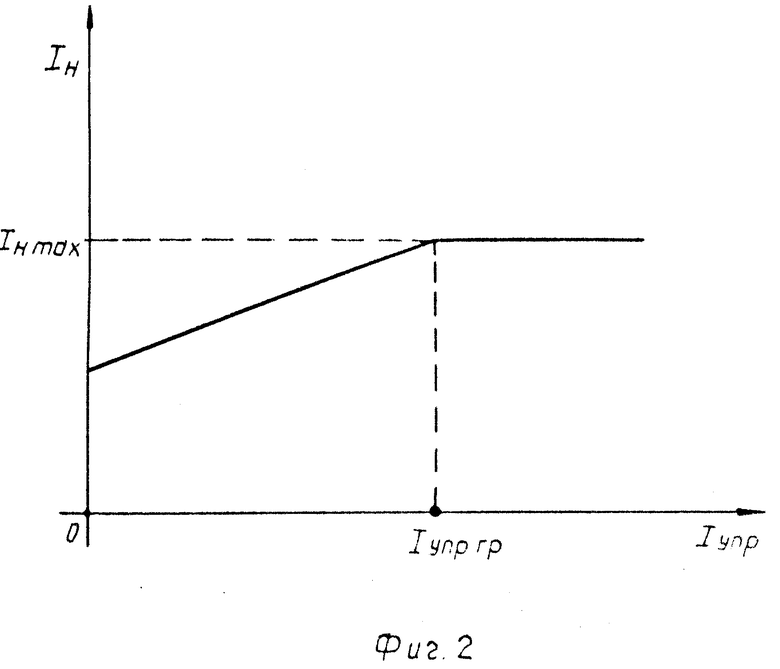

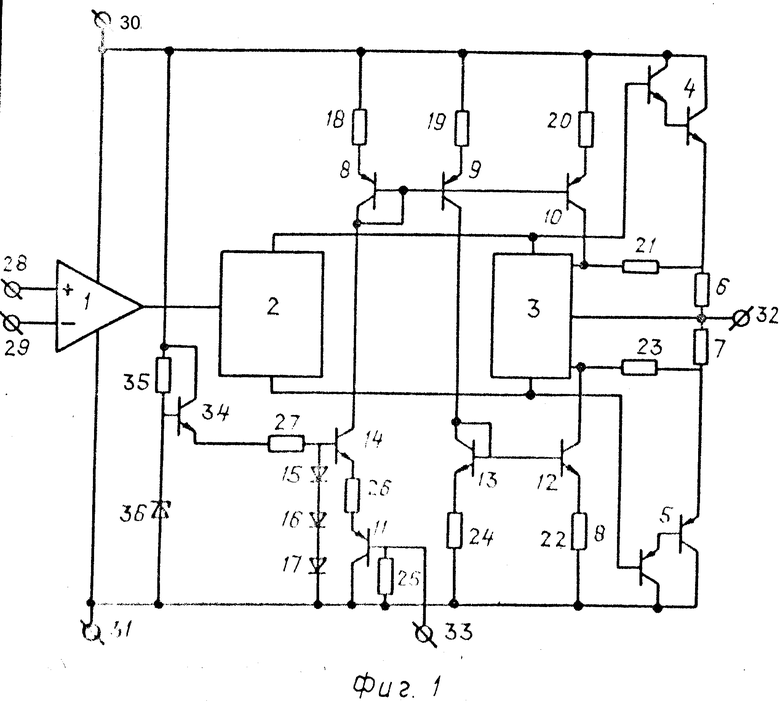

На фиг. 1 приведена схема МОУ; на фиг. 2 график зависимости тока нагрузки от управляющего тока.

МОУ содержит входной каскад 1, цепь смещения 2, ограничитель тока 3, выходной двухтактный каскад, содержащий n-p-n и p-n-p транзисторы 4 и 5, выполненные по схеме Дарлингтона, токоограничительные резисторы 6 и 7, p-n-p транзисторы 8, 9, 10 и 11, n-p-n транзисторы 12, 13 и 14, диоды 15, 16 и 17 и резисторы с 18 по 27, причем неинвертирующий и инвертирующий входы входного каскада 1 являются соответствующими входами МОУ 28 и 29, выводы питания входного каскада 1 подключены соответственно к положительной и отрицательной шинам питания 30 и 31, а выход соединен с входом цепи смещения 2, включенной между базами транзисторов 4 и 5, коллекторы которых соединены соответственно с шинами питания 30 и 31, а эмиттеры соединены с первыми выводами резисторов 21 и 23 и через резисторы 6 и 7 соединены с общим выходом ограничителя тока 3, включенного между базами транзисторов 4 и 5, при этом точка соединения резисторов 6 и 7 является выходом МОУ 32, базы транзисторов 8, 9 и 10 соединены с коллектором транзистора 8, эмиттеры транзисторов 8, 9 и 10 соответственно через резисторы 18, 19 и 20 соединены с шиной питания 30, коллектор транзистора 9 соединен с базой транзистора 12 и с коллектором и базой транзистора 13, эмиттеры транзисторов 12 и 13 соответственно через резисторы 22 и 24 подключены к шине питания 31, при этом коллектор транзистора 10 соединен с первым управляющим входом ограничителя тока 3 и со вторым выводом резистора 21, коллектор транзистора 12 соединен со вторым управляющим входом ограничителя тока 3 и со вторым выводом резистора 23, причем база транзистора 11 является входом управления током нагрузки МОУ 33 и через резистор 25 соединена с шиной питания 31 и коллектором транзистора 11, эмиттер которого через резистор 26 подключен к эмиттеру транзистора 14, коллектор которого соединен с коллектором транзистора 8, база через последовательно соединенные в прямом включении диоды 15, 16 и 17 подключена к шине питания 31, а через резистор 27 к эмиттеру транзистора 34, база которого через резистор 35 соединена с шиной питания 30 и коллектором транзистора 34, а через стабилитрон 36 с шиной питания 31.

МОУ работает следующим образом.

Входной каскад 1 выделяет и усиливает дифференциальный сигнал между входами МОУ 28 и 29. Этот сигнал поступает на вход цепи смещения, которая в зависимости от знака сигнала открывает либо транзистор 4 (положительный дифференциальный сигнал), либо транзистор 5 (отрицательный дифференциальный сигнал) выходного двухтактного каскада. Ток нагрузки протекает через транзистор (4 или 5) и токоограничительный резистор (6 или 7).

На транзисторах 11, 14, диодах 15, 16 и 17 и резисторах 25, 26 собран генератор тока. При поданном питании и управляющем токе Iупр=0, поданном на вход управления током нагрузки МОУ 33, генератор вырабатывает максимальный ток, так как на эмиттере транзистора 34 устанавливается напряжение

U Uст Uбэт34,

где Uст напряжение стабилитрона 36;

Uбэт34 напряжение на базо-эмиттерном переходе открытого транзистора 34.

Через резистор 27 и диоды 15, 16 и 17 протекает ток, и на базе транзистора 14 стабилизируется напряжение, равное 3Uд, где Uд - напряжение на прямосмещенном диоде.

При Iупр 0 по протекает только ток базы транзистора 11, и на резисторе 25 падает напряжение

UR25 R25•Iбт11,

где Iбт11 ток базы транзистора 11.

Если управляющий ток отличен от нуля, то на резисторе 25 дополнительно падает напряжение

U Iупр•R25.

Током генератора является ток коллектора транзистора 14, приблизительно равный току через резистор 26, который определяется

IR26 (3Uд Uбэт14 Uбэт11 (Iбт11 + Iупр)•R25)/R26,

где Uбэт14, Uбэт11 напряжение на базо-эмиттерных переходах транзисторов 14 и 11 соответственно.

Ток базы транзистора 11 определяется

Iбт11 Iэт11 /b Ir26/ b,

где b коэффициент усиления транзистора 11 по постоянному току. Таким образом, уравнение для тока генератора запишется следующим образом:

IR26 (Uд (IR26/b + Iупр)•R25)/R26 Uд/R26 - (IR26•R25)/(b•R26) Iупр•R25/R26 (Uд - Iупр•R25)/(R26 R25/b).

При в > 1

IR26 (Uд Iупр•R25)/R26.

Ток коллектора транзистора 10 I2 является отражением тока коллектора транзистора 8 I1 от токового зеркала на транзисторах 8, 10 и резисторах 18, 20, а ток коллектора транзистора 12 I3 отражением тока I1 от токового зеркала на транзисторах 13, 12 и резисторах 24, 22.

I2 I1•R20/R18;

I3 I1•R19•R22/(R18•R24).

Для симметричности верхнего и нижнего каскадов

R22 R24 и R20 R18,

тогда I2 I3 + I1•R20/R18 ((Uд - Iупр•R25)/R26)•R20/R18.

Ограничитель тока 3 отслеживает напряжение между его общим выходом и первым управляющим входом, если открыт транзистор 4, или общим выходом и вторым управляющим входом, если открыт транзистор 5. Если отслеживаемое напряжение превышает пороговое значение Uпор, то ограничитель тока 3 начинает отбирать базовый ток открытого транзистора выходного каскада, транзистор подзакрывается, а следовательно, уменьшается ток нагрузки, протекающий через токоограничительный резистор (6 или 7). Напряжение на токоограничительном резисторе уменьшается до тех пор, пока на управляющем входе ограничителя тока 3 не установится пороговое напряжение Uпор.

Если ток коллектора транзистора 10 I2, протекающий через резистор 21, равен нулю, то все напряжение на токоограничительном резисторе 6 прикладывается между общим выходом и первым управляющим входом ограничителя 3, и ток нагрузки ограничивается только токоограничительным резистором 6. Иначе ток 12 создает на резисторе 21 дополнительное падение напряжения, что дополнительно ограничивает ток нагрузки:

Iнаг (Uпор I2•R21)/R6 Uпор/R6 - I1•R20•R21/(R18•R6) Uпор/R6 (Uд - Iупр•R25)/R26•R20•R21/(R18•R6) (Uпор - Uд•R20/R18•R21/R26)/R26 - Iупр•R25/R26•R20/R18•R21/R6.

Таким образом, ток нагрузки пропорционален току управления (фиг. 2).

При Iупр Uд/R25 ток нагрузки максимальный и определяется токоограничительным резистором, при Iупр 0

Iнаг Uпор/R6 Uд•R20•R21/R18/R26/R26

и при Uпор Uд•R20/R18•R21/R26

Iнаг 0.

Таким образом, вход управления током нагрузки позволяет устанавливать предельный нагрузочный ток с учетом конкретных условий и режимов МОУ.

| название | год | авторы | номер документа |

|---|---|---|---|

| МОЩНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 1991 |

|

RU2017322C1 |

| ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ | 1992 |

|

RU2036510C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ТИРИСТОРНЫМ КЛЮЧОМ | 1990 |

|

RU2007859C1 |

| СТАБИЛИЗАТОР ПОСТОЯННОГО ТОКА | 1991 |

|

RU2024916C1 |

| Операционный усилитель | 1989 |

|

SU1721614A1 |

| БАКТЕРИЦИДНАЯ СИСТЕМА ДЛЯ ОБРАБОТКИ ВОДЫ | 1994 |

|

RU2072967C1 |

| СТАБИЛИЗИРОВАННЫЙ ПРЕОБРАЗОВАТЕЛЬ ПОСТОЯННОГО НАПРЯЖЕНИЯ С ЗАЩИТОЙ | 1991 |

|

RU2024171C1 |

| Усилитель мощности | 2023 |

|

RU2796545C1 |

| ДВУХТАКТНЫЙ УСИЛИТЕЛЬ МОЩНОСТИ | 2004 |

|

RU2274947C2 |

| БИПОЛЯРНО-ПОЛЕВОЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ "ПЕРЕГНУТОГО" КАСКОДА | 2015 |

|

RU2592429C1 |

Использование: в микроэлектронике, а именно в схемах управления двигателями, аудиоусилителях и измерительной технике. Сущность изобретения: повышение надежности достигается тем, что в мощный операционный усилитель, состоящий из входного каскада 1, цепи 2 смещения, ограничителя 3 тока, выходного двухтактного каскада на n-p-n и p-n-p транзисторах, включенных по схеме Дарлингтона соответственно, первого и второго токоограничительных резисторов 6 и 7 введены первый, второй и третий, четвертый p-n-p транзисторы 8, 9, 10, 11 и первый, второй и третий n-p-n транзисторы 12, 13 и 14, первый, второй и третий диоды 15, 16, 17 и с третьего по одиннадцатый резисторы 18-27. 2 ил.

Мощный операционный усилитель, содержащий входной каскад, инвертирующий и неинвертирующий входы которого являются соответствующими входами мощного операционного усилителя, выводы питания входного каскада подключены соответственно к положительной и отрицательной шинам питания, а выход соединен с входом цепи смещения, включенной между базами n p n- и p n - p-транзисторов, выполненных по схеме Дарлингтона, выходного двухтактного каскада, коллекторы n p n- и p n p-транзисторов выходного двухтактного каскада соединены соответственно с положительной и отрицательной шинами питания, а эмиттеры соединены с первыми выводами первого и второго резисторов и через первый и второй токоограничительные резисторы соединены с общим выходом ограничителя тока, включенного между базами p n p- и n p - n-транзисторов выходного двухтактного каскада, при этом точка соединения первого и второго токоограничительных резисторов является выходом мощного операционного усилителя, отличающийся тем, что введены первый, второй, третий, четвертый p n p-транзисторы, первый, второй, третий и четвертый n p - n-транзисторы, первый, второй, третий диоды, стабилитрон и с третьего по одиннадцатый резисторы, причем базы первого, второго и третьего p n - p-транзисторов соединены с коллектором первого p n p-транзистора, эмиттеры первого, второго и третьего p n p-транзисторов соответственно через третий, четвертый и пятый резисторы соединены с положительной шиной питания, коллектор второго p n p-транзистора соединен с коллектором и базой второго n p n-транзистора, эмиттеры первого и второго n p n-транзисторов соответственно через шестой и седьмой резисторы подключены к отрицательной шине питания, при этом коллектор третьего n p n-транзистора соединен с первым управляющим входом ограничителя тока и вторым выводом первого резистора, коллектор второго n p n-транзистора соединен с вторым управляющим входом ограничителя тока и вторым выводом второго резистора, причем база четвертого p n р-транзистора является входом управления током нагрузки мощного операционного усилителя и через восьмой резистор соединена с отрицательной шиной питания и коллектором четвертого p n p-транзистора, эмиттер которого через девятый резистор подключен к эмиттеру третьего n p - n-транзистора, коллектор которого соединен с коллектором первого p n - p-транзистора, база через последовательно соединенные в прямом включении первый, второй, третий диоды подключена к отрицательной шине питания, а через десятый резистор к эмиттеру четвертого n p n-транзистора, база которого через стабилитрон соединена с отрицательной шиной питания, а через одиннадцатый резистор с положительной шиной питания и коллектором четвертого n p n-транзистора.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Каталог Burr Brown IC Data Book, v | |||

| Способ сопряжения брусьев в срубах | 1921 |

|

SU33A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Патент США N 4258406, кл | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Каталог Burr Brown IC Data Book, v | |||

| Способ сопряжения брусьев в срубах | 1921 |

|

SU33A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1997-10-10—Публикация

1991-07-12—Подача