Изобретение относится к импульсной и дискретной вычислительной технике и может быть использовано при построении в процессорах ЦВМ формирователей импульсов продвижения интервального таймера с периодичностью 1/300 с.

Известен синхронный делитель частоты с коэффициентом деления 13, содержащий пять счетных триггеров. Недостатком указанного делителя частоты являются большие аппаратные затраты, связанные с необходимостью использовать пятый счетный триггер.

Известен счетчик с произвольным коэффициентом пересчета, содержащий счетчик (из четырех счетных триггеров при коэффициенте деления 13) и дешифратор, входами связанный с выходами всех счетных триггеров счетчика, а выходом соединенный с входом сброса счетчика. На основе указанного счетчика с произвольным коэффициентом пересчета может быть построен синхронный делитель частоты с коэффициентом деления 13 путем добавления дополнительного элемента И. Недостатком таким образом построенного делителя частоты являются большие аппаратные затраты, связанные с необходимостью организации дешифратора. При использовании счетчиков, серийно производимых в виде микросхем серии КМ500СТ2 (КС1543 ИЕ1), в которых предусмотрены только прямые выходы двух счетных триггеров, для построения дешифратора указанного делителя потребуется использовать не только четырехвходовый элемент И, но и еще два элемента НЕ.

Известен делитель количества последовательных импульсов (делитель частоты), содержащий четыре счетных триггера, сборку ИЛИ, элементы И, НЕ, в котором можно задать произвольный коэффициент деления, в том числе и коэффициент деления 13.

Недостатком указанного делителя частоты являются большие аппаратные затраты вследствие необходимости использовать сборку ИЛИ.

Наиболее близким по технической сущности к предложенному устройству является синхронный делитель частоты с коэффициентом деления 13, содержащий первый и второй двухразрядные счетчики, четыре двухвходовых элемента И-НЕ, четыре элемента НЕ, четырехвходовый элемент И с парафазным выходом.

Недостатком указанного делителя частоты являются большие аппаратные затраты и низкое быстродействие, обусловленное большой задержкой появления каждого 13-го импульса на выходе делителя частоты относительно момента появления счетного импульса на входе делителя частоты.

Цель изобретения - сокращение аппаратных затрат и повышение быстродействия делителя частоты.

Это достигается тем, что синхронный делитель частоты с коэффициентом деления 13, содержащий первый и второй двухразрядные счетчики, первый и второй входы синхросигналов которых соединены между собой и соответственно с входами первого и второго синхросигналов делителя, дополнительно содержит трехвходовый элемент И с парафазными выходами, причем вход делителя частоты соединен со счетным входом первого двухразрядного счетчика и с первым входом трехвходового элемента И, второй и третий входы которого соединены соответственно с первым и вторым информационными выходами второго двухразрядного счетчика, счетный вход которого соединен с выходом переноса первого двухразрядного счетчика, вход сброса которого соединен с входом сброса второго двухразрядного счетчика и с инверсным выходом трехвходового элемента И, прямой выход которого соединен с выходом делителя частоты.

Предложенный делитель частоты имеет такие признаки, как трехвходовый (а не четырехвходовый) элемент И с парафазными выходами, а также новая связь входа делителя частоты с первым входом трехвходового элемента И, кроме этого, новая связь инверсного выхода данного элемента И с входами сброса первого и второго двухразрядных счетчиков. Эти признаки отсутствуют во всех аналогах и прототипе и благодаря им достигается поставленная цель изобретения. В прототипе для построения делителя частоты используются два двухразрядных счетчика, четырехвходовый элемент И, три элемента И-НЕ и четыре элемента НЕ. При этом используются 15 внутренних связей. Кроме перечисленных элементов, реализованных на микросхемах серии 500, для связей необходимо еще использовать 15 согласующих резисторов. В результате для построения делителя частоты - прототипа требуется 6 мест на ТЭЗе для корпусов типа ДИП-16 микросхем указанной серии 500. Для построения предложенного делителя частоты необходимы всего два двухразрядных счетчика, один трехвходовый элемент И и три согласующих резистора. В результате на ТЭЗ для размещения микросхем серии 500, на которых можно построить предложенный делитель частоты, потребуется всего лишь 2 мест, из которых 2

мест, из которых 2 места для интегральных микросхем и

места для интегральных микросхем и  места для резисторов.

места для резисторов.

Таким образом, достигается сокращение аппаратурных затрат, так как требуется примерно в 2 раза меньше мест на ТЭЗ.

Задержка появления выходного сигнала на выходе делителя частоты - прототипа (сигнал СИТ на копии схемы прототипа) по отношению к входному сигналу на его входе (сигнал Р44) равна

Тзад.пр. = 2Тпер.счет. + 3 τэ. + 4 Тл.с. (1) где Т пер.счет. - величина задержки выходного переноса СО с выхода переноса второго двухразрядного счетчика по отношению к входному сигналу на счетном входе первого двухразрядного счетчика;

τэ.- величина задержки на одном логическом элементе типа И,НЕ;

Тл.с. - величина задержки на связях между элементами.

Считая Тпер.счет. ≈ 2 τэ.. и 4 Тл.c. ≈τэ., получим Тзад.пр. = 8 τэ.. Для предложенного делителя частоты появление указанного сигнала СИТ задерживается только на величину τэ.. по отношению к сигналу Р44. Таким образом, увеличение быстродействия для этого делителя частоты равно 8 раз.

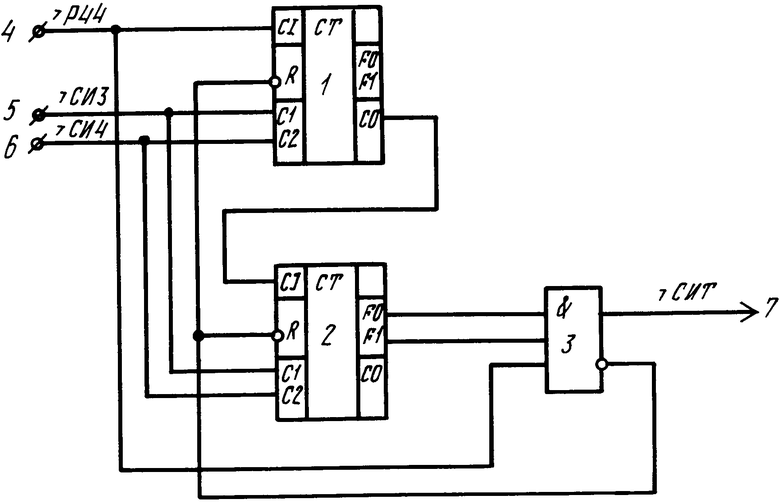

На фиг.1 изображена функциональная схема делителя частоты, где 1 - первый двухразрядный счетчик; 2 - второй двухразрядный счетчик; 3 - трехвходовый элемент И; 4 - вход делителя частоты;5 - вход первого синхросигнала; 6 - вход второго синхросигнала; 7 - выход делителя частоты.

Первый и второй двунаправленные счетчики предназначены для подсчета количества сигналов, поступающих на вход делителя частоты, и могут быть реализованы на микросхемах типа КМ500СТ2 или КС1543ИЕ1.

Вход 4 делителя частоты соединен с первым входом трехвходового элемента И и со счетным входом первого двухразрядного счетчика 1, первый и второй входы синхросигналов которого соединены с соответствующими входами первого 5 и второго 6 синхросигналов делителя частоты и с соответствующими входами второго двухразрядного счетчика 2, счетный вход которого соединен с выходом переноса первого двухразрядного счетчика 1, вход сброса которого соединен с инверсным выходом трехвходового элемента И 3 и с входом сброса второго двухразрядного счетчика 2, первый и второй информационные выходы которого соединены соответственно с вторым и третьим входами трехвходового элемента И 3, прямой выход которого соединен с выходом 7 делителя частоты.

Делитель частоты работает следующим образом.

Первый и второй синхросигналы СИ3 и СИ4 имеют длительность 20 нс и поступают на входы делителя частоты с периодом 120 нс. Сигнал Р44, поступающий на вход делителя частоты, имеет длительность 120 нс и период 256 мкс. На первом двухразрядном счетчике 1 и втором двухразрядном счетчике 2 осуществляется подсчет числа сигналов Р44, которые увеличивают содержимое этих двух счетчиков по указанным синхросигналам. В тот момент времени, когда содержимое этих двух счетчиков становится равным 12, т.е. значение первого двухразрядного счетчика 1 равно 002 и значение второго двухразрядного счетчика 2 равно 112, по поступлению тринадцатого сигнала Р44 открывается трехвходовый элемент И 3, на прямом выходе которого появляется сигнал СИТ длительностью 120 нс и периодом, равным 256 х13 ≈ 1/300 с, который поступает на выход 7 делителя частоты.

Одновременно сигнал с инверсного выхода трехвходового элемента И 3 поступает на вход сброса первого 1 и второго 2 двухразрядных счетчиков, которые по синхросигналам СИ3 и СИ4 обнуляются. Таким образом, делитель частоты снова готов к работе, чтобы указанным способом формировать следующий сигнал СИТ с периодом 1/300 с.

Технико-экономические преимущества предложенного делителя частоты по сравнению с прототипом заключаются в значительном сокращении аппаратурных затрат и повышении быстродействия. Оборудование для предложенного делителя по сравнению с прототипом сокращается на три элемента И-НЕ и четыре элемента НЕ, вместо четырехвходового элемента И применяется трехвходовый элемент И. Соответственно сокращается число связей и число согласующих резисторов. Быстродействие предложенного делителя частоты по сравнению с прототипом повышается в 8 раз. Следовательно, достигается цель изобретения - сокращение аппаратурных затрат и повышение быстродействия.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ С КОНТРОЛЕМ | 1992 |

|

RU2084015C1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ СИГНАЛА ПЕРЕПОЛНЕНИЯ | 1992 |

|

RU2020556C1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ПРЕДСКАЗАННЫХ СИГНАЛОВ ЧЕТНОСТИ ПРИ СДВИГАХ ДВОИЧНЫХ КОДОВ | 1992 |

|

RU2045772C1 |

| УСТРОЙСТВО ДЛЯ ВЫБОРКИ ТАКТОВЫХ СИГНАЛОВ | 1992 |

|

RU2084016C1 |

| УСТРОЙСТВО ДЛЯ ОТСЧЕТА ВРЕМЕНИ | 1990 |

|

RU2024920C1 |

| ШИФРАТОР | 1991 |

|

RU2023345C1 |

| РЕВЕРСИВНЫЙ ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНО-ДЕСЯТИЧНОГО КОДА В ДВОИЧНЫЙ | 1990 |

|

RU2022467C1 |

| УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ | 1991 |

|

RU2018933C1 |

| УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ | 1991 |

|

RU2018934C1 |

| ОТКАЗОУСТОЙЧИВОЕ УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ | 1991 |

|

RU2021631C1 |

Использование: изобретение относится к импульсной технике и может быть использовано при построении в процессорах формирователей импульсов продвижения интервального таймера с периодичностью 1/300 с. Сущность изобретения: устройство содержит два двухразрядных счетчика 1, 2 и трехвходовый элемент И 3 с парофазным выходом. 1 ил.

СИНХРОННЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ С КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ 13, содержащий первый и второй двухразрядные счетчики, первый и второй входы синхросигналов которых соединены между собой и соответственно с входами первого и второго синхросигналов делителя, отличающийся тем, что, с целью сокращения аппаратных затрат и повышения быстродействия, в него введен трехвходовый элемент И с парафазными выходами, вход делителя частоты соединен со счетным входом первого двухразрядного счетчика и с первым входом трехвходового элемента И, второй и третий входы которого соединены соответственно с первым и вторым информационными выходами второго двухразрядного счетчика, счетный вход которого соединен с выходом переноса первого двухразрядного счетчика, вход сброса которого соединен с входом сброса второго двухразрядного счетчика и с инверсным выходом трехвходового элемента И, прямой выход которого соединен с выходом делителя частоты.

| Устройство радиостанций с быстродействующими аппаратами Юза и Бодо | 1922 |

|

SU2130A1 |

| Техническое описание, Ч.1 | |||

| Общие сведения | |||

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Насос | 1917 |

|

SU13A1 |

Авторы

Даты

1994-09-30—Публикация

1991-04-04—Подача