Изобретение относится к вычислительной технике и может быть использовано для организации контроля работоспособности cдвигателей двоичных кодов высокопроизводительных цифровых вычислительных машин и систем.

Известно устройство [1] для формирования сигналов четности при сдвигах двоичных кодов, содержащее модуль формирования сигналов четности, узел сдвига контрольных разрядов, узел коммутации. В указанном устройстве при использовании модуля формирования сигналов четности, предложенного в изобретении [2] обеспечивается максимальная задержка формирования предсказанных сигналов четности, равная 12 τэ, где τэ задержка сигнала логическим элементом типа И-НЕ с количеством входов не более 5-ти. Указанного быстродействия известного устройства недостаточно, например, при использовании в паре с устройством для сдвига операндов, предложенном в [3] Это связано с тем, что при организации конвейерной обработки двоичных кодов (операндов), устройство для формирования сигналов четности при сдвигах двоичных кодов должно работать синхронно с устройством для сдвига двоичных кодов. Для этого устройство для формирования сигнала четности при сдвигах двоичных кодов должно иметь такое же или большее быстродействие, что и устройство для сдвига двоичных кодов, так как в противном случае необходимо ухудшить конвейер, подстраивая его к работе узла с худшим быстродействием. Максимальное же быстродействие устройств для сдвига двоичных кодов достигает 8 τэ(3) и на уровне логической структуры может быть увеличено до 6 τэ при технологических ограничениях использование для построения устройств логических элементов типа И-НЕ с количеством входов не более 5-ти.

Наиболее близким по технической сущности к заявляемому устройству является устройство [4] для формирования предсказанных сигналов четности при сдвигах двоичных кодов, содержащее модуль формирования сигналов четности, узел сдвига контрольных разрядов, дешифратор типа сдвига, дешифратор нулевого кода, формирователь дополнительного кода, формирователь кода маски, элемент И, причем модуль формирования сигналов четности содержит  формирователей сигналов четности (N количество разрядных входов информационного входа модуля (N 2S, S ≥ 2), К число разрядов в байте), формирователь маски, причем информационный вход модуля формирования сигналов четности является информационным входом устройства, выход модуля формирования сигналов четности соединен с информационным входом узла сдвига контрольных разрядов, выход которого является выходом устройства, выход знака которого соединен с первым входом элемента И, второй вход которого соединен с первым выходом дешифратора типа сдвига, второй и третий выходы которого соединены первым и вторым разрядными входами задания типа сдвига модуля формирования сигналов четности, вход блокировки которого соединен с выходом дешифратора нулевого кода и с первым разрядом входа дешифратора типа сдвига, второй разряд которого соединен с младшим разрядом входа задания величины сдвига устройства, а третий, четвертый и пятый разряды входа дешифратора типа сдвига образуют вход задания типа сдвига устройства, вход задания величины сдвига которого соединен с информационным входом формирователя дополнительного кода, группа старших разрядов выхода которого подключена к группе разрядов входа задания величины сдвига узла сдвига контрольных разрядов, вход задания типа сдвига которого соединен с выходом формирователя кода маски, группа разрядов информационного входа которого соединена с группой старших разрядов входа задания величины сдвига которого соединена с группой разрядов входа дешифратора нулевого кода, группа разрядов управляющего входа формирователя кода маски подключена к соответствующим разрядам входа задания типа сдвига устройства, разряд признака направления сдвига входа задания типа сдвига которого соединен с управляющим входом формирователя дополнительного кода, группа младших разрядов выхода которого соединена с группой разрядов входа задания величины сдвига модуля формирования сигналов четности, группа входов контрольных разрядов котоpого образуют группу входов контрольных разрядов устройства, а в модуле формирования сигналов четности вход формирователя кода маски является входом задания величины сдвига модуля, каждый i-й разряд информационного входа j-го формирователя сигнала четности (1 ≅ i ≅ (K-1), 1 ≅ j ≅

формирователей сигналов четности (N количество разрядных входов информационного входа модуля (N 2S, S ≥ 2), К число разрядов в байте), формирователь маски, причем информационный вход модуля формирования сигналов четности является информационным входом устройства, выход модуля формирования сигналов четности соединен с информационным входом узла сдвига контрольных разрядов, выход которого является выходом устройства, выход знака которого соединен с первым входом элемента И, второй вход которого соединен с первым выходом дешифратора типа сдвига, второй и третий выходы которого соединены первым и вторым разрядными входами задания типа сдвига модуля формирования сигналов четности, вход блокировки которого соединен с выходом дешифратора нулевого кода и с первым разрядом входа дешифратора типа сдвига, второй разряд которого соединен с младшим разрядом входа задания величины сдвига устройства, а третий, четвертый и пятый разряды входа дешифратора типа сдвига образуют вход задания типа сдвига устройства, вход задания величины сдвига которого соединен с информационным входом формирователя дополнительного кода, группа старших разрядов выхода которого подключена к группе разрядов входа задания величины сдвига узла сдвига контрольных разрядов, вход задания типа сдвига которого соединен с выходом формирователя кода маски, группа разрядов информационного входа которого соединена с группой старших разрядов входа задания величины сдвига которого соединена с группой разрядов входа дешифратора нулевого кода, группа разрядов управляющего входа формирователя кода маски подключена к соответствующим разрядам входа задания типа сдвига устройства, разряд признака направления сдвига входа задания типа сдвига которого соединен с управляющим входом формирователя дополнительного кода, группа младших разрядов выхода которого соединена с группой разрядов входа задания величины сдвига модуля формирования сигналов четности, группа входов контрольных разрядов котоpого образуют группу входов контрольных разрядов устройства, а в модуле формирования сигналов четности вход формирователя кода маски является входом задания величины сдвига модуля, каждый i-й разряд информационного входа j-го формирователя сигнала четности (1 ≅ i ≅ (K-1), 1 ≅ j ≅  ) соединен с [K(j-1)+i]-м разрядом информационного входа модуля, (j-1)-й вход контрольного разряда группы входов контрольных разрядов которого соединен с входом контрольного разряда j-го формирователя сигнала четности, вход маски которого соединен с первым выходом формирователя маски в модуле, первый разряд входа задания типа сдвига которого соединен с входом блокировки крайнего левого (1-го) формирователя сигнала четности.

) соединен с [K(j-1)+i]-м разрядом информационного входа модуля, (j-1)-й вход контрольного разряда группы входов контрольных разрядов которого соединен с входом контрольного разряда j-го формирователя сигнала четности, вход маски которого соединен с первым выходом формирователя маски в модуле, первый разряд входа задания типа сдвига которого соединен с входом блокировки крайнего левого (1-го) формирователя сигнала четности.

В известном устройстве дешифратор типа сдвига и дешифратор нулевого кода образуют узел управления, который может быть построен на одном элементе ПЗУ (постоянного запоминающего устройства). В описанном устройстве обеспечивается максимальное быстродействие (10 τэ), однако требуются большие аппаратные затраты, главным образом на построение модуля формирования сигналов четности.

Основным техническим результатом в заявленном устройстве является сокращение аппаратных затрат при сохранении быстродействия.

Технический результат достигается тем, что устройство для формирования предсказанных сигналов четности при сдвигах двоичных кодов, содержащее модуль формирования сигналов четности, узел сдвига контрольных разрядов, узел управления, формирователь дополнительного кода, формирователь кода маски, элемент И, причем модуль формирования сигналов четности содержит  формирователей сигналов четности (N количество разрядных входов информационного входа модуля (N 2S, S ≥ 2), К число разрядов в байте), формирователь маски, при этом информационный вход модуля формирования сигналов четности является информационным входом устройства, выход модуля формирования сигналов четности соединен с информационным входом узла сдвига контрольных разрядов, выход которого является выходом устройства, вход знака которого соединен с первым входом элемента И, второй вход которого соединен с первым выходом узла управления, второй и третий выходы которого соединены с первым и вторым разрядными входами задания типа сдвига модуля формирования сигналов четности, вход блокировки которого соединен с четвертым выходом узла управления, разряды первого входа которого соединены с группой младших разрядов входа задания величины сдвига устройства, а разряды второго входа узла управления образуют вход задания типа сдвига устройства, вход задания величины сдвига которого соединен с информационным входом формирователя дополнительного кода, группа старших разрядов выхода которого подключена к группе разрядов входа задания величины сдвига узла сдвига контрольных разрядов, вход задания типа сдвига котоpого соединен с выходом формирователя кода маски, группа разрядов информационного входа которого соединена с группой старших разрядов входа задания величины сдвига устройства, группа разрядов управляющего входа формирователя кода маски подключена к соответствующим разрядам входа задания типа сдвига устройства, разряд признака направления сдвига входа задания типа сдвига которого соединен с управляющим входом формирователя дополнительного кода, группа младших разрядов выхода которого соединена с группой разрядов входа задания величины сдвига модуля формирования сигналов четности, группа входов контрольных разрядов которого образует группу входов контрольных разрядов устройства, а в модуле формирования сигналов четности вход формирователя кода маски является входом задания величины сдвига модуля, каждый i-й разряд информационного входа j-го формирователя сигнала четности (1 ≅ i ≅ (K-2), 1 ≅ j ≅

формирователей сигналов четности (N количество разрядных входов информационного входа модуля (N 2S, S ≥ 2), К число разрядов в байте), формирователь маски, при этом информационный вход модуля формирования сигналов четности является информационным входом устройства, выход модуля формирования сигналов четности соединен с информационным входом узла сдвига контрольных разрядов, выход которого является выходом устройства, вход знака которого соединен с первым входом элемента И, второй вход которого соединен с первым выходом узла управления, второй и третий выходы которого соединены с первым и вторым разрядными входами задания типа сдвига модуля формирования сигналов четности, вход блокировки которого соединен с четвертым выходом узла управления, разряды первого входа которого соединены с группой младших разрядов входа задания величины сдвига устройства, а разряды второго входа узла управления образуют вход задания типа сдвига устройства, вход задания величины сдвига которого соединен с информационным входом формирователя дополнительного кода, группа старших разрядов выхода которого подключена к группе разрядов входа задания величины сдвига узла сдвига контрольных разрядов, вход задания типа сдвига котоpого соединен с выходом формирователя кода маски, группа разрядов информационного входа которого соединена с группой старших разрядов входа задания величины сдвига устройства, группа разрядов управляющего входа формирователя кода маски подключена к соответствующим разрядам входа задания типа сдвига устройства, разряд признака направления сдвига входа задания типа сдвига которого соединен с управляющим входом формирователя дополнительного кода, группа младших разрядов выхода которого соединена с группой разрядов входа задания величины сдвига модуля формирования сигналов четности, группа входов контрольных разрядов которого образует группу входов контрольных разрядов устройства, а в модуле формирования сигналов четности вход формирователя кода маски является входом задания величины сдвига модуля, каждый i-й разряд информационного входа j-го формирователя сигнала четности (1 ≅ i ≅ (K-2), 1 ≅ j ≅  ) соединен с [K(j-1)+i]-м разрядом информационного входа модуля, (j-1)-й вход контрольного разряда группы входов контрольных разрядов которого соединен с входом контрольного разряда j-го формирователя сигнала четности, вход маски которого соединен с первым выходом формирователя маски в модуле, (j-1)-й разряд выхода которого соединен с выходом сигнала четности j-го формирователя сигнала четности, а первый разряд входа задания типа сдвига модуля соединен с входом блокировки крайнего левого (1-го) формирователя сигнала четности, содержит дополнительный формирователь сигнала четности, i-й [0 ≅ i ≅ (K-1)] разряд информационного входа которого соединен с (N-K+1+i)-м разрядом информационного входа модуля, вход блокировки которого соединен с входом блокировки дополнительного формирователя сигнала четности, вход контрольного разряда которого соединен с

) соединен с [K(j-1)+i]-м разрядом информационного входа модуля, (j-1)-й вход контрольного разряда группы входов контрольных разрядов которого соединен с входом контрольного разряда j-го формирователя сигнала четности, вход маски которого соединен с первым выходом формирователя маски в модуле, (j-1)-й разряд выхода которого соединен с выходом сигнала четности j-го формирователя сигнала четности, а первый разряд входа задания типа сдвига модуля соединен с входом блокировки крайнего левого (1-го) формирователя сигнала четности, содержит дополнительный формирователь сигнала четности, i-й [0 ≅ i ≅ (K-1)] разряд информационного входа которого соединен с (N-K+1+i)-м разрядом информационного входа модуля, вход блокировки которого соединен с входом блокировки дополнительного формирователя сигнала четности, вход контрольного разряда которого соединен с  -м входом группы входов контрольных разрядов модуля, второй разрядный вход задания типа сдвига которого соединен с входом блокировки

-м входом группы входов контрольных разрядов модуля, второй разрядный вход задания типа сдвига которого соединен с входом блокировки  -го формирователя сигнала четности, выход переноса которого соединен с выходом переноса первого формирователя сигнала четности, вход переноса каждого j-го [1 ≅ j ≅ (

-го формирователя сигнала четности, выход переноса которого соединен с выходом переноса первого формирователя сигнала четности, вход переноса каждого j-го [1 ≅ j ≅ ( 2)] формирователя сигнала четности соединен с выходом переноса (j+1)-го формирователя сигнала четности, вход маски которого соединен с вторым выходом формирователя маски, крайний левый (нулевой) разряд информационного входа каждого j-го формирователя сигнала четности соединен с [K(j-1)]-м разрядом информационного входа модуля, вход знака которого соединен с входом знака

2)] формирователя сигнала четности соединен с выходом переноса (j+1)-го формирователя сигнала четности, вход маски которого соединен с вторым выходом формирователя маски, крайний левый (нулевой) разряд информационного входа каждого j-го формирователя сигнала четности соединен с [K(j-1)]-м разрядом информационного входа модуля, вход знака которого соединен с входом знака  -го формирователя сигнала четности и с выходом элемента И устройства.

-го формирователя сигнала четности и с выходом элемента И устройства.

Технический результат сокращение аппаратных затрат достигается благодаря тому, что вместо переноса остающегося кода в каждом формирователе сигнала четности в соседний справа формирователь сигнала четности (через второй информационный вход) осуществляется перенос соответствующего сигнала четности в каждый формирователь сигнала четности из соседнего справа формирователя сигнала четности, что обуславливает более простую структуру формирователей сигнала четности и, следовательно, сокращение аппаратных затрат, несмотря на введение дополнительного формирователя сигнала четности, необходимого для обеспечения такой же достоверности формирования сигналов четности в заявляемом устройстве, что и в прототипе.

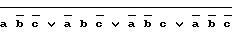

На фиг. 1 изображена структурная схема устройства; на фиг. 2 структурная схема модуля формирования сигналов четности; на фиг. 3 структурная схема первого формирователя сигналов четности в модуле формирования сигналов четности; на фиг. 4 структурная схема дополнительного формирователя сигнала четности; на фиг. 5 структурная схема  -го формирователя сигнала четности в модуле формирования сигналов четности; на фиг. 6 функциональная схема узла свертки по модулю два, используемых в формирователях сигналов четности; на фиг. 7 функциональная схема дешифратора типа сдвига.

-го формирователя сигнала четности в модуле формирования сигналов четности; на фиг. 6 функциональная схема узла свертки по модулю два, используемых в формирователях сигналов четности; на фиг. 7 функциональная схема дешифратора типа сдвига.

Устройство (фиг. 1) содержит модуль формирования сигналов четности 1, узел сдвига контрольных разрядов 2, узел управления 3, формирователь дополнительного кода 4, формирователь кода маски 5, элемент 6, дешифратор 7 типа сдвига в узле, дешифратор 8 нулевого кода в узле, вход 9 задания типа сдвига устройства, вход 10 задания величины сдвига устройства, информационный вход формирователя 4, вход 11 знака устройства, первый вход элемента 6, информационный вход 12 модуля 1 и устройства, группа входов 13 контрольных разрядов модуля 1 и устройства, вход 14 знака модуля 1, выход элемента 6, группа младших разрядов 15 входа 10, группа разрядов первого входа узла, вход 16 разряда входа 10, вход 17 разряда признака направления сдвига входа 9, управляющий вход узла 4, первый выход 18 узла 3, второй вход элемента 6, второй выход 19 узла 3, первый разрядный вход задания типа сдвига модуля 1, третий выход 20 узла 3, второй разрядный вход задания типа сдвига модуля 1, четвертый выход 21 узла 3, вход блокировки узла 1, группа младших разрядов выхода 22 формирователя 4, группа разрядов входа задания величины сдвига модуля 1, группа старших разрядов выхода 23 формирователя 4, группа разрядов входа задания величины сдвига узла 2, группа разрядов информационного входа 24 формирователя 5, группа старших разрядов входа 10, вход 25 задания типа сдвига узла 2, выход формирователя 5, выход 26 модуля 1, информационный вход узла 2, выход 27 устройства, выход узла 2, первый (крайний левый) формирователь 28 сигнала четности, j-й формирователь 29 сигнала четности [2 ≅ j ≅ ( 1)] дополнительный формирователь 30 сигнала четности,

1)] дополнительный формирователь 30 сигнала четности,  -й крайний правый формирователь 31 сигнала четности, формирователь 32 маски в модуле 1, первый выход 33 формирователя 32, вход маски формирователей 28, 29, 31, второй выход 34 формирователя 32, вход маски формирователя 30, вход 35 переноса узла 28 (29,31), выход 36 переноса узла 28 (29), вход 37 контрольного разряда j-го формирователя сигнала четности, (j-1)-й вход контрольного разряда группы входов 13 контрольных разрядов (1≅ j ≅

-й крайний правый формирователь 31 сигнала четности, формирователь 32 маски в модуле 1, первый выход 33 формирователя 32, вход маски формирователей 28, 29, 31, второй выход 34 формирователя 32, вход маски формирователя 30, вход 35 переноса узла 28 (29,31), выход 36 переноса узла 28 (29), вход 37 контрольного разряда j-го формирователя сигнала четности, (j-1)-й вход контрольного разряда группы входов 13 контрольных разрядов (1≅ j ≅  ); вход 38 контрольного разряда дополнительного и

); вход 38 контрольного разряда дополнительного и  -го формирователей сигнала четности; информационный вход 39 узла 28, разряда [0/6] входа 12; информационный вход 40 узла 30, разряды [25/31] входа 12; (при N 32, К 8); информационный вход 41 узла 31, разряды [24/30] входа 12 (при N 32, К 8); выход 42 формирователя 30; выход 43 сигнала четности узла 28 (29); выход 44 сигнала четности узла 31; группа элементов И-НЕ 45 в узле 28 (29); узел свертки 46 по модулю два с тремя парафазными входами и одним парафазным выходом (как на фиг. 47 без входа 19); узел свертки 47 по модулю два с тремя парафазными входами a

-го формирователей сигнала четности; информационный вход 39 узла 28, разряда [0/6] входа 12; информационный вход 40 узла 30, разряды [25/31] входа 12; (при N 32, К 8); информационный вход 41 узла 31, разряды [24/30] входа 12 (при N 32, К 8); выход 42 формирователя 30; выход 43 сигнала четности узла 28 (29); выход 44 сигнала четности узла 31; группа элементов И-НЕ 45 в узле 28 (29); узел свертки 46 по модулю два с тремя парафазными входами и одним парафазным выходом (как на фиг. 47 без входа 19); узел свертки 47 по модулю два с тремя парафазными входами a , b

, b , с

, с и одним парафазным выходом (y

и одним парафазным выходом (y ), функциональная схема которого изображена на фиг. 6; узел свертки 48 по модулю два с двумя входами и одним парафазным выходом; узел свертки 49 по модулю два; группа элементов И 50 в узле 30; узел свертки 51 по модулю два с тремя парафазными входами; элемент 4И-НЕ 52; элемент 4И-НЕ 53 с парафазным выходом; инверсный выход 54 узла 47 (45); прямой выход 55 узла 47 (45, 47, 48); прямой разрядный вход 56 "а" входа узла 47, подключенный к прямому выходу "y" 55 узла 46; инверсный разрядный вход 57 "а" входа узла 47, подключенный к инверсному выходу "y" 54 узла 46; элементы НЕ 58 в дешифраторе 7; элемент И 59 в дешифраторе 7; элемент 4И 60 в дешифраторе 7; элементы 2И-НЕ 61 в дешифраторе 7; соответственно 0-й, 1-й и 2-й разряды входа 9, 62, 63, 64.

), функциональная схема которого изображена на фиг. 6; узел свертки 48 по модулю два с двумя входами и одним парафазным выходом; узел свертки 49 по модулю два; группа элементов И 50 в узле 30; узел свертки 51 по модулю два с тремя парафазными входами; элемент 4И-НЕ 52; элемент 4И-НЕ 53 с парафазным выходом; инверсный выход 54 узла 47 (45); прямой выход 55 узла 47 (45, 47, 48); прямой разрядный вход 56 "а" входа узла 47, подключенный к прямому выходу "y" 55 узла 46; инверсный разрядный вход 57 "а" входа узла 47, подключенный к инверсному выходу "y" 54 узла 46; элементы НЕ 58 в дешифраторе 7; элемент И 59 в дешифраторе 7; элемент 4И 60 в дешифраторе 7; элементы 2И-НЕ 61 в дешифраторе 7; соответственно 0-й, 1-й и 2-й разряды входа 9, 62, 63, 64.

Цифры около входов и выходов на фиг. 1, 2, 7 обозначают номера разрядов входов и выходов узлов.

Модуль 1 (на фиг. 2) для частного случая N 32, К 8 (предназначен для формирования сигналов четности на выходе 23 с учетом только битных сдвигов) в пределах [0 (K-1)] Модуль 1 содержит  формирователей 28, 29, 31 сигналов четности (в рассматриваемом конкретном случае

формирователей 28, 29, 31 сигналов четности (в рассматриваемом конкретном случае

4, фиг. 2), формирователь маски 32 и дополнительный формирователь 30 сигнала четности.

4, фиг. 2), формирователь маски 32 и дополнительный формирователь 30 сигнала четности.

Структурная схема формирователя 28 (фиг. 3) содержит группу из (К-1) элементов И-НЕ 45, узлы сложения по модулю два 46, 47, 48, 49, которые тождественны таковым в аналоге 2 и принцип построения которых демонстрируется на фиг. 6 примером построение узла 47. Узел 46 так же, как и узел 51, аналогичен по структуре узлу 47 (фиг. 6) с тем отличием, что отсутствует вход 19 и соответствующий вход элементов И-НЕ 52.

Узлы 48, 49 могут иметь как одиночные прямые, так и парафазные входы в зависимости от конкретных возможностей использования элементной базы. В случае, если входы элемента 49 одинарные и прямые, то используются одинарный прямой выход "y" 55 узла 46 и 47 для подключения их к входам узла 49. В качестве выхода из узла 49 и выхода 44 узла 51 всегда используется одинарный прямой вход y (55) во всех формирователях 28, 29, 31.

Узел 28 функционирует следующим образом.

При лог. "0" на входе 19 на выходе 36 устанавливается лог. 0, так как элементы 52 (фиг. 6) в узле 47 блокируются и на выходах их устанавливаются логические единицы. В результате на выходе 54 элемента 53 устанавливается  1, а на выходе 55 y 0, что соответствует лог. 0 на выходе 36. При логической единице на входе 19 узел 47 выполняет суммирование по модулю два сигналов, установленных на трех видах, т.е. выполняются функции:

1, а на выходе 55 y 0, что соответствует лог. 0 на выходе 36. При логической единице на входе 19 узел 47 выполняет суммирование по модулю два сигналов, установленных на трех видах, т.е. выполняются функции:

Y=

∨

∨ b

b ∨

∨

c∨

c∨

Y  (1)

(1)

В соответствии с выражением (1) функционируют также узлы 46, 51. При этом на выходе 44 используются только функции y. На выходе элемента 48 формируется функция:

f= ∨

∨

f  (2) где d, e значение сигналов на входах элемента 48. В соответствии с выражением (2) функционирует и элемент 49. При этом на выходе 43 формируется сигнал в соответствии с функцией.

(2) где d, e значение сигналов на входах элемента 48. В соответствии с выражением (2) функционирует и элемент 49. При этом на выходе 43 формируется сигнал в соответствии с функцией.

Таким образом, на выходе 36 формируется сигнал, соответствующий сумме по модулю два сигналов, сформированных на выходе группы элементов 45, а на выходе 43 сигнал, соответствующий сумме по модулю два сигналов, сформированных на выходе группы элементов 45 и входах 35, 37.

На выходы группы элементов 45 передаются только те сигналы входа 39 (41), которые пропускаются маской на входе 33. На выходах группы 45, заблокированных маской с входа 33, формируются логические нули, т.е. ноль на прямом выходе и единица на инверсном.

В качестве выходов элементов И-НЕ группы 45 (так же как и 50) используются парафазные выходы (т.е. прямой и инверсный выходы). Количество разрядов входа 33 равно количеству разрядов входа 39 (42). Код маски зависит от кода величины битных сдвигов. При этом логические единицы устанавливаются в таком количестве крайних слева разрядов кода маски (и входа 33), которое равно заданной величине битных сдвигов на входе 22 [в пределах 0-(К-1)]

Узел 30 функционирует аналогично узлу 28 с тем отличием, что на выходе 42 формируется сигнал, соответствующий сумме по модулю два сигналов, сформированных на выходах группы элементов 50 и входе 38 при лог. "1" на выходе 21 (фиг. 4). При лог. "0" на выходе 21, на выходе 42 узла 30 устанавливается лог. "0".

При этом на входе 34 формируется инверсный код маски от сдвинутого логически влево на один разряд кода, формируемого на входе 33.

Узел 31 (фиг. 5) функционирует аналогично узлу 28 с тем отличием, что на выходе 44 формируется сигнал, соответствующий сумме по модулю два сигналов, сформированных на выходах группы 45 элементов И-НЕ и входах 14, 38, 36 при логической единице на входе 20. При логическом нуле на входе 20, на выходе 44 формируется сигнал суммы по модулю два сигналов, сформированных на входах 14, 36. Вход 14 (и следовательно, выход элемента 6 (фиг. 1) является парафазным).

Узлы 28, 29, 31 предназначены для формирования сигналов, четности на разрядах выхода 26 модуля 1. Узлы 28, 29 формируют также сигналы переноса на выходах 36. Узел 30 предназначен только для формирования сигнала переноса на выходе 42 способом, отличным от способа формирования переноса в узлах 28, 29. Это связано с тем, что контроль безошибочности части кода, выдвигаемой за пределы [1 ≅ j ≅ ( 1)] группы, "К" разрядов выдвигаемого кода обеспечивается благодаря формированию сигнала четности для оставшейся части кода на (j-1)-м разряде выхода 26 путем суммирования по модулю два сигналов выдвигаемого кода и сигнала на выходе 37 контрольного разряда (т.е. с использованием контрольного разряда), а в

1)] группы, "К" разрядов выдвигаемого кода обеспечивается благодаря формированию сигнала четности для оставшейся части кода на (j-1)-м разряде выхода 26 путем суммирования по модулю два сигналов выдвигаемого кода и сигнала на выходе 37 контрольного разряда (т.е. с использованием контрольного разряда), а в  -м формирователе 31 использование контрольного разряда при арифметических и логических сдвигах вправо блокируется (фиг. 5 через вход 20 предусмотрена блокировка элемента 47 узла 31).

-м формирователе 31 использование контрольного разряда при арифметических и логических сдвигах вправо блокируется (фиг. 5 через вход 20 предусмотрена блокировка элемента 47 узла 31).

Для того, чтобы обеспечить контроль выдвигаемого кода в  -й группе разрядов входа 12 и, следовательно, обеспечить такую же достоверность работы заявляемого устройства, что и прототипа, используется узел 30, с помощью которого на выходе 42 формируется сигнал переноса (т.е. сигнал четности выдвигаемого кода) с использованием входа 38 контрольного разряда. Для этого с входа 39 с помощью кода маски на входе 40 выделяется оставшаяся часть кода (оставшийся код) и после суммирования его сигналов четности всего байта на входе 38 на выходе 42 формируется сигнал четности выдвигаемого кода, т.е. одиночная ошибка в выдвигаемом коде всегда будет обнаруживаться, так как контрольный сигнал на выходе (

-й группе разрядов входа 12 и, следовательно, обеспечить такую же достоверность работы заявляемого устройства, что и прототипа, используется узел 30, с помощью которого на выходе 42 формируется сигнал переноса (т.е. сигнал четности выдвигаемого кода) с использованием входа 38 контрольного разряда. Для этого с входа 39 с помощью кода маски на входе 40 выделяется оставшаяся часть кода (оставшийся код) и после суммирования его сигналов четности всего байта на входе 38 на выходе 42 формируется сигнал четности выдвигаемого кода, т.е. одиночная ошибка в выдвигаемом коде всегда будет обнаруживаться, так как контрольный сигнал на выходе ( -1)-го формирователя 29 формируется без непосредственного использования сигналов выдвигаемого кода на входе (

-1)-го формирователя 29 формируется без непосредственного использования сигналов выдвигаемого кода на входе ( )-го формирователя 31.

)-го формирователя 31.

Формирователь 27 маски предназначен для формирования кодов маски на выходах 33, 34 в соответствии с табл. 1 (для случая К 8).

Формирователь 32 может быть построен на элементах ПЗУ или на логических элементах (как известный узел [1]).

Модуль 1 функционирует следующим образом.

В исходном состоянии на входах 12 устанавливается сдвигаемый код (М). На выходе 13 код (К) побайтных контрольных разрядов для кода М. На входе 14 устанавливается код знака при арифметическом сдвиге вправо и нулевой код в остальных случаях. На входе 19 устанавливается лог. "1" во всех случаях сдвига вправо и при циклических сдвигах. В остальных случаях на выходе 19 устанавливается лог "0". На входе 20 устанавливается лог. "1" во всех случаях сдвига влево и при циклических сдвигах. В остальных случаях на входе 20 устанавливается лог. "0". На выходе 21 устанавливается лог. "0" при нулевом коде на группе 15 младших разрядов входа величины сдвига и лог."1" в противном случае. На входе 22 устанавливается код (m) величины сдвига в пределах группы "К" [0 ≅ m ≅ (K-1)] разрядов.

В результате при сдвигах влево на разрядах 0/3 выхода 26 формируются побайтные сигналы четности для кода, полученного в результате сдвига влево кода, установленного на входе 12 на величину разрядов, заданную кодом на входе 22. При сдвигах вправо на разрядах 0/3 выход 26 формируется код побайтных сигналов четности сдвинутой циклически влево на один разряд относительно кода побайтных сигналов четности для входа 12 на величину, задаваемую дополнительным кодом от кода, установленного на входе 22. При нулевых сдвигах значения контрольных разрядов с входов 13 транзитом передаются на входы 26. При сдвигах влево, кроме циклического, на выходе 36 формирователя 28 формируется нулевой код. В остальных случаях на выходах переноса всех формирователей 28, 29, 30, а на выходах переноса узлов 29, 30 во всех случаях формируются сигналы четности выдвигаемой части кода, установленного на информационном входе соответствующего формирователя сигнала четности.

Дешифратор 7 сдвига предназначен для формирования управляющих сигналов на выходах 18, 19, 29 с учетом кодов на входах 9, 16, 21. Дешифратор 8 предназначен для формирования сигнала блокировки (лог. "0") на выходе 21 при нулевом коде на входе 15.

Дешифраторы 7, 8 образуют узел управления 3, предназначенный для формирования управляющих сигналов на выходах 18, 19, 20, 21 с учетом сигналов на входах 9, 15.

Узел управления 3 может быть построен на одном элементе ПЗУ, закодированном в соответствии с табл. 2, в которой в крайней строке и крайнем левом столбце указаны в 16-тиричном представлении значения кодов на входах, соответственно 15 [разряды 0, 1, 2 (16)] 9 [разряды 0 (2)] а в остальных клетках указаны соответствующие 16-ти-разные значения кода на выходах 18, 19, 20, 21.

Узел 3 (при реализации устройства в виде большой интегральной схемы (БИС) может быть реализован на логических элементах при построении дешифратора 7 по схеме на фиг. 7 с использованием элементов НЕ 58, И 59, И/НЕ 61. Дешифратор 8 может быть построен на трехвходовом элементе ИЛИ, входы которого соединены с разрядами входа 15, а выход элемента ИЛИ соединен с выходом 21 и входом 21 (фиг. 7) дешифратора 7.

На входе 9 узла 3 и устройства в соответствии с типом сдвига могут устанавливаться следующие коды на разрядах [0/2]

0Х0 логический сдвиг влево (ЛЛ);

001 логический сдвиг вправо (ЛП);

011 арифметический сдвиг вправо (АП);

1Х0 циклический сдвиг влево (ЦЛ);

1Х1 циклический сдвиг вправо (ЦП), где Х произвольное значение бита.

Узел 4 является известным формирователем дополнительного кода 4. При лог. "1" на входе 17 на выходе узла 4 (разрядах 22, 23) формируется дополнительный код от кода на входе 10. При лог. "0" на входе 17 код с входа 10 транзитом передается на выход узла 4.

Формирователь 5 кода маски предназначен для формирования кода маски для маскирования соответствующих правых и левых разрядов циклически сдвинутого влево в узле 2 кода, установленного на входе 26.

Узел 2 представляет собой узел циклических сдвигов влево, построенный на мультиплексорах, например, типа К155КП7, и имеет структуру, аналогичную структуре узла сдвига контрольных разрядов прототипа с тем отличием, что j-й разряд входа и выхода (и мультиплексор) узла сдвига контрольных разрядов прототипа является ( j)-м разрядом входа и выхода (и мультиплексора) узла 2, где 0 ≅ j ≅ (

j)-м разрядом входа и выхода (и мультиплексора) узла 2, где 0 ≅ j ≅ ( 1). При этом вход блокировки мультиплексора [j 0, 1, (

1). При этом вход блокировки мультиплексора [j 0, 1, ( 1)] при отсчете слева направо соединен с j-м разрядным входом входа 25 задания типа сдвига узла 2 и с j-м разрядным выходом выхода формирователя 5.

1)] при отсчете слева направо соединен с j-м разрядным входом входа 25 задания типа сдвига узла 2 и с j-м разрядным выходом выхода формирователя 5.

Формирователь 5 может быть построен на элементах ПЗУ, закодированных в соответствии с табл. 3 (для случая N 32, K 8).

Устройство функционирует следующим образом.

В исходном состоянии на входе 12 устанавливается сдвигаемый код, на входе 13 код контрольных бит, значение каждого j-го бита которого равно значению сигнала четности j-го байта сдвигаемого кода на входе 12, где 0 ≅ j ≅ ( 1) при отсчете слева направо.

1) при отсчете слева направо.

На входе 9 устанавливается код типа сдвига.

На входе 10 устанавливается код величины сдвига. При арифметическом сдвиге вправо на входе 11 устанавливается код знака. На выходе 27 формируется  -разрядный код предсказанных сигналов четности для сдвинутого кода.

-разрядный код предсказанных сигналов четности для сдвинутого кода.

Рассмотрим в качестве примера сдвиги кода 10111000111100001111000011110000 на величину

l + L x 8 5 + 2 х 8 21, т.е. l 5 (101)дв-ов код на младших разрядах 15 входа 10, а L 2 (10)дв код на старших разрядах 24 входа 10. На входе 13 устанавливается код 0000. Последовательно рассмотрим все типы сдвига.

При логическом сдвиге влево (ЛЛ) на разрядах [0/2] входа 9 устанавливается код 0Х0. На выходах 18, 19, 20, 21 узла 3 установится (в соответствии с табл. 2) код 3 (0011)дв. На входе 17 установится логический ноль. На разрядах 22, 23 установятся коды соответственно 101, 10. На входе 14 установится лог. "0". На информационных входах формирователей 28, 29, 31 установятся коды соответственно 1011100, 1111000, 1111000, 1110000, 1111000. На выходах 33, 34 установятся коды соответственно 1111100, 0000111 (табл. 1). На выходе 36 установится лог. "0" вследствие блокировки узла 47 формирователя 28 лог. "0" с входа 19. На выходах переноса формирователей 29, 30 установятся коды соответственно 0, 0, 0. На выходах сигналов четности формирователей 28, 29, 31 (на разрядах 0/3 выхода 26) установится код 0000. На выходе 25 (в соответствии с табл. 3) сформируется код 1100. В узле 2 осуществляется циклический сдвиг влево кода 0000 на два разряда и два разряда справа полученного (сдвинутого) кода "обнуляются" маской на входе 25, в результате на разрядах [0/3] выхода 27 формируется код 0000.

При логическом сдвиге вправо (ЛП) на входе 9 устанавливается код 001.На выходах 18, 19, 20, 21 установится код 5 0101. На разрядах 22, 23 установятся коды соответственно 011 и 01, так как формируется дополнительный код 01011 от кода 10101 21. На выходе 25 установится код 0011. На входе 14 установится лог. "0". На выходах 33, 34 установятся коды 1110000, 0011111.

На информационном входе первого 28, второго 29, третьего 29, дополнительного 30 и четвертого 31 формирователей сигнала четности установятся коды соответственно 1011100, 1111000, 1111000, 1110000, 1111000. На выходах переноса 1-го, 2-го, 3-го и дополнительного формирователей 28, 29, 30 устанавливаются коды соответственно 0, 1, 1, 1. В результате на разрядах [0/3] выхода 26 установится код 1000, который в узле 2 циклически сдвигается на один разряд влево с формированием кода 0001, два разряда слева которого обнуляются маской 0011 на входе 25. В результате на выходе 27 сформируется код 0001 предсказанных сигналов четности для логически сдвинутого вправо кода, равного 00000000, 00000000, 00000101, 11000111.

При арифметическом сдвиге (АП) устройство функционирует так же, как и при логическом сдвиге вправо, с тем отличием, что на входе 11 устанавливается код знака, в рассматриваемом примере, лог. "1", так как нулевой разряд сдвигаемого кода равен "1", а на выходах 18, 19, 20, 21 формируется код 13 1011 (табл. 2). В результате код (лог. "1") с входа 11 будет передан на вход 14. В результате на выходе 44 формирователя 31 сформируется код 1, т.е. на выходе 26 сформируется код 1001, который циклически сдвигается влево на один разряд с формированием кода 0011, в котором два разряда слева "обнуляются" кодом маски 0011 с входа 25. Таким образом на выходе 27 сформируется код 0011 предсказанных сигналов четности для арифметически сдвинутого вправо кода, равного 11111111, 11111111, 11111101, 11000111.

При циклическом сдвиге влево (ПЛ) устройство функционирует так же, как и при логическом сдвиге влево с тем отличием, что на выходах 18, 19, 20, 21 формируется код 7 (0111)дв (табл. 2), а на выходе 25 код 1111. В результате на выходе 36 формируется сигнал четности "выдвигаемой" части кода, установленной на входе 39 и равный лог. "0". В результате на выходе 27 сформируется код 0000 предсказанных сигналов четности для циклически сдвинутого влево кода, равного 000111100001011100011110 00011110.

При циклическом сдвиге вправо (ЦП) устройство функционирует так же, как и при логическом сдвиге вправо с тем отличием, что на выходах 18, 19, 20, 21 устанавливается код 7 (0111)дв (табл. 2), а на выходе 25 код 1111. В результате на выходе 26 установится код 1001, который в узле 2 циклически сдвигается на один разряд влево с формированием кода 0011, который передается на разряды [0/3] выхода 27 и представляет собой код предсказанных сигналов четности для циклически сдвинутого вправо кода, равного 10000111100001111000010111000111.

При "нулевом" сдвиге, т.е. при нулевом коде на входе 10, на выходах 18, 19, 20, 21 устанавливается код в соответствии с табл. 2. Однако, при любом коде на входе 9 рассматриваемого случая на выходах 18, 21 устанавливаются лог. "0". На разрядах 22, 23 устанавливаются лог. "0". На выходе 25 устанавливается единичный код (табл. 3). На выходе 33 установится нулевой код, который заблокирует передачу кода с информационных входов формирователей 28, 29, 31 на выходы группы элементов И-НЕ 45, 50. В результате сигналы четности с входа 13 транзитом передаются на соответствующие разряды выхода 27, что и требуется.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ СИГНАЛА ПЕРЕПОЛНЕНИЯ | 1992 |

|

RU2020556C1 |

| УСТРОЙСТВО ДЛЯ ОТСЧЕТА ВРЕМЕНИ | 1990 |

|

RU2079165C1 |

| УСТРОЙСТВО ДЛЯ ОТСЧЕТА ВРЕМЕНИ | 1990 |

|

RU2024920C1 |

| Устройство для предсказания сигналов четности при сдвигах двоичных кодов | 1989 |

|

SU1735852A1 |

| УСТРОЙСТВО ДЛЯ ВЫБОРКИ ТАКТОВЫХ СИГНАЛОВ | 1992 |

|

RU2084016C1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ С КОНТРОЛЕМ | 1992 |

|

RU2084015C1 |

| Устройство для формирования сигналов четности при сдвигах двоичных кодов | 1989 |

|

SU1783527A1 |

| Устройство для отсчета времени | 1990 |

|

SU1784959A1 |

| УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ | 1991 |

|

RU2021632C1 |

| ОТКАЗОУСТОЙЧИВОЕ УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ | 1991 |

|

RU2021631C1 |

Изобретение относится к вычислительной технике и может быть использовано для организации контроля работоспособности сдвигателей двоичных кодов высокопроизводительных цифровых вычислительных машин и систем. Основным техническим результатом устройства является сокращение аппаратных затрат (по сравнению с прототипом) при сохранении высокого быстродействия. Технический результат достигается благодаря тому, что устройство содержит узел сдвига контрольных разрядов, узел управления, формирователь дополнительного кода, формирователь кода маски, элементт И, модуль формирования сигналов четности, содержащий N/K формирователей сигналов четности (N количество разрядных входов информационного входа устройства (N=2s, s≥ 2), K число разрядов в байте) формирователь маски содержит в модуле формирования сигналов четности дополнительный формирователь сигналов четности с новыми связями, что позволяет существенно упростить каждый формирователь сигнала четности. 7 ил. 3 табл.

УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ПРЕДСКАЗАННЫХ СИГНАЛОВ ЧЕТНОСТИ ПРИ СДВИГАХ ДВОИЧНЫХ КОДОВ, содержащее модуль формирования сигналов четности, узел сдвига контрольных разрядов, узел управления, формирователь дополнительного кода, формирователь кода маски и элемент И, модуль формирования сигналов четности содержит N /K формирователей сигналов четности (N количество разрядных входов информационного входа модуля, N 2S, S ≥ 2, K число разрядов в байте) и формирователь маски, причем информационный вход устройства соединен с информационным входом модуля формирования сигналов четности, выход которого соединен с информационным входом узла сдвига контрольных разрядов, выход которого является выходом устройства, вход знака устройства соединен с первым входом элемента И, второй вход которого соединен с первым выходом узла управления, второй и третий выходы которого соединены с входами соответственно первого и второго разрядов кода задания типа сдвига модуля формирования сигналов четности, вход блокировки которого соединен с четвертым выходом узла управления, входы первой группы которого соединены с входами младших разрядов кода задания величины сдвига устройства, а входы второй группы узла управления являются входами задания типа сдвига устройства, вход задания величины сдвига устройства соединен с информационным входом формирователя дополнительного кода, выходы старших разрядов которого подключены к входам задания величины сдвига узла сдвига контрольных разрядов, вход задания типа сдвига которого соединен с выходом формирователя кода маски, информационные входы которого соединены с входами старших разрядов кода задания величины сдвига устройства, управляющие входы формирователя кода маски подключены к входам соответствующих разрядов кода задания типа сдвига устройства, вход признака направления сдвига устройства соединен с управляющим входом формирователя дополнительного кода, выходы младших разрядов которого соединены с входами задания величины сдвига модуля формирования сигналов четности, входы контрольных разрядов которого являются входами контрольных разрядов устройства, в модуле формирования сигналов четности вход формирователя кода маски является входом задания величины сдвига модуля, информационный вход i-го разряда j-го формирователя сигнала четности (i 1, K 2, j 1, N / K) соединен с информационным входом [K (j 1) + i]-го разряда модуля, вход (j 1)-го контрольного разряда которого соединен с входом контрольного разряда j-го формирователя сигнала четности, вход маски которого соединен с первым выходом формирователя маски, выход (j 1)-го разряда модуля соединен с выходом сигнала четности j-го формирователя сигнала четности, вход типа сдвига первого разряда модуля соединен с входом блокировки первого формирователя сигнала четности, отличающееся тем, что модуль формирования сигнала четности содержит дополнительный формирователь сигнала четности, информационный вход p-го разряда которого, где p 1, K, соединен с информацинным входом (N K + 1 + p)-го разряда модуля, вход блокировки которого соединен с входом блокировки дополнительного формирователя сигнала четности, вход контрольного разряда которого соединен с входом N / K-го контрольного разряда модуля, вход задания типа сдвига второго разряда которого соединен с входом блокировки N / K-го формирователя сигнала четности, вход переноса q-го (q 1, (N / K) 2) формирователя сигнала четности соединен с выходом переноса (q + 1)-го формирователя сигнала четности, вход переноса (q + 1)-го формирователя сигнала четности, вход переноса (N / K 1)-го и N-го формирователя сигнала четности соединен с выходами переноса соответственно дополнительного и первого формирователя сигнала четности соединен с вторым выходом формирователя маски, первый информационный вход каждого j-го формирователя сигнала четности соединен с информационным входом K (j 1)-го разряда модуля, вход знака которого соединен с входом знака N /K-го формирователя сигнала четности и с выходом элемента И.

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Устройство для формирования сигналов четности при сдвигах двоичных кодов | 1989 |

|

SU1783527A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1995-10-10—Публикация

1992-05-18—Подача